### Multi-scale, Multi-physics Modeling and Simulation of Single Event Effects in Digital Electronics: from Particles to Systems

Jean-Luc Autran, Daniela Munteanu

### ► To cite this version:

Jean-Luc Autran, Daniela Munteanu. Multi-scale, Multi-physics Modeling and Simulation of Single Event Effects in Digital Electronics: from Particles to Systems. IEEE Transactions on Nuclear Science, 2024, 71 (1), pp.31-66. 10.1109/TNS.2023.3337288 . hal-04333942

### HAL Id: hal-04333942 https://amu.hal.science/hal-04333942v1

Submitted on 10 Dec 2023  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Multi-scale, Multi-physics Modeling and Simulation of Single Event Effects in Digital Electronics: from Particles to Systems

J.L. Autran and D. Munteanu

*Abstract*— This review paper aims to provide a survey of modeling and simulation of single-event effects (SEEs) in digital electronics at device, circuit and system levels. It primarily focuses on the specific multi-scale, multi-physics, multi-domain nature of SEEs and on the main underlying physical mechanisms that lead to the occurrence of single events in digital devices and circuits. This review addresses the different ways to model and simulate both in space and time this complex sequence of mechanisms from the particle-material interaction up to the electrical response of a given electronics device, circuit, or system. It highlights the specific features of each methodology, and discusses simulation requirements, code or model inputs and expected outputs.

*Index Terms*— Circuit simulation, compact models, device modeling and simulation, digital circuits, digital single-event transient, radiation effects, single-event effects, soft error rate, transport models, radiation transport codes.

#### I. INTRODUCTION

SINGLE event effects (SEEs) designate a set of multiphysics and multi-scale phenomena that take place in a

microelectronic device, component, subsystem, or system (digital or analog) impacted by a single energetic particle and that result in any measurable or observable change in its state, operation, or performance. SEEs were reported for the first time in the 1950s during nuclear weapon testing and observed in space electronics from the 60s [1-4]. Terrestrial cosmic-rays (atmospheric radiation) and traces of radioactive impurities (alpha-particle emitters) in circuit materials were identified later in the 70s-80s as the two major sources of SEEs at ground level [5-10]. In the 90s, the interaction of low-energy (thermal) cosmic-ray-induced neutrons with the <sup>10</sup>B isotope potentially present in device materials was also identified as another major source of SEEs [11].

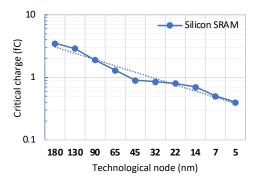

In recent decades, the growing significance of SEEs in the reliability of modern electronics can be attributed to the extreme miniaturization of complementary metal-oxide-semiconductor (CMOS) devices combined with the increase of the circuit integration (i.e., the number of transistors per unit area) [12,13,14]. As feature-size scales down, the per-bit crosssectional area exposed to an incoming ionizing particle decreases. This is accompanied by a reduction in the volume where energy is deposited by the traversing particle, and by an increase of the particle's region of influence within the affected

Manuscript received March 16th, 2023.

device, cell, or circuit [12]. The ongoing reduction of the critical charge as devices shrink [12,14,15,16], has made them increasingly susceptible to natural or artificial radiation in general and down to the most tenuous levels, as encountered for example at terrestrial ground level.

Alongside the experimental aspects, modeling and simulation have long been used for better understanding the effects of radiation on the operation of devices and circuits [17-22]. Because of its increasingly predictive capacity, which goes hand in hand with the power of computational tools and advances in physical modeling, simulation offers the possibility of reducing radiation experiments and of testing hypothetical devices or conditions, which are not feasible (or not easily measurable) by experiments. For the study of SEEs in future devices for which experimental investigation is still limited, numerical simulation is an ideal investigation tool for providing physical insights and predicting the operation of future devices expected at the end of the roadmap [13,21].

As CMOS technologies move down to the nanometer scale and circuits become more complex, it becomes necessary to adopt a truly multi-physics and multi-scale simulation approach to capture the essential physics of SEEs, from the particlematter interaction to the response of a digital circuit or system. This raises several challenges in the development of powerful simulation tools and in the management of interactions between simulation levels. In brief, multiscale simulations can be linked in two ways: i) by incorporating direct links between input/output flows of different simulation types, or ii) by transforming the results of a given simulation level into a simplified form and feeding them as input to another simulation level. A hierarchical structure of the interactions between simulation levels offers advantages in terms of efficiency, while also providing design insights [23].

This paper deals with this important issue of modeling and simulation of SEEs in digital electronics at device, circuit and system levels. The paper primarily addresses key topics related to single-event transients (SETs) and single-event upsets (SEUs) occurring in digital devices and circuits. An SET is a temporary and unintended voltage or current fluctuation that occurs when ionizing particles, such as cosmic rays or highenergy particles from nuclear reactions, interact with the

J.L. Autran, is with Aix-Marseille University and CNRS, IM2NP (UMR 7334), F-13397 Marseille, France and with University of Rennes and CNRS, IPR (UMR 6251), F-35042 Rennes, France (e-mail: <u>jean-luc.autran@univ-rennes.fr</u>). D. Munteanu is with Aix-Marseille University and CNRS, IM2NP (UMR 7334), F-13397 Marseille, France (e-mail: <u>daniela.munteanu@univ-</u>

amu.fr). This article was presented in part at Section IV of the Short-Course "Multi-Scale, Multi-Physics of Radiation Effects," in the 2022 IEEE Nuclear and Space Radiation Effects Conference (NSREC), Provo, UT, July 18, 2022.

semiconductor materials inside electronic devices [24,25]. These interactions can disrupt the normal operation of digital circuits, causing a momentary change in the logic state of a device/circuit or an operation interrupt. The other numerous effects induced by single events in electronics are only briefly mentioned at the beginning of the article to provide an overview of SEEs and to better contextualize the topics discussed here. The paper is organized as follows. Section II primarily focuses on the specific multi-scale, multi-physics, multi-domain nature of SEEs and on the main underlying physical mechanisms that lead to the occurrence of soft errors in digital circuits. In Section III, a meticulous review will address the different ways to model and simulate both in space and time this complex sequence of mechanisms from the particle-material interaction up to the electrical response of a given circuit. Section IV explores in detail the main approaches for the modeling and simulation of SEEs at device and circuit cell levels such as sensitive volume-based models, the so-called diffusioncollection method, the random-walk drift diffusion approach, and Technology Computer-Aided Design (TCAD) simulation. In section V we examine a few approaches of mixed-mode and circuit simulation used to investigate SEEs at circuit level. Section VI presents the modeling of the Soft Error Rate (SER) as well as different approaches of critical charge modeling in both memory circuits and in combinational logic. Finally, in section VII we briefly review modeling and simulation approaches of SEEs at the system-level.

#### II. UNDERSTANDING THE NATURE OF THE SEE PROBLEM

#### A. Definition and classification

We start by a general definition of a Single-Event Effect, followed by a classification of the different types of SEEs.

- A Single-Event Effect is initiated by the passage of a single energetic particle through the volume of an electronic device.

- The striking particle may be an elementary particle (proton, neutron, muon, electron, ...), or an ion (alpha particle, heavy ion).

- An SEE is created if the result of the interaction of the particle with the device or circuit interferes with its electrical operation, causing or not an observable functional error.

- An SEE can result in a reversible (non-permanent) or irreversible (permanent) change in device or circuit operation. In the first case, the error is recoverable and is qualified as a "soft error"; in the second case, the error is generally the result of an unrecoverable damage and one speaks about "hard error".

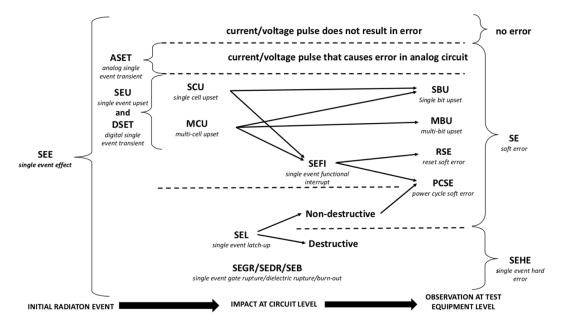

The recent revision of the JEDEC standard JESD89B [24] proposes a definition and a classification of the different types of SEEs, resulting from several years of discussion and effort to try to standardize this ensemble of technical terms. These are summarized in Fig. 1 and their extensive definitions, according to the JEDEC standard, are given below (all quotes in italics correspond to definitions directly taken from [24]). Soft errors (SE) include single-event transients (SET), single-event upsets (SEU), single-bit upsets (SBU), single-cell upsets (SCU),

multiple-bit upsets (MBU), multiple-cell upsets (MCU), singleevent transients (SET) that, if latched, become SEU [24]:

- Single-event upset (SEU): "A non-permanent error caused by a state change of a latch, flop, memory cell or other bistable element from the particle strike. The energetic strike can occur directly on the circuit element or propagate to that circuit (see SET)."

- Single-bit upset (SBU): "A SEU in which the observed error is a single logical or data bit."

- Single-cell upset (SCU): "A SEU where only one cell or logic element (latch, flip flop, etc.) is upset (compare to MCU)."

- Multiple-bit upset (MBU): "A single event that induces upset of multiple-cells where two or more of the upsets occur in the same logical word (or frame/column/sector, etc. for field-programmable gate arrays (FPGAs)). NOTE An MBU is a logical manifestation of a single event."

- Multiple-cell upset (MCU): "A single event that induces several cells (e.g., memory cells or flip-flops) in an integrated circuit (IC) to flip their state at one time." Single-event functional interrupt (SEFI): "A single event that causes the component to reset, lock-up, or otherwise malfunction in a detectable way, but does not result in permanent damage (i.e. hard error). Note that a SEFI is often associated with an SBU/MBU in a control bit or register, whereas a SEL is caused by the turn-on of a parasitic thyristor. Many SEFI events can be cleared with a component reset operation. In cases where resetting some configuration registers requires a complete power cycle of the device, it can be difficult to distinguish between a SEFI and a SEL (see below). A SEFI event does not necessarily result in an extended increase in operational current like a high current SEL."

- Single-event transient (SET): "A time dependent radiation induced spurious current or voltage signal on a circuit node. A digital SET (DSET) occurs when an SET in a combinational logic gate (along data or control paths) propagates and is latched to create an error in the output of a sequential element. An analog SET (ASET) is a spurious signal in an analog circuit (e.g., a spurious signal on an input-output (IO) pin, etc.) that causes an erroneous output."

Single Event Hard errors (SEHE) include single event gate oxide ruptures (SEGR), single event dielectric ruptures (SEDR), single event burnouts (SEB) and destructive single event latchups (SEL) [24]:

- Single-event gate rupture (SEGR): "An event in which a single energetic particle strike results in a breakdown and subsequent conducting path through the gate oxide of a metal-oxide-semiconductor (MOS) transistor."

- Single-event dielectric rupture (SEDR): "An event in which conducting path is created in a dielectric material from a single energetic particle strike."

- Single-event burnout (SEB): "An event in which a single

Fig. 1. Diagram of terms used to describe single event effects. (After JEDEC Standard JESD89B [24], © JEDEC 2021.)

energetic particle strike induces a localized highcurrent state in a device, resulting in catastrophic failure."

Single-event latchup (SEL): "An abnormal current state in a circuit caused by the passage of a single energetic particle inducing a parasitic thyristor to turn on and remain in a fixed state regardless of inputs, until the device is power cycled. Some SEL events result in a measurable current increase (e.g., latch-up of an IO circuit). Some SEL events may result in a difficult to detect increase in current (micro-SEL) compared to the quiescent current of the entire component (e.g., latchup of memory cells within a common well). A high current SEL may cause permanent damage to the component and result in a hard error. Micro-SEL events are typically non-destructive due to the low current draw and can be cleared by power cycling."

As explained in the introduction, this paper does not aim to cover the vast and exhaustive domain of all types of SEEs, but mainly focuses on the most important issues concerning the modeling and simulation of SETs and SEUs induced by single events in digital electronics. For a detailed presentation of other SEEs and radiation effects in electronics (total-ionizing dose (TID), displacement damage) we invite the reader to consult ref. [13,26,27,28] and the references cited therein.

## *B.* Main processes that lead to the production of an SEE in a circuit/system (summary)

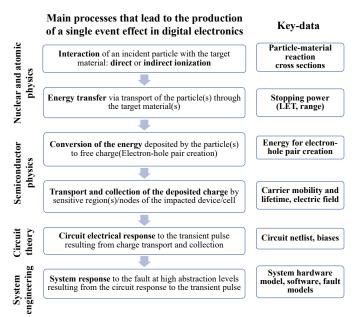

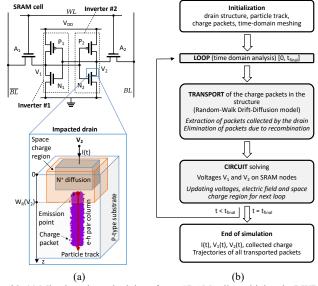

Before surveying the main modeling and simulation approaches of SEEs in the next sections and going into the substance of several underlying mechanisms for creating SEEs, we summarize in the text that follows and in Fig. 2 the main processes that lead to the production of an SEE in a circuit. We note that the physical processes occur on different time scales and are non-interacting.

### *1)* Interaction of the incoming particle with the target material

An SEE is always initiated by the interaction of an incident particle with the target material. This interaction necessarily involves a transfer of energy from the particle to the medium via electromagnetic or nuclear processes. As a result of such processes, a fraction or the totality of the incoming particle energy is released inside the medium [29]. At this level, we can identify two primary interaction mechanisms for the typical particles that could potentially cause SEEs in electronics: direct ionization and indirect ionization of matter [30].

Direct ionization typically concerns electrons, muons, low energy protons (E < 1 MeV), alpha particles and heavy ions (with atomic number Z > 1). These mainly interact with the electrons and nuclei of the target material [30]. In the initial phase of the passage of such a charged particle in matter, collisions with atomic electrons are the principal mode of energy loss in a very wide range of energies of the incident particle. These interactions gradually slow down the particle. In the final phase, the particle slowing and stopping are due to collisions with nuclei. The main mechanism that leads to energy loss and slowing down of the charged particle is then the ionization phenomenon. Ionization induces the generation of a large number of excited energetic electrons (delta-rays) which generally have sufficient energy to ionize other atoms. An electronic cascade is activated in which the number of free electrons continues to increase while their average energy decreases. During the passage of the ionizing particle, a highly ionized channel of very small diameter (typically a few tens of nm) develops around the track of the particle. Very rapidly, the excited electrons in the plasma lose their kinetic energy through a series of elastic collisions with electrons of the lattice to finally reach an energy close to the binding energy of the material. Simultaneously, the ionized atoms, positively

Fig. 2. Main processes that lead to the production of SEEs in digital electronics and key-data considered for their modeling and simulation, from the particle interaction to the system level.

charged, rearrange their electrons resulting in creation of holes in the valence band. A high-density column of electron-hole pairs is then formed in a narrow region around the particle track.

Indirect ionization primally concerns neutrons, but also highenergy protons and heavy ions. These particles can interact with atomic nuclei following two major mechanisms, i.e., scattering (elastic and inelastic interactions) and capture (inelastic interactions or nuclear reactions). For elastic interactions, the total kinetic energy is conserved, and the incoming particle is deflected from its path as it transfers some of its energy to the target atom. In the case of inelastic scattering, the target nucleus rearranges its internal state to one of higher energy, and the total kinetic energy is not conserved. But in both cases, the nature of the recoil nucleus is left unmodified. Instead of being scattered, an incident neutron, proton or ion may be absorbed or captured by a target material nucleus. After it has absorbed the impinging particle, the nucleus can get rid of excess protons or neutrons, it can undergo de-excitation by emitting a  $\gamma$ -ray, or it may even split into medium-sized fragments when the energies are high enough to trigger nuclear fission (a threshold energy exists for each such reaction). The produced fragments extend from proton or neutron to the nucleus of the target atom; they can in their turn directly ionize matter like any charged particle (previous case). It is important to note that nuclear reactions produced by high-energy ions are rare compared to ion-electron interactions, yet they hold significance in specific cases as explained in [31,32,33]. These nuclear reactions yield one or multiple secondary ionizing particles with significantly different electronic stopping power (see below) compared to the primary incident particle. The relevance of nuclear reactions in error rate estimations strongly depends on the critical charge of the circuit or device under consideration [31,32,33].

The number of nuclear interactions per type of interaction can be evaluated from cross section data of the atom nuclei present in the target material. For monoenergetic neutrons or protons arriving perpendicularly on a thin sheet of natural material, the number of nuclear interactions occurring in the target is given by

$$N_X(E) = \sum_i f_i \sigma_{X,i}(E) imes 10^{-24} imes NV imes t imes M$$

(1)

where X is the type of the considered interactions (elastic, inelastic, inelastic), E is the energy of the incident neutrons or protons,  $\sigma_{X,i}(E)$  is the value at energy E of the type X reaction cross section for isotope i (expressed in barn), f<sub>i</sub> is the fraction of isotope i in the target isotopic composition, t is the target thickness (expressed in cm), NV is the number of atoms per cubic centimeter and M is the number of incident monoenergetic neutrons or protons impacting the target.

### *2) Energy transfer from the ionizing particle(s) to the target material*

For both direct or indirect ionization, two key-quantities can be introduced to characterize the energy transfer from an ionizing particle (i.e., an incident ionizing particle penetrating the target material or produced as a secondary particle in an interaction event involving a primary incoming particle and a target atom nucleus) to the target material: the stopping power and the range. We recall below the definitions of these two quantities.

<u>Stopping power</u>: The stopping power is the amount of energy per unit length lost by a particle in the matter. It is usually expressed in keV/ $\mu$ m or MeV/ $\mu$ m. The total stopping power is decomposed into two components: i) the electronic stopping power, corresponding to the loss of energy of the particle due to collisions with atomic electrons of the target material; ii) the nuclear stopping power, corresponding to the loss of energy of the particle due to collisions with the nuclei of atoms of the target material. The electronic stopping power is also called Linear Energy Transfer (LET). The LET thus characterizes the creation of electron-hole pairs by ionization of the target material, while nuclear stopping power describes the atomic displacement of the target material [30]. The LET is expressed as a function of the energy particle E as

$$LET = -\frac{\mathrm{d}E}{\mathrm{d}x} \,. \tag{2}$$

For a nonrelativistic charged particle with speed v, charge z (in multiples of the electron charge) traveling into a target of electron density n and mean excitation potential I, the LET can be analytically evaluated from the reduced form of the Bethe-Bloch formula [34]

$$LET = \frac{4\pi n z^2}{m_e v^2} \cdot \left(\frac{e^2}{4\pi\epsilon_0}\right)^2 \cdot \ln\left(\frac{2m_e v^2}{I}\right)$$

(3)

where  $\varepsilon_0$  is the vacuum permittivity, e and m<sub>e</sub> are the electron charge and rest mass respectively. Equation (3) shows that LET increases with decreasing particle velocity until it reaches a maximum value when the particle is close to stopping. A weighted LET is generally used, defined as the ratio between the LET and the density  $\rho$  of the target material

$$LET = -\frac{1}{\rho} \frac{\mathrm{d}E}{\mathrm{d}x} \,. \tag{4}$$

The unit of this weighted LET is  $MeV/(mg/cm^2)$ .

<u>Range</u>: The range R is the distance traveled by an ionizing particle of initial kinetic energy  $E_0$  before it comes to rest in the stopping material; it is calculated from the LET of the particle as

$$R(E_0) = \int_{E_0}^0 -\frac{1}{\frac{dE}{dx}} dE = \int_0^{E_0} \frac{1}{LET} dE$$

(5)

#### 3) Conversion of the deposited energy to an electrical charge

The conversion of the energy deposited by an ionizing particle to free charge in a given target material can be evaluated from its mean value of energy for electron-hole pair creation  $E_{e,h}$ , a material-dependent constant usually experimentally measured or determined from band structure and quantum transport simulation (see for example recent work performed for bulk silicon and germanium [35]). When experimental or accurate simulated values are not available for a given semiconductor material,  $E_{e,h}$  can be estimated from Klein's phenomenological model that establishes a linear relationship between the bandgap energy and  $E_{e,h}$  in semiconductor materials [36]

$$E_{e,h}(eV) \simeq \frac{14}{5} E_g(eV) + 0.66$$

(6)

The well-known value for bulk silicon is  $E_{e,h} = 3.6 \text{ eV}$  at 300 K. From (6),  $E_{e,h}$  is expected to vary from ~1.1 eV for InSb ( $E_g = 0.17 \text{ eV}$  at 300 K) to ~12 eV for diamond ( $E_g = 5.47 \text{ eV}$  at 300 K).

For a given target semiconductor material characterized by its density  $\rho$  and its average energy for electron-hole pair creation  $E_{e,h}$  and considering a particle with a given LET value, it is possible to calculate the charge  $Q_{dep}$  deposited by this particle along a path of length  $\ell$  in the target material from the following expression

$$Q_{dep} = \frac{16.02 \times \rho}{E_{e,h}} \int_{path} LET(\ell) d\ell$$

(7)

In (7),  $Q_{dep}$  is given in fC if  $\rho$  is expressed in g/cm<sup>3</sup>,  $E_{e,h}$ , is in eV, LET is in MeV/(mg/cm<sup>2</sup>) and  $\ell$  is in  $\mu$ m.

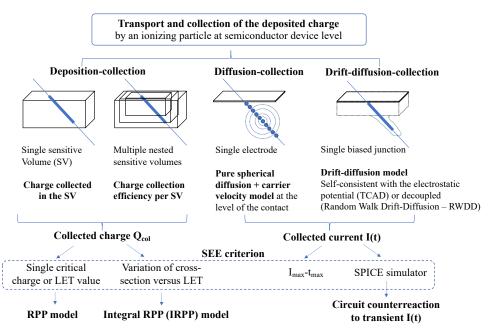

## *4) Transport and collection of the deposited charge in the region of the impacted circuit*

Once a very dense column of electron-hole pairs has been created almost instantaneously (the practically instantaneous delivery of the ion energy to the electronic subsystem of a solid, lasting from 0.1 to  $10^3$  fs, creates a large number of electron-hole pairs per unit track length [37]) along the track of the ionizing particle, this deposited charge rapidly evolves under the action of different mechanisms that control the charge-carrier dynamics, e.g., its transport in the semiconductor material and its possible collection by a circuit node. It must be noted that these transport and collection processes of

importance occur in the active semiconductor region of the device.

- <u>Charge transport</u>: the development of the column of electron-hole pairs starts in the femto-second range after its creation following three mechanisms that contribute to the reduction of the density of excess carriers at the heart of the track: ambipolar diffusion, carrier recombination (Shockley-Read-Hall and Auger recombination) and separation between holes and electrons under the combined effect of diffusion and drift induced by local electrical fields [37]. Charges released from this plasma column and having escaped the initial massive recombination, are quickly transported further into the semiconductor by diffusion and also by additional drift in regions where a non-zero electric field exists.

- <u>Charge collection</u>: released charges in the "vicinity" of a circuit node at front-end-of-line (FEOL) level, e.g., near or across a reverse-biased p-n junction or a biased diffused area contact, can be collected via drift-diffusion by such a structure and be extracted from the semiconductor material to the circuit. This charge collection process is crucial in the formation of a parasitic transient current that is injected on the impacted node. In section III we will look in detail at the physics, modeling, and simulation of this key-step in the formation of SEEs.

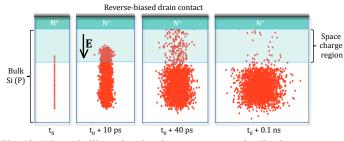

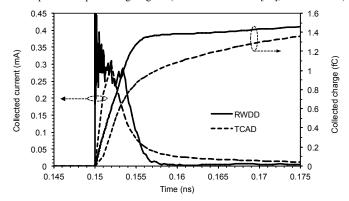

Fig. 3 illustrates the formation of a transient current pulse (shown in Fig 3(a)) resulting from the charge transport and collection in the case of a neutron-silicon nuclear reaction. This reaction occurs in the volume of the space charge region (SCR) of a reverse-biased nano-transistor drain junction and produces four ionizing secondaries. The figure is the result of a simplified particle Monte Carlo simulation in which the radiation-induced minority carriers (here the electrons grouped per packets of multiple charges) are represented by red points. After the production of secondaries and the energy deposition along their tracks (Fig. 3(b)), the widening of the charge clouds reflects the diffusion of the carriers, their displacement towards the top surface, and their drift in the electrical field (here vertical) of the junction (Figs. 3(c), (d), (e)). Carriers are finally extracted from the top surface (electrode) where they contribute to the formation of the transient current that is injected into the external circuit.

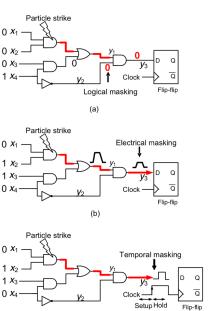

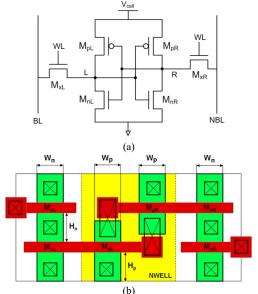

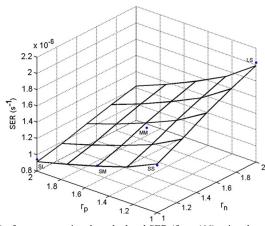

#### 5) Circuit electrical response

The current transient pulse resulting from the radiationinduced charge collection and extraction at the level of a circuit node may induce disturbances in the circuit to which the impacted node is connected. The induced effects at circuit level are different according to the intensity of the current transient, as well as the number of impacted circuit nodes. If the transient peak is sufficiently important in terms of current magnitude, it can induce a hard error (permanent damage) on gate insulators (gate rupture, SEGR) or provoke a short-circuit loop between different semiconductor regions (latchup, burnout). In other cases, the transient current may generally induce a soft error which can be manifested by the change of logic state of one or

Fig. 3. Particle random-walk drift-diffusion (RWDD) numerical simulation (described in section IV.C) of the transient current (a) extracted from the junction contact (corresponding to the top surface) in a reverse-biased junction caused by the interaction of a 1.17 GeV neutron with a silicon atom (3 protons and a  $^{22}$ Na ion produced). Illustration of the charge generation (b) and the transport and collection phases 2 (c), 3 (d) and 4 (e) indicated on the transient plot. Dimensions on the three axes are in nanometers.

more memory points (upset) or even a functional interrupt. In the following sections, we will examine in detail the circuit electrical response to such radiation-induced pulses, and we will show that the circuit is not necessary passive during this phase of charge collection. On the contrary, it can play an important role via the counter-reaction it develops on the impacted node potential following the collection of charges on it.

#### 6) System response

When a transient event occurs at the level of a circuit, hardware component of a larger electronic system, it can trigger various consequences that reverberate at the system level. One prominent consequence is data corruption. In digital systems, the sudden change in the state of a register or memory bit due to an SEU for example can lead to errors in calculations, memory storage or communication protocols. This corruption compromises the integrity of critical information and can have cascading effects on subsequent operations. In addition to data corruption, the functionality of the affected circuit may be disrupted. This disruption may be transient, causing temporary malfunctions, or it may cause permanent changes in the logic of the circuit, resulting in unexpected behavior, system crashes or erroneous responses. In some cases, a single event can even trigger a system reset, resulting in temporary downtime, potential loss of data and disruption to overall system operation. Single events can also cause communication errors. Corruption of data as it is transmitted between different components of the system can lead to misinterpretation, protocol violations or communication failures. Such errors can undermine the synchronization of subsystems, essential for the proper functioning of complex systems. SEEs at the system level can similarly alter the control flow within software. An eventinduced change in the logic of a program can lead to unintended branches or loops that were not intended by the original design. Consequently, the system might exhibit behavior that deviates from the expected and intended operational path, potentially causing software crashes or erroneous outcomes. There is also the risk of permanent damage caused by single events. In extreme cases, the circuit can be irreparably harmed, rendering the system inoperable. Finally, SEEs might not always lead to immediate visible effects. Some events could introduce latent effects that manifest themselves later, making the diagnosis of

#### system-level issues challenging.

### *C. Multi-physics, multi-scale and multi-domain nature of single events*

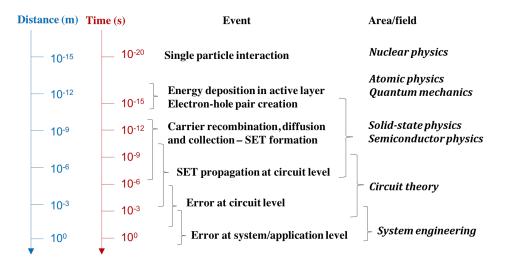

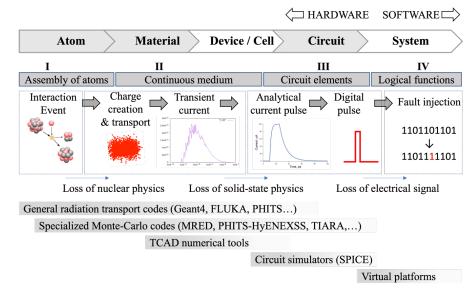

The previous subsections summarized the different processes that lead to the production of an SEE in a digital circuit or a system. It showed that single-event effects are inherently multiphysics, multi-scale and multi-domain, as indicated in the following and illustrated in Figs. 4 and 5.

- <u>Multi-physics</u>: SEEs are first initiated by particle-matter interactions, fields of nuclear and atomic physics. Then, they involve the creation of charges and their transport in materials, mainly semiconductors, governed by solid-state physics and quantum-mechanics. The resulting transient current or voltage pulse created in the interconnected network of elementary structures that constitute the circuit itself, in the sense of the electronics function, obeys the fundamental laws of electrokinetics and circuit theory. Finally, the potentially disturbed circuit response can affect the system of which it is a part, governed by the general theory of systems.

- <u>Multi-scale</u>: SEEs are initiated by a single particle interaction at atomic-level in the bulk of circuit materials and can lead to a functional error at circuit or system-level. Between these two events, there are approximately 15 orders of magnitudes on the distance scale and approximately 20 orders of magnitude on the time scale, as illustrated in Fig. 4. In addition to the multi-physics nature of SEEs, these changes of scale both in time and in distance explain why is extremely difficult to simulate SEEs with a single tool from the beginning to the end of this sequence of events.

- <u>Multi-domain</u>: SEE, or more accurately the precursor event to an SEE, is first an atomic event before being transformed into an electrical signal then into an analog or logical event. Depending on when it is considered, it therefore belongs to different fields or domains: the domain of materials, then of devices, then of circuits and finally of systems. To each domain corresponds a particular expression of this SEE precursor: secondary particles of a nuclear interaction, bundle of electron-hole pairs, transient current, analog signal, logic pulse, value encoded in a memory, etc. When passing from one domain to the next, as defined in the SEE chronology formulation, the physics of the previous domain appears to be lost in

Fig. 4. Typical space and time scales for single events effects, from the single particle interaction to the detection of an error at system level.

Fig. 5. The multi-physics, multi-scale, and multi-domain nature of SEE. The main simulation tools and platforms are also indicated.

the new domain; this can be overcome to a certain extent, as will be discussed in several places later in this paper. For example, when the secondary particle energy is converted into e-h pairs, the nuclear physics is no longer appropriate for describing the formation of the SEE and any information relating to the nuclear event is moreover lost. This vision is true until the final expression of the SEE at the system or application level, at the end of the chain.

Fig. 5 illustrates in a slightly different way the multi-physics and multi-scale nature of SEE, emphasizing their multi-domain character. Four domains can be defined in which an SEE precursor (or initial event) will have different expressions: at the atomic level (assembly of atoms), at the material level (continuous media), at the circuit level (circuit elements) and at the system level (logical functions). The boundary is sometimes difficult to define, hence the notion of assembly of atoms to describe the domain in which nuclear interactions and energy deposition of secondary particles by ionization take place. The same applies to the notion of continuous medium to describe semiconductor or insulating materials, whether they are considered as bulk materials or part of a component.

When considering the chronological formulation of SEEs (from atoms to systems), each change of domain is marked by a loss of information concerning the mechanism that gave rise to the precursor signal of the SEE. The precursor of an SEE is first a nuclear interaction, then a cloud of charges, then an analog electrical signal, then a digital signal and finally a binary value. Considering the electrical signature of an SEE no longer allows us to go back to the interaction that gave rise to it; likewise, considering a binary change does not make it possible to go back to the original electrical signal. This loss of information concerning the physical mechanisms from the underlying domain to the next is an important element in understanding that an SEE can be simulated at different levels and with different physical manifestations. This point will be discussed in detail in III.A. In certain cases, results from a tool that simulates a level farther along in the chronological formulation of an SEE can be used to define inputs to a tool that appears earlier in the chronological view. While at first this seems counter intuitive, the rationale is in fact simple: if the outputs from a higher-level tool can be simplified such that they can be used to define inputs to a lower-level tool, then one gives up information from the high-level tool. This approach allows one to by-pass higher-level tools in the full analysis of an SEE, reducing simulation time significantly. This point is briefly described in Sections I.V.A and V.D.

#### III. TAXONOMY OF MODELING AND SIMULATION APPROACHES

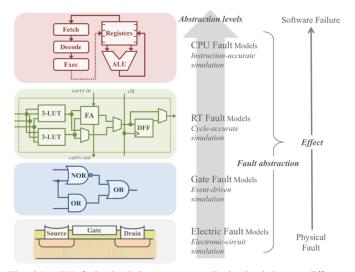

In this section, we examine the different types of methodologies of modeling and simulation of SEEs, as a function of the "simulation level" envisaged to perform a given study. We propose a classification of simulation tools in five main categories. We also examine the main modeling and simulation approaches for the transport and collection of the deposited charge induced by an ionizing radiation at device or circuit levels that allow us to distinguish methods using a collection charge concept with respect to methods considering the computation of a collected current.

### *A. Types of methodologies: what simulation code, input, and output?*

We start again from Fig. 5 which illustrates the domains covered by the main simulation tools and platforms used to simulate SEE in electronics (the list is far from exhaustive). This highlights that none of them can cover the entire chain, from particles to systems. We distinguish five categories of codes, briefly described in the following and in Table I:

(1) General radiation transport codes like Geant4 [38,39], FLUKA [40,41], MCNP [42,43] or PHITS [44,45]: these codes are general-purpose, continuous-energy, generalized-geometry, time-dependent and Monte Carlo radiation transport codes designed to track many particle types over broad ranges of energies. These codes have many applications in high energy experimental physics and engineering, shielding, detector and telescope design, cosmic ray studies, dosimetry, medical physics, and radiobiology. In the context of SEE studies, these codes can be used to develop and compile complete applications from toolkits including source files and libraries. Alternatively, they can be used to perform various calculations from precompiled versions that read data input files.

(2) <u>Specialized Monte Carlo radiation transport codes</u> <u>applied to SEEs</u> like SEMM/SEMM-2 [46,47,48], MRED [31,49,50,51], PHITS-HyENEXSS [52], TIARA [53,54,55], MUSCA-SEP3 [56,57], IRT [58], MC-ORACLE [59,60] and other codes (see references in [51]) based on nuclear and radiation transport physics : these Monte Carlo-based radiation transport tools are able to simulate a variety of effects that result from energy transferred to a semiconductor material by a single particle event. The breadth and depth of the application of each specialized code solving single event effects problems varies dramatically, from almost non-existent to a high level of detail, as illustrated in [51].

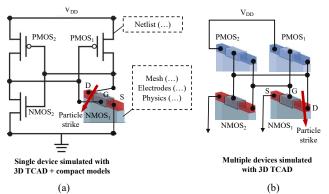

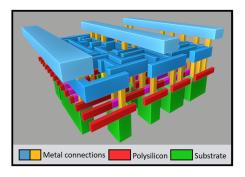

(3) <u>TCAD numerical simulation platforms</u> like the Synopsys<sup>®</sup> [61], Silvaco<sup>®</sup> [62] or Cogenda<sup>®</sup> [63] suites: TCAD code suites are used to model and numerically simulate

semiconductor fabrication and semiconductor device operation. Included are the modeling of process steps (such as diffusion and ion implantation), and modeling of the behavior of the electrical devices based on fundamental semiconductor physics and numerical solving of electrostatics and continuity equations for different carrier transport models (drift-diffusion, hydrodynamics, quantum transport,...), also taking into consideration radiation effects and transport (see section IV.D). Coupled with a circuit simulator, TCAD tools are also able to simulate the impact of radiation at circuit-level in mixed-mode approach (see section V).

(4) Circuit simulators: they include analog simulators, digital simulators, and dedicated codes for mixed-signal analog/digital circuits. The most popular is SPICE (Simulator Program with Integrated Circuit Emphasis) which is certainly the most used electronics circuit simulator. SPICE refers to a wide variety of open-source (Ngspice [64]) and commercial circuit simulation programs (PSpice<sup>®</sup> [65], Eldo<sup>®</sup> [66]) offering extended capabilities via the integration of optional analog, radiofrequency (RF), mixed-signals or digital circuit simulation modules. Analog circuits embedding digital content can thus be simulated. More generally speaking, SPICE also refers to a class of simulation approaches based on the conversion of a text netlist of electrical elements such as resistors, capacitors, diodes, transistors and voltage/current sources and their connections to equations to be numerically solved. At this circuit level, SEEs can be modeled under the form of current or voltage pulses produced by a parametrized or arbitrary source inserted in the netlist and emulating the impact of a ionizing particle on a particular circuit node.

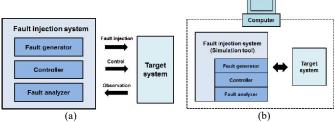

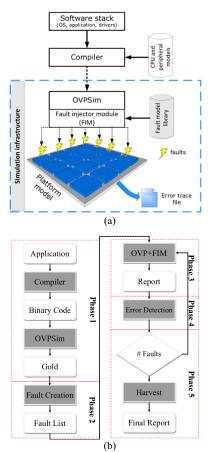

(5) System simulators and virtual platforms: at complex digital circuit, system-on-chip or system levels, the modeling and simulation of SEEs profoundly change in nature. SEE signals become logical (binary) information and are introduced during a simulation run via fault injection (FI) techniques. Their impact can be explored at different abstraction levels (gatelevel, cycle-level, transaction-level) using a wide variety of dedicated tools [67]. Full-system simulators or virtual platforms, such as OVPsim [68] or gem5 [69], are used to explore the vulnerability of complete systems to SEEs: they must include not only the modeling of the full hardware system (i.e., processor, memory, periphericals,...) but also the modeling of the full software system (the user application and the full operating system). The soft error vulnerability of a complete system can be analyzed from the exhaustive characterization of the execution errors monitored during a simulation.

Table I summarizes the simulation level, typical simulation inputs and outputs for the different categories of codes defined in Fig. 5 and in the text above. We will examine in the following sections some specificities of these different simulation approaches, firstly focusing on the physics of the charge transport and collection at semiconductor level, an essential step for the creation of transient signals which are at the origin of SEEs at device and circuit levels.

| Type of codes                                                                 | Simulation<br>level      | Typical simulation inputs                                                                                                                                         | Radiation input<br>(or signal emulating radiation)                              | Typical simulation outputs                                                               |

|-------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| General radiation<br>transport codes                                          | A 4 4                    | Simplified three-<br>dimensional (3D) circuit                                                                                                                     | Primary particles<br>Sources of particles (or nuclear<br>interaction databases) | Secondaries<br>Energy deposited in sensitive volumes                                     |

| Specialized Monte<br>Carlo code as applied<br>to SEEs                         | Atom to small<br>circuit | architecture<br>Sensitive volumes                                                                                                                                 |                                                                                 | Secondaries<br>Energy in sensitive volumes and/or<br>collected charge<br>Soft error rate |

| TCAD                                                                          | Material to cell         | Realistic device/circuit 3D<br>architectures       Radiation-induced generation rate         (possible link with process)       Radiation-induced generation rate |                                                                                 | Device transient response<br>Carrier and potential distributions                         |

| Cell circuit<br>simulation codes                                              | Material to cell         | Transistor compact model                                                                                                                                          | Numerical or analytical SETs                                                    | Cell transient response<br>(time domain analysis)                                        |

| Circuit<br>simulators                                                         | Device to circuit        | Circuit netlist<br>Device library                                                                                                                                 | Analytical SETs<br>Logical SETs                                                 | Soft error rate                                                                          |

| Hardware Description<br>Language (HDL)<br>simulators and virtual<br>platforms | Circuit to<br>system     | Circuit design<br>Application code                                                                                                                                | Logical faults                                                                  | Soft error vulnerability<br>Execution errors                                             |

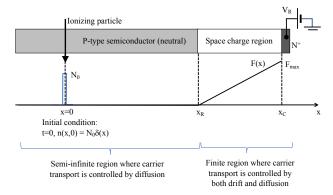

V<sub>R</sub> N<sup>+</sup> diffusion (N<sub>D</sub>) V<sub>Z</sub> W<sub>SCR</sub> Space charge region Funneling Funneling Radiation-induced free carriers (e-h) Ionizing particle

Fig. 6. Schematic illustration of the passage of an ionizing particle crossing the space charge region (SCR) of a reverse-biased p-n junction and stopping in the semiconductor region.

# *B. Physics of the charge transport and collection (collected charge and current)*

One of the most complex and central tasks in modeling and simulation of SEE is to correctly describe the interaction of an incoming particle with the sensitive zone(s) of a circuit and to determine the resulting transient electrical response susceptible to subsequently induce an SEE at circuit level. We examine in this paragraph the underlying physics that controls the charge transport and collection at the level of an elementary device, a reverse-biased n<sup>+</sup>-p junction integrated on bulk semiconductor material (silicon by default). We take as a starting point (t<sub>0</sub>) the moment immediately after the passage of the particle when the radiation-induced charge is just deposited in the form of a dense track of electron-hole pairs, as schematically illustrated in Fig. 6. The device of interest is defined by its geometry, type of materials, doping concentrations, and so on. Carrier transport and potential dynamics induced by the passage of the particle

in the semiconductor domain can be resolved in time from the self-consistent solving (coupling) of a set of three fundamental equations:

1) the <u>Poisson equation</u> that addresses the electrostatic problem. Solving this equation amounts to finding the electric potential  $\phi$  (V) for a given charge density distribution  $\rho$  (C.m<sup>-3</sup>)

$$\nabla\left(\epsilon\overrightarrow{\nabla\phi}\right) = -\rho = -q\left[N_D^+ - N_A^- + p - n\right] \tag{8}$$

where  $\varepsilon$  is the material-dependent permittivity (F.m<sup>-1</sup>), q is the absolute value of the electron charge, N<sub>D</sub><sup>+</sup> and N<sub>A</sub><sup>-</sup> are the doping ionized atom concentrations (m<sup>-3</sup>) for donor and acceptor impurities, respectively, n and p are the electron and hole densities (m<sup>-3</sup>), respectively.

2) the <u>continuity equations</u> that guarantee the continuity of electron and hole current densities  $J_n$  and  $J_p$  (A.m<sup>-2</sup>), respectively

$$\nabla \vec{J}_n = q(G - R) + q \frac{\partial n}{\partial t} \tag{9}$$

$$\nabla \vec{J}_p = -q(G-R) - q\frac{\partial p}{\partial t} \tag{10}$$

where G and R are the generation and recombination rates, respectively.

The electron and hole densities are calculated using the Fermi-Dirac statistics or using the Maxwell-Boltzmann approximation in case of non-degenerate doped semiconductors. In addition, to solve (9) and (10), a transport model must be chosen to express the current densities  $J_n$  and  $J_p$ . In the following, the classical drift-diffusion (DD) model will be used as the transport model. This assumes that the carrier energy is constantly in balance with the electric field, so that the transport only depends on the electric field. In the DD model,

the carrier transport is mainly due to electrostatic potential gradients and/or to carrier concentration gradients. The current densities of electrons and holes are then usually modeled as follows

$$\vec{J}_n = -q\mu_n n \vec{\nabla} \phi + q D_n \vec{\nabla} n \tag{11}$$

$$\vec{J}_p = q\mu_p p \vec{\nabla} \phi - q D_p \vec{\nabla} p \tag{12}$$

where  $\mu_n$  ( $\mu_p$ ) is the electron mobility (respectively holes),  $D_n$  ( $D_p$ ) is the thermal diffusion coefficient of electrons (respectively of holes), and  $\phi$  is the electric potential, solution of (8).  $D_{n,p}$  and  $\mu_{n,p}$  depend on the material and electric field and are connected by the Einstein relation  $D_{n,p} = (kT_L/q) \times \mu_{n,p}$  where  $T_L$  is the lattice temperature. In (11) and (12), current densities are therefore given by the sum of the conduction or drift component (the first term of the right side of equations) and the diffusion component (the second term).

In (8)-(12), the quantities n and p include not only the free carrier concentrations at equilibrium given by the band bending of the semiconductor, but also the excess carrier densities produced during the passage of the ionizing particle in the device. In other words, these radiation-induced electrons and holes are in excess with respect to the charge carriers available at thermal equilibrium. It is evident that the presence (along the particle track at  $t_0$ ) and the evolution (due to diffusion, recombination, and drift in the space charge region (SCR)) of excess carriers locally modify the electrostatic potential and thus complexifies the carrier dynamics and the transient device response.

One of the most important electrostatic manifestations of excess carriers is the drastic distortion of the electric field in the border of the SCR when the particle passes through this area, known as the funnel effect. After the particle penetration, the electric field, which was originally limited to the SCR, extends far down into the bulk semiconductor along the length of the particle track and can literally "funnel" many carriers into the struck junction, further enhancing charge collection. After a few nanoseconds, the field recovers to its position in the normal depletion layer, and, if the track is long enough, a residue of carriers is left to be transported by diffusion. The extent of this funneling is a function of substrate doping concentration, bias voltage, and the particle energy. It is a clear manifestation of the self-consistent character of the problem posed by the solving of the Poisson and continuity equations in the presence of an ionizing particle penetration.

Solving self-consistently the set of equations (8)-(12) in the three spatial dimensions and in a time domain including the passage of the ionizing particle up to the return to equilibrium is thus a very complicated process that only becomes tractable when using full numerical simulation performed on a meshed structure in which each node has specific associated properties, such as type of material, doping concentration, electrostatic potential, quasi-Fermi levels, etc. This meshing is used for solving discretized forms of (8)-(12) with given boundary conditions. In practice, only TCAD tools or some dedicated codes are capable of performing such fully numerical calculations (see section IV).

To render this problem easier to solve in the context of <u>SEE</u> prediction at circuit level, many simplifying assumptions must be introduced. These simplifications relate to the two aspects of the problem: the electrostatics and the transport of charges.

- The first is to decouple the Poisson equation from the continuity equations. In other words, the electrostatic potential at equilibrium (before the particle struck) is conserved throughout. The continuity equations are then solved considering an electric field fixed at the equilibrium of the structure, i.e., equal to zero in the semiconductor bulk and given by the p-n junction theory inside the space charge region of the collecting junction. Consequently, electron and hole density currents are pure diffusion currents throughout the simulation domain, to which a drift component must be added only inside the SCR. Two time-dependent models can be derived from this simplified schema: the diffusion-collection model and the drift-diffusion collection model, detailed in sections IV.B and IV.C. These approaches allow a collected current to be computed, catch the dynamics of the event, and facilitate the consideration of the counter reaction of the circuit in the case of mixed-mode simulation (section V).

- In addition to the previous simplification, the way in which the sensitive node collects the minority carriers resulting from the radiation can be greatly simplified by considering that only the carriers generated in a certain socalled sensitive volume around the node will surely be collected. Here, diffusion and drift of excess carriers occur in an "invisible way", their action and efficiency are included in the geometrical parameters of the sensitive volume. The computation of the charge transport is no longer meaningful, and the time variable disappears from the calculation that reduces to a pure geometrical problem. Different models can be derived from this approach, they are described in section IV.A.

These simplifying assumptions lead to less accurate simulation results, but simplified implementation and faster simulation times. Depending on the level of simplification considered, the computation effort and accuracy will be obviously very different. From the considerations highlighted above, Fig. 7 proposes a classification of the main modelingsimulation approaches for the transport and collection of the deposited charge by an ionizing radiation at semiconductor device level, detailed in the following.

#### IV. ANALYTICAL, COMPACT, AND FULL NUMERICAL METHODS AT DEVICE/CELL LEVEL

In this section, we examine in detail the main modeling and simulation approaches developed in the last decades by several research groups and authors concerning SEE at device and circuit cell levels. They include some popular sensitive volume-based models, the so-called diffusion-collection method, the random-walk drift diffusion approach and TCAD simulation.

Fig. 7. Classification of the main modeling-simulation approaches for the transport and collection of the deposited charge induced by an ionizing radiation at semiconductor device level.

#### A. Sensitive volume-based models

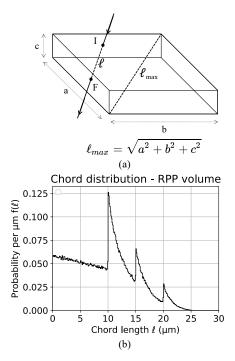

<u>RPP model</u>: A sensitive volume (SV) is defined as "*a region in space in which energy deposition from ionizing particle can affect the operation of a device. For SEE, the volume is often associated with the depletion region of a particular circuit node" [70]. This SV, also called "charge collection volume", is generally treated as a rectangular parallelepiped (RPP). The charge deposited by a given ionizing particle depends on its path in the SV. It can be evaluated from (7) where \ell is the length of the particle path in the SV, as illustrated in Fig. 8(a). An RPP volume is defined by a triplet of reals (a, b, c) where a, b, and c represent the three dimensions of the parallelepiped in decreasing order. For such an RPP volume, the chord maximum length \ell\_{max} corresponds to the main diagonal, i.e., \ell\_{max}^2 = a^2 + b^2 + c^2, and the total surface area of the volume is S = 2(ab + ac + bc) (Fig. 8(a)).*

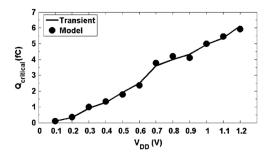

Sensitive volume approaches are based on the essential notion of circuit critical charge Q<sub>crit</sub>, originally defined for memory circuits as "*the minimum amount of collected charge that will cause a device node to change state and result in a single event upset*" [24]. In this definition, the critical charge is supposed to be independent of the current pulse shape, which supposes that the current pulse produced by the ionizing particle is short compared to the integration time constant of the circuit (including parasitic capacitances) [71].

The determination of the critical charge value can be evaluated from various mixed-mode, TCAD or circuit simulation approaches, described later in the paper. At this point, it is important to remember the remark that concluded section II.C. This remark emphasizes that the outputs from a higher-level of simulation (i.e., a circuit simulation) can be simplified (i.e., reduced to a single critical charge value) such that they can be used to define inputs to a lower-level approach (i.e., the RPP model), hence by-passing higher-level tools in the full analysis of the SEE problem and, in final, reducing simulation time significantly.

Supposing that the SV of Fig. 8(a) is attached to a sensitive node of a given circuit cell characterized by a critical charge value  $Q_{crit}$ , in a first approximation (discussed and completed later), if the charge generated by the incident ionizing particle in the SV is greater or equal to  $Q_{crit}$ , then the circuit will be disturbed, and an SEE will be produced. This condition can be written as follows

$$Q_{dep} = K \times LET \times \ell > Q_{crit} \tag{13}$$

where K is a material-dependent constant derived from (7) that depends on  $\rho$ , the density of the material and on  $E_{e,h}$ , the energy for electron-hole pair creation, and  $\ell$  is the length of the particle path inside the SV.

The primary interest of SV-based models is that it is possible to combine certain characteristics of the particle source with the calculation of the deposited charge and therefore, by comparison with a critical charge, to calculate directly the SEE error rate for a given radiation environment. In this sense, these models are particularly well-adapted for on-orbit environments characterized by an isotropic flux of heavy-ions. To be numerically tractable, a certain number of simplifying assumptions must be considered. These assumptions have been carefully reviewed and discussed by Petersen in [71]. We recall in the following the most important (all are taken from [71]):

- "The energy deposited in a sensitive volume is equal to the energy loss of an energetic ion passing through that volume as calculated using its LET."

- "Ions with the same LET have the same effect."

- "The change in LET along an ion track in the region of interest is negligible."

- "The charge generation is equal to the product of the LET of the ion and a chord of the region (as state by (13)),

Fig. 8. (a) Definition of an RPP volume of dimensions  $a \times b \times c$ , and (b) chord distribution numerically calculated from Monte Carlo simulation for an RPP volume with  $a = 20 \ \mu m$ ,  $b = 15 \ \mu m$  and  $c = 10 \ \mu m$  (histogram on 570,612 chords).

perhaps augmented by a funnel region or a diffusion region."

- "The charge collection path is independent of the LET."

- "The sensitive volume is a convex body. The charge collected from an ion track is that generated along the chord defined by the path through the sensitive volume."

- "The particle flux is isotropic at the device and therefore the LET spectrum is the same for all directions".

The charge deposited in the SV is given by the integral of the product of the chord length distribution  $f(\ell)$  of the RPP box by the LET distribution of the incoming particles [71]. Fig. 8(b) shows such a chord length distribution for an RPP volume in the form of a probability histogram. This histogram is upper bounded by the maximum chord length value, i.e.,  $\ell = \ell_{max}$ .

To directly derivate the SEE error rate from (13), one must evaluate for a given particle LET value  $\Lambda$ , the minimum chord length  $\ell_{min}$  of the particle through the sensitive volume that will create enough electron-hole pairs to cause an upset. From (13), it is evident that  $\ell_{min} = Q_{crit}/(K \times \Lambda)$ ; its *minimum minimorum* value is  $\ell_{min} = Q_{crit}/(K \times \Lambda_{max})$  where  $\Lambda_{max}$  corresponds to the maximum value of the LET spectrum related to the particle source. The number of events is then directly determined by the sum of possible paths that can lead to an adequate charge deposition in the SV. Pickel's formulation [71] uses the combination of the ionizing integral particle flux in terms of its energy deposition  $\Phi(\Lambda)$  and the path probability  $f(\ell)$

$$N = \frac{S}{4} \int_{\ell_{min}}^{\ell_{max}} \Phi(\Lambda_{min}) f(\ell) d\ell$$

(14)

where S is the total area surface of the volume,  $\ell_{max}$  is the maximum path length in the RPP volume,  $\Lambda_{min}$  is the minimum

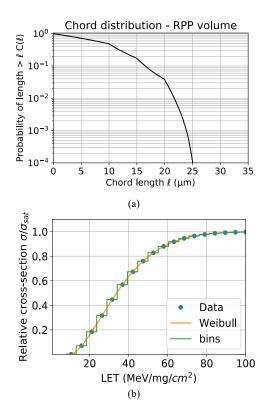

Fig. 9. (a) Integral chord length distribution corresponding to the integration of histogram of Fig. 8(b) using (15), and (b) Typical relative cross section data versus LET. The fitting of data with integral Weibull distribution is also plotted. The introduction of bins on the cross-section curve is needed for IRPP calculations.

LET that can deposit critical charge in path length  $\ell$ . From (13), the quantity to be used in (14) is  $\Lambda_{\min} = Q_{\text{crit}}/(K \times \ell)$ . Note that  $\Phi(\Lambda)$  is derived from the distribution in energy  $\Phi(E)$  using the transformation  $\Phi(\Lambda) = \Phi(E) \times (dE/d\Lambda)$ . The particle flux  $\Phi$  is supposed isotropic and is integrated over  $4\pi$  steradians.

For the convenience of calculation (availability of analytical approximations), the integral chord length distribution  $C(\ell)$  may be preferred to  $f(\ell)$ .  $C(\ell)$  corresponds to the probability of a particle traversing the sensitive volume with a chord length greater than  $\ell$  (see Fig. 9(a)), i.e.,

$$C(\ell) = \int_{\ell}^{\ell_{max}} f(\ell') d\ell'$$

(15)

Equation (14) can be rewritten following the basic form of Bradford's formulation [71,72]

$$N = \frac{N}{4} \int_{\Lambda_0}^{\Lambda_{max}} \Phi(\Lambda) \times C\left(\frac{Q_{crit}}{K\Lambda}\right) d\Lambda$$

(16)

where  $\Lambda_0$  and  $\Lambda_{max}$  are, respectively, the minimum minimorum and the maximum value of the LET spectrum related to the particle source, and from (13),  $\Lambda_0 = Q_{crit}/(K \times \ell_{max})$ .

Integral RPP (IRPP) model: In the RPP method described above (formulations of Pickel and Bradford), there is a unique critical charge that must be exceeded for the circuit cell to upset. Consequently, the curve of cross section versus LET, for a circuit modeled as a collection of identical cells with the same SV parameters and a unique  $Q_{crit}$  value, will be necessarily a step function. Such a cross-section curve, expected if all parts of all cells had the same sensitivity, does not correspond to what is generally observed. Petersen discussed in detail in [71] (and references therein) the inadequacy of the single  $Q_{crit}$  (or LET threshold) for upset rate calculations and the necessity of integrating the LET spectrum with the cross-sections curves to properly allow for changes of sensitivity across the circuit. This more general model is called the integral RPP approach.

The IRPP model allows for the variation of the internal circuit sensitivity by integrating over a distribution of event rates corresponding to the variation of the circuit cross section versus LET  $\sigma(\Lambda)$ . This curve is supposed to be experimentally known. The process consists in interpreting the  $\sigma(\Lambda)/\sigma_{sat}$ relative cross-section curve ( $\sigma_{sat}$  is the saturation cross section) in terms of a distribution of critical charges, assuming a single RPP sensitive volume with thickness c. The conversion from  $\Lambda$ to Q<sub>crit</sub> is obtained at any part of the curve via the relationship:  $c = Q_{crit}/(K \times \Lambda)$ . From the experimental data (see Fig. 9(b)) and for each discrete value of Qcrit describing the curve, the number of events is calculated by integrating the RPP chord distribution with the LET spectrum of the environment, in the same way as in (14). The result is weighted with the quantity  $(\sigma(\Lambda)/\sigma_{sat}) \times bin$ width for the bin corresponding to the considered discrete Q<sub>crit</sub> value (Fig. 9(b)). The circuit response corresponds to the sum of these individual contributions over the entire curve [71]. In mathematical terms with continuous variables and functions, if we set  $\sigma(\Lambda)/\sigma_{sat} = F(\Lambda)$ , the number of events can be expressed as

$$N = \frac{N}{4} \int F(\Lambda') \int_{\Lambda_{min}}^{\Lambda_{max}} \Phi(\Lambda) \times C\left(\frac{\Lambda'c}{\Lambda}\right) d\Lambda d\Lambda' \qquad (17)$$

where  $\Lambda_{\min}$  is the minimum LET value to deposit  $Q_{\text{crit}} = K \times \Lambda' \times c$ on the main diagonal of the RPP volume,  $\ell_{\max}$ , that gives  $K \times \Lambda_{\min} \times \ell_{\max} = K \times \Lambda' \times c$ , then  $\Lambda_{\min} = \Lambda' \times c / \ell_{\max}$ .

Different distribution functions can be used to model the  $\sigma(\Lambda)/\sigma_{sat}$  relative cross-section curve [71]. The most popular function is the integral Weibull distribution

$$rac{\sigma(\Lambda)}{\sigma_{sat}} = F(\Lambda) = 1 - exp\left\{-\left[rac{(\Lambda - \Lambda_0)}{W}

ight]^s

ight\} \quad \Lambda \ge \Lambda_0 \ = 0 \quad \Lambda < \Lambda_0$$

(18)

where  $\Lambda$  is the LET,  $\Lambda_0$  is the LET threshold, W is the width parameter and s is the shape parameter. Fig. 9(b) illustrates the plot of (18) with the following parameters:  $\Lambda_0 = 10 \text{ MeV/(mg/cm^2)}, W = 30 \text{ MeV/(mg/cm^2)}, s = 1.6.$

<u>Introduction of funneling in RPP/IRPP models</u>: The chargecollection effect attributed to funneling, illustrated in Fig. 6, can be included in RPP/IRPP models following two different approaches summarized here.

• The first method consists in increasing the depth of the sensitive volume to include the funnel contribution. The chord lengths will be then augmented, notably in the z direction, from a funnel length  $\ell_{\rm f}$ .

• The second method is to add the funnel path to the chargecollection path, but not to change the basic RPP volume. As noted by Petersen [71], most of simulation codes allow a separation of an intrinsic sensitive volume and an additional path length  $\ell_f$  attributed to the funnel. In this case, the charge deposited in the SV must be rewritten

$$Q_{dep} = K \times LET \times (\ell + \ell_f) \tag{19}$$

Consequently, the different expressions for  $\ell_{\min}$ ,  $\ell_{\max}$ ,  $\Lambda_{\min}$  and  $\Lambda_{\max}$  previously defined for (14), (16) and (17) must be reevaluated from (19).

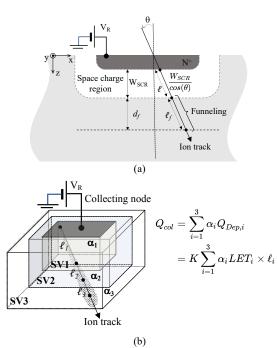

A series of funneling model descriptions conducted by Messenger and Ash can be found in [72]. Different analytical expressions of the funnel lengths can be derived from the approximate solution of the continuity equations and the electroneutrality equation. The model developed by Hu [73] proposes simple expressions for the depth of collection  $d_f$  and length of collection  $\ell_f$  related to the funneling in a n<sup>+</sup>p junction subjected to an ion strike, as defined in Fig. 10(a)

$$\ell_f = \left(1 + \frac{\mu_n}{\mu_p}\right) \frac{W_{SCR}}{\cos(\theta)} \tag{20}$$

$$d_f = \left(1 + \frac{\mu_n}{\mu_p}\right) W_{SCR} \tag{21}$$

where  $W_{SCR}$  is the width of the space charge region,  $\theta$  is the incident angle of the ionizing particle,  $\mu_n$  and  $\mu_p$  are the electron and hole mobilities in the substrate material, respectively.

For the first method and as illustrated in Fig. 10(a), the depth of the sensitive volume has to be increased by the quantity  $d_f$ given by (21) to include the funneling. It should be noted that in this case the angular dependence of the funnel contribution is not explicit, since it is already integrated with the chord length distribution functions obtained with this RPP volume (with increased depth).

Weighted sensitive volume model: This method was introduced to improve the traditional RPP approach that fails to account for different charge collection mechanisms such as drift, diffusion, or bipolar amplification [74,75]. Indeed, considering the contributions of these mechanisms in the charge collection can lead to a notable difference between the amount of charge deposited in the RPP volume by the incident ion and the amount of charge effectively collected at the circuit node. A possible expansion of the single sensitive volume RPP method is to consider several distinct SVs or nested volumes, as depicted in Fig. 10(b). A weighting of the contributions of the different volumes to the collected charge is introduced to describe intracell variation in charge collection. The model quantifies the charge collection at a node by an individual particle event as a linear combination of the charge deposited in each volume SV<sub>i</sub> scaled by the respective coefficient  $\alpha_i$  which is related to the collection efficiency (see Fig. 10(b)) [76] by

$$Q_{col} = \sum_{i} \alpha_i Q_{Dep,i} = K \sum_{i} \alpha_i LET_i \times \ell_i$$

(22)

The principle of nested regions allows to model the spatial

Fig. 10. (a) Definition of quantities used in Hu's funneling model [73], and (b) conceptual drawing of an ionizing particle passing through three sensitive volumes. The total collected charge for the event is the sum of the charge generated in each segment  $\ell_i$  in volume SVi scaled by the collection efficiency for that region  $\alpha_i$ . (Adapted after Warren et al. [74], © IEEE 2007.)

charge collection efficiency that falls off with distance from the sensitive node. For example, and as illustrated in Fig. 10(b), we could imagine an incident particle directly passing through and ionizing the innermost sensitive volume  $SV_1$  with 100% charge collection efficiency whereas those passing through a region immediately outside this volume could have only 50% charge collection efficiency in  $SV_2$  and 25% in  $SV_3$ .

The determination of the geometry, dimensions and collection efficiency of the different nested volumes can be typically performed using TCAD simulation (Section IV.D). Once more, the concluding remark of Section II.C takes on its full meaning: the nested volumes characterizing the collection of charge at a sensitive node can be defined only once per TCAD simulation, which then makes it possible to carry out a complete simulation of the circuit without using again TCAD simulations of higher level, which saves significant time.

To conclude, one additional remark: pushing this model to its limits with a very large number of SV (which would result in segmenting the trace of the particle into elementary sections), naturally leads to the collection-diffusion approach in which the expression of  $\alpha_i$  coefficients are derived from the diffusion law.

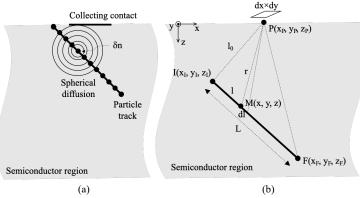

#### B. Diffusion-collection models

In the so-called "diffusion-collection" models, the energy lost by a charged particle in the semiconductor material along its track is converted in electron-hole pairs that are rearranged in the form of a succession of point charge densities of electrons and holes,  $\delta n$  and  $\delta p$  respectively with  $\delta n = \delta p = \delta n_0$  just after energy deposition and creation of the pairs (see Fig. 11(a)). The model then assumes that the transport of these discrete charge densities is governed by a pure 3D spherical diffusion law in all regions of the semiconductor domain  $\frac{\partial n(r,t)}{\partial r(r,t)} = -2$

$$\frac{\partial n(r,t)}{\partial t} = D\nabla^2 n(r,t)$$

(23)

where D is the diffusion coefficient.

In the neutral semiconductor region and in the absence of an external electric field, the separation of electron-hole pairs induces an internal field drawing the electrons and holes back together (this electric field arises from the small charge imbalance that inevitably occurs as low-mobility holes try to keep up with higher mobility electrons). Consequently, when the particle track begins to expand in its radial direction, electrons and holes in the track are foremost transported together and diffuse in train. This corresponds to ambipolar diffusion and the coefficient D in (23) must be taken equal to the ambipolar coefficient D<sup>\*</sup> given by

$$D^* = \frac{(n+p)D_nD_p}{nD_n + pD_p} \tag{24}$$

where  $D_n$  and  $D_p$  are the diffusion coefficients for electrons and holes, respectively, n and p are the total electron and hole densities, respectively.

The ambipolar diffusion constant has an intermediate value between  $D_n$  and  $D_p$  but numerically closer to the diffusion constant of the less mobile species (holes in this case). For longer times after track formation when carrier densities are reduced, D reverts to its value  $D_n$ , the diffusion coefficient of electrons in the semiconductor at equilibrium. Equation (23) can be analytically solved with the limit condition  $\lim_{t\to 0} \delta n(r_0, t) = \delta n_0$

The excess carrier density at time t and distance r from the initial track element  $\delta n_0$  is

$$\delta n(r,t) = \frac{\delta n_0}{(4\pi D^* t)^{\frac{3}{2}}} exp\left(-\frac{r^2}{4D^* t} - \frac{t}{\tau}\right)$$

(25)

where  $\tau$  is the carrier lifetime.

The resulting elementary current density due to this pure diffusion process from the initial track element  $\delta n_0$  is

$$\delta J(r,t) = q D \nabla(\delta n) \tag{26}$$

The corresponding diffusion current passing through a given closed surface S is then given by

$$\delta I_{diff} = \iint_{S} \delta \vec{J}(r,t) \cdot \vec{dS} = qD \iint_{S} \vec{\nabla} \delta n \cdot \vec{dS}$$

(27)

From these preliminary results established for a single point charge density  $\delta n_0$ , we can now generalize (25) and (27) in the case of a charge deposited along a particle track. Let consider the case illustrated in Fig. 11(b) with the following considerations:

- The ionizing particle of kinetic energy E is emitted (or arrives) at point  $I(x_I,y_I,z_I)$  and stops at point  $F(x_F,y_F,z_F)$ .

- The total charge deposited by this particle is  $Q_0 = qn_0$ =qE/E<sub>e,h</sub> where E<sub>e,h</sub> is the mean energy of creation for

Fig. 11. (a) Schematic illustration of the diffusion-collection model principle: the ionizing particle track is divided in small elements containing  $\delta n = \delta p$  electrons and holes which are able to isotropically diffuse towards the collecting electrode, and (b) definition of the main notations used in the model.

Fig. 12. The one-dimensional (1D) problem of radiation-induced carrier transport in the presence of a non-constant electric field. At t=0, the ionizing particle deposits a charge  $N_0$  in x = 0 (Dirac distribution).

an electron-hole pair in the semiconductor bulk material. For simplicity, this charge is supposed to be linearly deposited between I and F.

The integration of (25) along the track segment IF gives

$$n(t) = \frac{n_0}{8\pi L D t} exp\left(-\frac{l_0^2}{4 D t} - \frac{t}{\tau}\right) exp\left(\frac{K^2}{L^2 4 D t}\right) \\ \times \left\{ erf\left(\frac{1}{\sqrt{4 D t}} \left(L + \frac{K}{L}\right)\right) - erf\left(\frac{K}{L\sqrt{4 D t}}\right) \right\}.$$

(28)

According to (27), the diffusion current passing through an elementary surface of dimensions  $\Delta x \times \Delta y$ , centered in point P and perpendicular to axis (Oz) is given by

$$\Delta I_{diff}(t) \approx q D \frac{\Delta n(t)}{\Delta z} \times \Delta x \Delta y$$

(29)

where  $\Delta n(t)/\Delta z$  is the gradient of n in the z-direction at time t, numerically evaluated from (28) at two points, P and P'(x<sub>P</sub>,y<sub>P</sub>,z<sub>P</sub>+ $\Delta z$ ). The discrete summation of (29) over a given surface S (divided in  $\Delta x \times \Delta y$  elements) perpendicular to axis (Oz) directly gives the diffusion current I<sub>diff</sub>(t) that can be extracted by an electrode of surface S located at this level. Finally, the complete current pulse resulting from the passage of the ionizing particle in the semiconductor region can be computed from (28) and (29) considering a time mesh with uniform or nonuniform spacing (with a geometric progression for example).

The current pulse analytically calculated from the previous procedure is a diffusion current, without any contribution of an electric field in such a pure diffusion approach. In this sense, it ignores the contribution of the electric field of the space charge region in the transport and collection mechanism (Fig. 6). Several methods and model improvements have been published these two last decades that attempt to solve this important limitation of the diffusion-collection approach. Briefly, all these methods modify the evaluation of the current, which is no longer based on the diffusion gradient, but which relies on the introduction of a collection velocity at the level of the collecting electrode. In its simplest revised version, the charge given by (28) is converted into a current by multiplying n(t) by the elementary charge and by the average collection velocity  $\upsilon_{col}$ evaluated over the space charge region of the reverse-biased drain. This quantity is then integrated on the surface S of the collecting electrode

$$I(t) = q \iint_{S} v_{col} \cdot n(t) dx dy$$

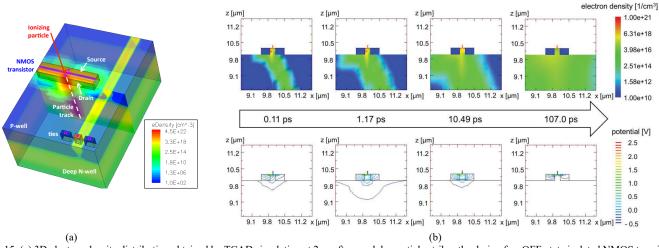

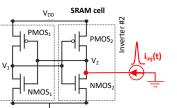

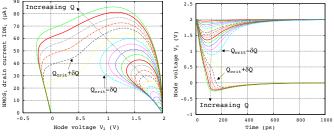

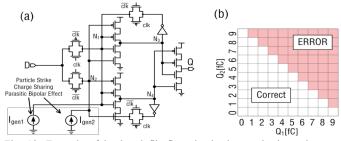

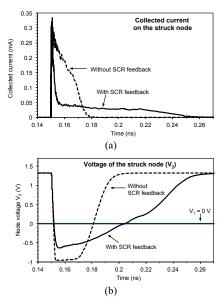

(30)