## 24.5 A 0.5V 1.27mW Nose-on-a-Chip for Rapid Diagnosis of Ventilator-Associated Pneumonia

Kea-Tiong Tang<sup>1</sup>, Shih-Wen Chiu<sup>1</sup>, Chung-Hung Shih<sup>2</sup>, Chia-Ling Chang<sup>1</sup>, Chia-Min Yang<sup>1</sup>, Da-Jeng Yao<sup>1</sup>, Jen-Huo Wang<sup>1</sup>, Chien-Ming Huang<sup>1</sup>, Hsin Chen<sup>1</sup>, Kwuang-Han Chang<sup>1</sup>, Chih-Cheng Hsieh<sup>1</sup>, Ting-Hau Chang<sup>1</sup>, Meng-Fan Chang<sup>1</sup>, Chia-Min Wang<sup>1</sup>, Yi-Wen Liu<sup>1</sup>, Tsan-Jieh Chen<sup>3</sup>, Chia-Hsiang Yang<sup>3</sup>, Herming Chiueh<sup>3</sup>, Jyuo-Min Shyu<sup>1</sup>

<sup>1</sup>National Tsing Hua University, Hsinchu, Taiwan, <sup>2</sup>Taipei Medical University, Taipei, Taiwan, <sup>3</sup>National Chiao Tung University, Hsinchu, Taiwan

Ventilator-associated pneumonia (VAP) is the most frequently acquired infection among patients that receive mechanical ventilation in the intensive-care unit (ICU). The mortality rate for VAP lies in the 20-to-50% range and could be even higher in some ICUs. A standard operation procedure to VAP treatment includes a sequence of chest radiography, sputum gram stain, sputum culture, and empiric therapy, initially with antibiotics covering broad pathogens. However, collection of the gram stain and culture of lower respiratory tract specimen is usually not time-efficient (up to 5 days), delaying the initiation of therapy and unacceptable for critically ill patients. A rapid and accurate diagnosis for VAP is therefore crucial, but still unavailable. It is known that microorganisms generate complex metabolites during infection. Fast detection is feasible by examining metabolic wastes in proximal end of the expiratory device, demanding a miniaturized, battery-powered, gas-sensing device. In this work, a fully integrated low-power nose-on-a-chip with a robust learning kernel is developed for such a vital clinical need.

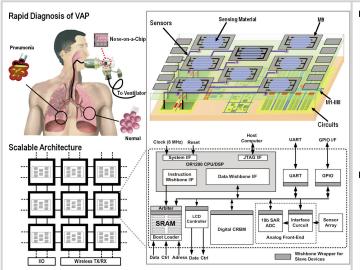

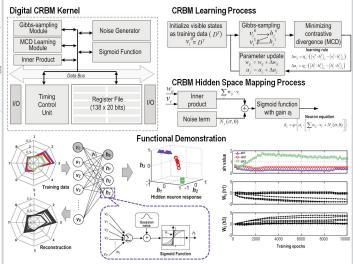

Figure 24.5.1 shows the target application scenario and a top-level system view of the nose-on-a-chip. With a 3D structure, the chip integrates 8 sensors on top and processing circuits at the bottom, completely in a standard CMOS process. The signal-processing circuits include an 8-channel adaptive sensor interface, a SAR analog-to-digital converter (ADC), a RISC processor core with an 8K×32b cache memory, and a dedicated continuous restricted Boltzmann machine (CRBM) kernel for data clustering. With the scalability to form a larger array of chips, massive sensor information can be processed efficiently in parallel to enhance sensing performance for a diversity of applications.

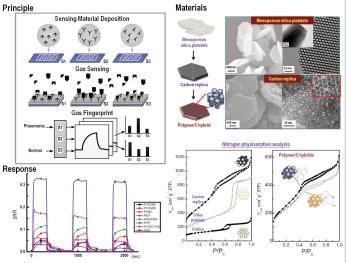

Figure 24.5.2 describes the principle of the nose-on-a-chip and the nanocomposite sensing materials. Distinct sensing materials deposited on the interdigitated electrodes (IDE) form an array of sensors. The collective response from the sensor array constructs unique gas fingerprints. Polymer-carbon composites are used for sensing materials. The carbon-based materials can be: carbon black, carbon nanotube, and mesoporous carbon, where mesoporous carbon has demonstrated superior sensitivity and reversibility. Mesoporous carbon is fabricated from platelet-shaped mesoporous SBA-15 silica and polymers are grown onto the carbon, as shown in the SEM images.

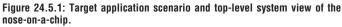

The sensing material is deposited on the IDE, as shown in Figure 24.5.3. The passivation layer is removed with the  $400 \times 400 \mu m^2$  opening windows. An 8-channel adaptive interface reads out the sensor signals. The interface circuit works as a negative-feedback loop to tune out long time constant signals such as temperature, humidity, and background odors. This sensor interface consumes 215µW. A 0.5V 10b SAR ADC with a charge-average switching (CAS) technique [1] is adopted. The CAS DAC generates top-plate voltage shift by charge averaging instead of conventional charging and discharging operation; it effectively reduces the switching energy to 88.6 CV<sub>ref</sub><sup>2</sup> (48% power saving) and minimizes the disturbance and noise of the reference supply voltage. Without the need of an extra voltage reference and common-mode shift issue during conversion, the CAS technique is robust and suitable for integration into a low-voltage SoC. This SAR ADC consumes 1.15µW.

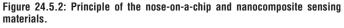

Figure 24.5.4 shows the architecture, learning process flow, and functionality of the CRBM kernel [2]. The CRBM is a probabilistic neural network by injecting Gaussian noise to robustly generalize the variability of data of the same type. By adapting the connection weights  $\{w_{ij}\}$  and the sigmoid gain  $\{a_j\}$ , the CRBM learns to regenerate training examples as the states of visible neurons. The CRBM kernel is trained to model three types of sensory data for 10,000 epochs. The

similarity between the reconstruction and the training data indicates the data are properly modeled. Moreover, the learning trajectories of all  $\{a_j\}$  and  $\{w_{ij}\}$  reach equilibrium after 5,000 training epochs. The hidden neurons of the trained CRBM respond differently to sensory data. This helps to cluster the sensory data and to reduce the data dimensions for reliable classification.

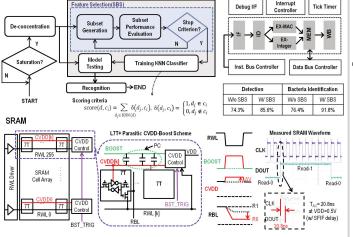

Figure 24.5.5 shows the flow of data recognition and the processing unit for gas identification based on a scalar 32b reduced instruction set computing (RISC) core. Before the data enter the recognition model, the RISC core checks whether the response data are saturated, and then performs normalization against variation in gas concentration. Then, features are selected based on an objective function to train a K-Nearest Neighboring (KNN) classifier. A sequential backward selection (SBS) scheme is adopted here. The SBS has a computation complexity of O(N), lower than  $O(2^n)$  from exhaustive search. Because SBS extracts informative features, the accuracy on pneumonia detection increases from 74.3 to 85.6% and the accuracy on pneumonia bacteria identification increases from 76.4 to 91.8%.

L7T SRAM cells [3] are employed to achieve a low VDD<sub>min</sub>. The L7T cells, however, suffer from limited read-bitline (RBL) voltage swing due to BL clamping current from unselected read-ports (RPs) of the accessed column. To increase the read margin, the gate-bias of 1T-RP is increased by boosting the cell-VDD (CVDD) in a read cycle through parasitic capacitors (PC) between metal-lines (BOOST-CVDD) on top of L7T cells. This parasitic boost-CVDD (PBV) scheme consumes only 1% area overhead. Measured read-waveform of PBV-L7T-SRAM probed through SRAM-Flash interface (SFIF) is shown. At SRAM-VDD=0.5V, this 256-rows 256Kb SRAM achieves 20.8ns read access time, including the path-delay due to SFIF, level-shifter, and I0-pads.

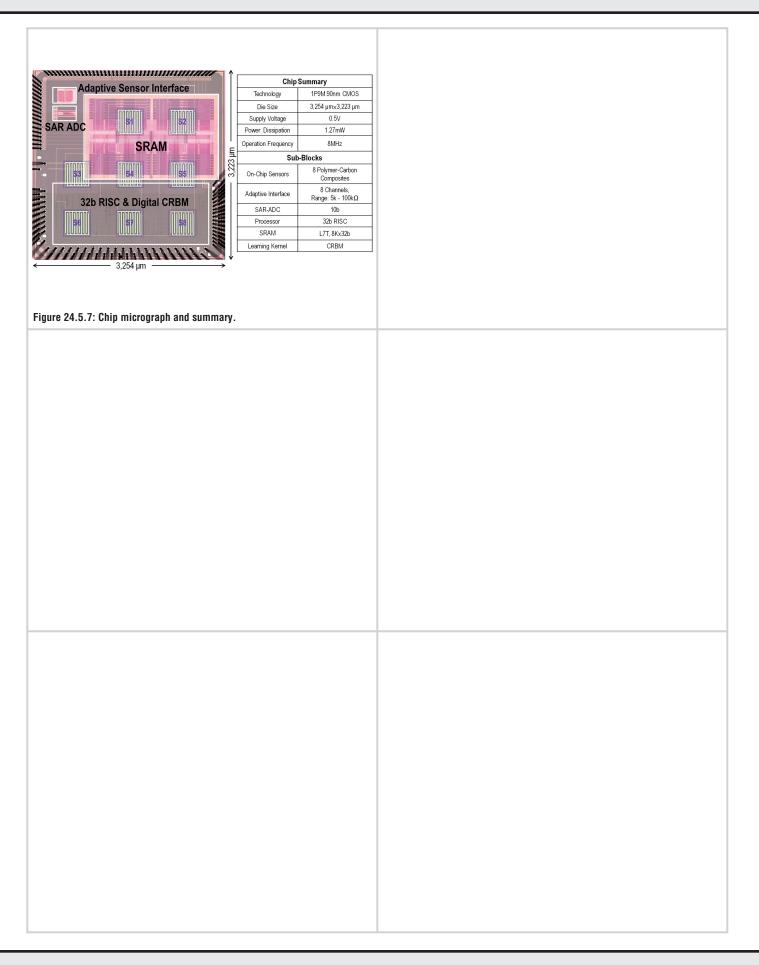

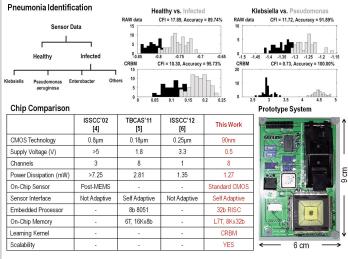

The functionality of the chip was verified in clinical trials. 74 samples infected with pneumonia (35 Klebsiella, 39 Pseudomonas aeruginosa) were categorized as experimental group and 43 samples as control group. Figure 24.5.6 shows the classification results performed in two steps: 1) recognizing whether the patient was infected, and 2) if infected, identifying which microorganism was the source. Although the raw data from these two groups overlap, the CRBM improves the accuracy from 89.74 to 95.73% by reducing Clustering Fisher Index (CFI) from 17.89 to 10.30. For the infected patients, the accuracy is improved from 91.89 to 100% by reducing CFI from 11.72 to 0.73. The chip occupies 10.49mm<sup>2</sup> in 90nm CMOS and dissipates 1.27mW. It achieves the highest level of integration and highest computation capability with the lowest power dissipation among state-of-the-art designs (see comparison table in Fig. 24.5.6). This chip fully integrates on-chip sensors, adaptive sensor interface, 10b SAR ADC, 32b RISC with a low-voltage L7T 8K×32b SRAM, along with a robust CRBM kernel, and scalability for higher-dimensional signal processing. This work provides a promising solution for a long-time unresolved issue — a rapid diagnostic strategy to VAP. Figure 24.5.7 shows the chip micrograph and summarv.

## Acknowledgements:

This work was supported by *NSC* under contract number NSC-102-2220-E-007-006. The authors thank *CIC* for chip fabrication.

## References:

[1] C.-Y. Liou, *et al.*, "A 2.4-to-5.2fJ/conversion-step 10b 0.5-to-4MS/s SAR ADC with Charge-Average Switching DAC in 90nm CMOS," *ISSCC Dig. Tech. Papers*, pp. 280-281, Feb. 2013.

[2] H. Chen, *et al.*, "Continuous Restricted Boltzmann Machine with an Implementable Training Algorithm," *IEE P-VIS Image Sign*, pp. 153-158, Aug. 2003.

[3] M.-F. Chang, *et al.*, "A Sub-0.3 V Area-Efficient L-Shaped 7T SRAM With Read Bitline Swing Expansion Schemes Based on Boosted Read-Bitline, Asymmetric-VTH Read-Port, and Offset Cell VDD Biasing Techniques," *IEEE J. Solid-State Circuits*, pp. 2558-2569, Oct. 2013.

[4] C. Hagleitner, *et al.*, "A Gas Detection System on a Single CMOS Chip Comprising Capacitive, Calorimetric, and Mass-Sensitive Microsensors," *ISSCC Dig. Tech. Papers*, pp. 430-431, Feb. 2002.

[5] K.-T. Tang, *et al.*, "A Low-Power Electronic Nose Signal-Processing Chip for a Portable Artificial Olfaction System," *IEEE T. BioCAS*, pp. 380-390, Aug. 2011.

[6] V. Petrescu, *et al.*, "Power-efficient readout circuit for miniaturized electronic nose," *ISSCC Dig. Tech. Papers*, pp. 318-319, Feb. 2012.

Figure 24.5.3: Adaptive sensor interface, on-chip sensor, and SAR ADC.

Figure 24.5.5: Flow of data recognition, RISC core architecture, and low-voltage SRAM.

Figure 24.5.4: Architecture, learning process flow, and functionality of the CRBM kernel.

Figure 24.5.6: Clinical results, chip comparison, and prototype system.