# Low Distortion Switching Amplifier With Discrete-Time Click Modulation

Leandro Stefanazzi, Fernando Chierchie, Member, IEEE, Eduardo E. Paolini, and Alejandro R. Oliva

Abstract—An all-digital Class-D amplifier based on a discretetime implementation of the click modulator is presented. The algorithm is able to generate binary signals with separated baseband, displacing the harmonic content produced by the modulation process above certain frequency chosen by the designer. Perfect demodulation can be achieved by a simple low-pass filter. Previous implementations of the discrete-time click modulator reported in the literature suffer from aliasing in the frequency domain. The approach proposed here avoids aliasing, without the necessity to increase (interpolate) the sampling frequency of the signals. Following a brief theoretical introduction, the performance of the proposed architecture is demonstrated by experimental measurements performed on an H-bridge amplifier. An 88 dB signalto-noise ratio (SNR) and a total harmonic distortion (THD) + N less than 0.04% is attainable over the entire audio band, extending from 20 Hz up to 20 kHz; on the other hand, no traces of IMD appear above the predicted noise floor. These performance indices are obtained for switching rates as low as 40 kHz. The reduction of the switching frequency provides more flexibility for the design of the demodulation stage allowing to trade off between the complexity of the demodulation filter and the achievable efficiency of the switching stage.

Index Terms—Digital modulation, pulse width modulation, switching amplifiers.

#### I. INTRODUCTION

IGITAL modulation and control of switching converters has been a topic of constant research over the last decades [1], with applications ranging from motor control [2]–[4] to power inverters [5], [6]. Pulse-width modulation (PWM) [7] has been widely used for both analog and digital implementations. Although analog PWM is fairly simple involving only a comparison of the modulating signal with a triangle or sawtooth carrier, its discrete-time version known as uniform PWM (UPWM) has a major drawback: baseband distortion appears together with intermodulation products that cannot be removed

Manuscript received February 25, 2013; revised May 31, 2013; accepted August 3, 2013. Date of publication October 25, 2013; date of current version January 31, 2014. This work was supported in part by PGI UNS 24/ZK21, ANPCyT PAE-PICT-2007-02344, PIP-CONICET 02671, and PIP-CONICET 0617.

L. Stefanazzi, F. Chierchie, and A. R. Oliva are with the Consejo Nacional de Investigaciones Científicas y Técnicas (CONICET), Buenos Aires 1917, Argentina (e-mail: lstefanazzi@uns.edu.ar).

E. E. Paolini is with the Comisión de Investigaciones Científicas (CIC), Instituto de Investigacion en Ingeniería Eléctrica Alfredo Desages (IIIE) (UNS-CONICET), Departamento de Ingeniería Eléctrica y de Computadoras, Universidad Nacional del Sur, Bahía Blanca 8000, Argentina.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TIE.2013.2281299

by linear filtering [8]. Several solutions to the problem of the digital implementation of PWM are found in the literature. In [9], [10] the input signal is pre-distorted with a neural network trained using the model of the digital amplifier. Digital feedback of the signal at the output of the switching stage [11], [12], allows to compensate the nonlinearities of the power stage and the power supply. A pseudo-natural implementation for digital PWM is presented in [13]. The latter mimics the behavior of the continuous-time PWM modulator from sampled signals, lowering the intermodulation products in the baseband. Another difficulty of PWM-based schemes is the finite temporal resolution of the circuit that positions the edges of the binary signal, a problem studied in [14]–[16]. Sigma-Delta modulation (SDM) [17] has also been used to control Class-D stages [18], [19]. A comparison between SDM and PWM for such applications can be found in [20]. The drawback of SDM is that the switching rate of the power stage tends to be high, 350 kHz to 1 MHz [21]–[26], which reduces the efficiency of the switched power stage.

In the continuous-time realm, click modulation [27] is a modulation technique which produces a binary signal with the property that preserves the baseband, displacing all the modulation-dependant frequency content above a certain frequency specified by the designer. High frequency harmonics can be removed with a low pass filter (LPF) and the continuous-time modulating signal is recovered without distortion. However, click modulation shares one of the problems of PWM: previous discrete-time implementations produce intermodulation products that are impossible to remove.

The application of click modulation to switching amplifiers was first introduced by Streitenberger *et al.* in 1999 (see [28]). In this paper, it is pointed out that classical PWM-based modulation schemes are insufficient for high-performance audio amplification, and the concept of separated baseband modulation for switching amplifiers is introduced. Based on these ideas, some other attempts to implement a discrete-time version of the click modulator are reported in [28]–[37]. These techniques use interpolation to mitigate the aliasing that appears in the discrete-time version of a key component of the click modulator (namely, the analytical exponential modulator), but they only result in a modulator that approximately behaves as the continuous-time click modulator.

A different approach was presented recently in [38] where the spectral characteristics of the exponential function together with the structure of the modulator are exploited. This results in a discrete-time click modulator that shares the same spectral characteristic that its continuous-time domain counterpart.

Fig. 1. Block diagram of the discrete-time click modulator.

In this paper, experimental measurements of an off-line implementation of the discrete-time click modulator [38] driving a Class-D power amplifier are provided. The sequence of samples of the input signal are used to generate the switching times of the modulated wave without needing to interpolate or to increase the sampling frequency of the input signal, as in other approaches [28]–[37].

The quality of the entire amplification chain is evaluated using standard audio tests. A maximum signal-to-noise ratio (SNR) of about 88 dB is obtained, being the quantization of the duty cycles responsible for this limit. On the other hand, the intermodulation distortion test (IMD) does not show any noticeable spurious components falling within the audio band. These experiments show that this implementation of the digital click modulator is able to keep the baseband free of distortion, even for multitone signals.

This spectral characteristic of the discrete-time click modulator makes it possible to lower the switching frequency of the power stage to almost twice the Nyquist frequency. This results in a greater flexibility for the designer, because it allows to dramatically reduce the switching losses as a result of a low switching rate, or to easy the design of the reconstruction filter by increasing the switching frequency and creating a guard band free of distortion components.

This article is organized as follows. The discrete-time modulation algorithm focusing on implementation issues is detailed in Section II. In Section III experimental measurements of the off-line implementation of the discrete-time modulator driving a Class-D amplifier are discussed. Conclusions and comments on possible future work are given in the final section.

## II. DISCRETE-TIME MODULATION ALGORITHM

A block diagram of the discrete-time click modulator is shown in Fig. 1. This presentation focuses on the implementation of each block; for a detailed theoretical description the reader is referred to [38].

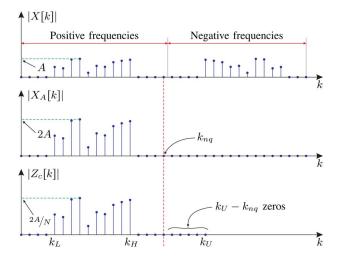

The input signal is assumed to be a sequence x[n] of length N and the output is the binary wave q(t). The remarkable feature of the modulation algorithm is that the spectrum of the signal q(t), used to drive the power switches, does not have any unwanted frequency components in the baseband. To facilitate the interpretation, it can be assumed that the sequence x[n] is composed by the samples of a continuous-time signal x(t) sampled every  $T_s = 1/f_s$  s. Because of the inherent periodicity of discrete Fourier transforms, the first (second) half of the Fourier transform X[k] of x[n] can be related to the positive (negative) frequency axis of the spectrum X(f) of the continuous-time signal x(t). The spectrum X[k] of x[n] does not vanish within the interval  $[k_L, k_H] \cup [N - k_H, N - k_L]$ .

An analytic signal  $x_A[n]$  is derived from x[n] using a Hilbert transformer (block HT in Fig. 1). The spectrum  $X_A[k]$  of

$x_A[n]$  is zero for the negative frequencies, i.e.,  $X_A[k]=0$  for  $k\in [k_{nq}+1,N-1]$  with  $k_{nq}$  being the index associated with the Nyquist frequency of the input signal

$$k_{nq} = \begin{cases} N/2 - 1, & \text{if } N \text{ is even} \\ (N - 1)/2, & \text{if } N \text{ is odd.} \end{cases}$$

The Discrete-Time Analytical Exponential Modulator plus Filtering, labeled as block DT-AEMF in Fig. 1, is the key component of this discrete-time implementation of the click modulator. It allows to obtain an alias-free version of its continuous-time counterpart, the Continuous-Time Analytical Exponential Modulator plus Filtering (CT-AEMF) [38]. Its implementation is based on applying successive convolutions to a scaled version of the spectrum of the analytic signal. The output of the DT-AEMF is the filtered sequence  $z_L[n]$ , where its Discrete Fourier Transform (DFT)  $Z_L[k]$  is given by [38]

$$Z_L[k] = \sum_{\ell=0}^{L} \tilde{Z}_{\ell}[k] \tag{1}$$

with L chosen such that the resulting sequence  $z_L[n]$  is the exact equivalent of the CT-AEMF output [38]. The sequences  $\tilde{z}_\ell[n]$  are computed recursively by

$$\tilde{z}_{\ell}[n] = \frac{1}{\ell} \left( \tilde{z}_{\ell-1}[n] \times z_c[n] \right) \otimes h_H[n] \tag{2}$$

or in the frequency domain

$$\tilde{Z}_{\ell}[k] = \frac{1}{\ell} \left[ \tilde{Z}_{\ell-1}[k] \otimes Z_c[k] \right] H_H[k] \tag{3}$$

where  $\widehat{M}$  is the M-point circular convolution, and  $z_c[n]$  is a filtered and scaled version of  $x_A[n]$  (more on this later). The term  $H_H[k]$  in (3) corresponds to the DFT of the analytic LPF with impulse response  $h_H[k]$ , and it is given by

$$H_H[k] = \begin{cases} 1, & \text{if } 0 \leqslant k \leqslant k_U \\ 0, & \text{if } k_U + 1 \leqslant k \leqslant M - 1. \end{cases}$$

The length of the sequences  $\tilde{z}_{\ell}[n]$  is  $k_U+1$ , where  $k_U>k_H$  is the index that indicates the end of the baseband. These sequences are zero-padded up to the length M of the circular convolution, with the value of M chosen so that no aliasing occurs in the computation, i.e.,  $M\geqslant 2(k_U+1)-1$ . The circular convolution is implemented using the FFT thus reducing computational costs, i.e.,

$$\tilde{Z}_{\ell-1}[k] \otimes Z_c[k] = \text{IFFT} \left[ \text{FFT} \left[ \tilde{Z}_{\ell-1}[k] \right] \times \text{FFT} \left[ Z_c[k] \right] \right]$$

(4)

where the inner FFTs (and the IFFT) are of length M and the symbol "×" in brackets indicates point-wise multiplication. The term  $\tilde{Z}_0[k]$  (corresponding to  $\ell=0$ ) is given by  $\tilde{Z}_0[k]=\delta[k]$ , for  $0\leqslant k\leqslant k_U$ . The frequency components of the input signal x[n] that lay in the interval  $[0,k_U]$  are guaranteed to be free of distortion at the output of the modulator.

<sup>&</sup>lt;sup>1</sup>In many applications, acceptable results can be obtained using a lower number of terms.

Fig. 2. Relationship between X[k],  $X_A[k]$  and  $Z_c[k]$ .

The sequence  $z_c[n]$  used in the computation of the terms  $\tilde{z}_\ell[n]$  in (2) is derived from the scaled version of the analytic signal  $x_A[n]$  using the filter  $h_H[n]$ . In this case it is easier to calculate the sequences  $\tilde{z}_\ell[n]$  in the frequency domain using (3). The DFT  $Z_c[k]$  of the sequence  $z_c[k]$  is given by

$$Z_c[k] = -jX_A[k]H_H[k]/N \tag{5}$$

where  $j=\sqrt{-1}$  is the imaginary unit. When computing  $Z_c[k]$  using this equation, it should be noted that the sequences  $X_A[k]$  and  $H_H[k]$  may have different lengths, say N and M, respectively. To properly apply the filter  $H_H[k]$  the sequence  $X_A[k]$  should be zero padded with M-N zeros. The action of the analytic LPF  $H_H[k]$  is to retain the components of  $X_A[k]$  for  $k \in [0, k_U]$  while zeroing the rest.

Choosing a value for the frequency index  $k_U$  (the end of the guard band) results in three possible scenarios.

- 1)  $k_U < k_H$ : this setting must be avoided because the spectrum of the signal x[n] will be distorted within the interval  $[k_U, k_H]$  by the appearance of frequency components produced by the modulator. As a consequence, the diagram of Fig. 1 does not behaves as a discrete-time counterpart of the continuous-time click modulator.

- 2)  $k_H < k_U < k_{nq}$ : the baseband components of the signal are guaranteed to be free of distortion with a guard band extending form  $k_H$  to  $k_U$ . A sharp reconstruction filter at the output of the power stage may be required for demodulation if  $k_U$  is close to  $k_{nq}$ . The selection  $k_U = k_{nq}$  results in N = M, being only necessary to scale  $X_A[k]$  by N to calculate the sequence  $Z_c[k]$  as indicated by (5).

- 3)  $k_U > k_{nq}$ : the baseband extends beyond the Nyquist frequency of the input signal. The sequence  $X_A[k]$  in the derivation of  $Z_c[k]$  must be zero padded because N < M, which is equivalent to displace the Nyquist frequency from  $k_{nq}$  to  $k_U$ . This is the preferred setting as it allows more flexibility in the design of the reconstruction filter.

Fig. 2 shows the relationship between X[k],  $X_A[k]$  and  $Z_c[k]$  (the spectra of x[n],  $x_A[n]$  and  $z_c[n]$ , respectively) for the normal operation mode, i.e.,  $k_U > k_{nq}$ .

It is useful to summarize the steps required to obtain the sequence  $z_L[n]$  from the input x[n].

- 1) Compute the N-point DFT X[k] of the input signal x[n].

- 2) Discard the second half of its samples to obtain the spectrum  $X_A[k]$  of the analytic signal  $x_A[n]$  and scale down the result by 2 (except for the 0 and  $k_{ng}$  indexes).

- 3) Add zeros from  $k_{nq}$  to  $k_U$  and scale down the result by N to obtain the sequence  $Z_c[k]$  [equation (5)].

- 4) Perform a zero-padding of  $M-(k_U+1)$  points over the sequences  $Z_c[k]$  and  $\tilde{Z}_{\ell-1}[k]$ , with  $M \geq 2(k_U+1)-1$ .

- 5) Compute the M-point circular convolution using (4).

- 6) Discard the last  $M (k_U + 1)$  samples of the result so that  $\tilde{Z}_{\ell}[k]$  has a length of  $k_U + 1$  points and divide the result by  $\ell$  [Equation (3)].

- 7) Add the sequences  $\tilde{Z}_{\ell}[k]$  as indicated by (1) to obtain the DFT  $Z_L[k]$  of the DT-AEMF output  $z_L[n]$ .

The advantage of using the DT-AEMF method is that the sequences  $\tilde{z}_{\ell}[n]$  are already filtered and alias free, so the number of terms L in (1) can be increased arbitrarily [38].

The last step in the modulation process is to determine the switching times of the continuous-time binary waveform q(t). This computation is carried out by the block ZCD of Fig. 1. In the continuous-time click modulator [27], an auxiliary real signal s(t) is derived from the filtered AEM output. The zeros of s(t) are interleaved with those of the carrier  $c(t) = \sin(2\pi f_C t)$ . This interleaving property allows building the signal q(t), setting the rising edge at the zeros of the carrier c(t) and the falling edge at the zeros of s(t). The switching rate  $f_Q$  of the resulting square wave is twice the carrier frequency, i.e.,  $f_Q = 2f_C$ .

For the discrete-time click modulator the real sequence s[n] is obtained from the output of the DT-AEMF  $z_L[n]$  (see [38]) as

$$s[n] = \operatorname{Re}\left\{z_L[n]e^{-j\omega_C n}\right\}$$

where  $\omega_C=2\pi f_C/f_s$ . For the click modulator to work properly it is crucial to determine the exact time instant at which an hypothetical continuous-time signal s(t) (being s[n] its samples every  $t=nT_s$  s) takes the zero value. In previous works, zero crossings were computed using a polynomial built using some samples around the sign changes of s[n] [32], [35]–[37]. The detection improves when either the order of the polynomial is increased or the sampling frequency of the signal is augmented. However, the main advantage of using the DT-AEMF for computing  $z_L[n]$  is that the sampling rate does not need to be increased. To exploit this advantage, a novel method for computing the zero crossings of s(t) is introduced in [38] which uses the frequency information provided at the output of the DT-AEMF.

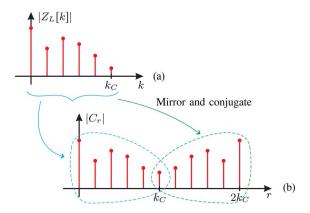

As it is demonstrated in [38], exact computation of the zero-crossings of s(t) is possible by computing the roots of the auxiliary polynomial  $P(\sigma)$  defined as

$$P(\sigma) = \sum_{r=0}^{k_C} \left( Z_L[r] \sigma^r + \overline{Z_L}[k_C - r] \sigma^{r+k_C} \right) = \sum_{r=0}^{2k_C} C_r \sigma^r$$

(6)

Fig. 3. Polynomial  $P(\sigma)$  from  $Z_L[k]$ : (a) DFT  $Z_L[k]$  of the signal  $z_L[n]$  at the output of the DT-AEMF and (b) coefficients  $C_r$  of  $P(\sigma)$ , where r indicates the power of the variable  $\sigma$ .

and mapping its zeros  $\sigma_n$  to switching times using the transformation

$$t_n = \frac{N}{2\pi f_s} \arg(\sigma_n). \tag{7}$$

In the time domain, the signal p(t) associated with the polynomial  $P(\sigma)$  is obtained by applying a frequency shift to the signal s(t) to avoid negative powers of the variable  $\sigma$  to appear, i.e.,  $p(t) = e^{j2\pi f_C t} s(t)$ . For the practical implementation, the coefficients of the polynomial  $C_r$  in (6) can be obtained from  $Z_L[k]$  according to

$$C_r = \begin{cases} Z_L[r], & \text{for } r = 0, \dots, k_C - 1\\ 2\text{Re}\{Z_L[r]\}, & \text{for } r = k_C\\ \overline{Z_L}[2k_C - r], & \text{for } r = k_C + 1, \dots, 2k_C. \end{cases}$$

(8)

The derivation of the coefficients of the polynomial  $P(\sigma)$  from  $Z_L[k]$  is represented in Fig. 3.

To generate the binary waveform q(t) the zero-crossings  $t_n$  of the signal s(t) given by (7) are interleaved with those of the carrier c(t). These do not need to be explicitly computed as they occur at  $t_C = nT_Q$ , with  $n = 0, 1, \ldots$  and  $T_Q = 1/f_Q$  the switching period. The pulse widths  $\Delta[n]$  of the signal q(t) in Fig. 1 are given by the time difference  $t_n - t_C$ , i.e.,

$$\Delta[n] = t_n - nT_O, \quad \text{with } n = 0, 1, \dots$$

(9)

The pulse width values  $\Delta[n]$  are normalized between 0 and 1 for  $t_n$  varying between 0 and  $T_Q$ .

## A. Effects of Duty Cycle Quantization

The accuracy at which the switching times of the binary signal q(t) are positioned impacts on the quality of the modulator. The effects of the quantization of the zero-crossing detection as well as the input level were studied in [36] for the discrete-time version of the click modulator. The relationship between the word length and the maximum SNR is given by

$$SNR[dB] \approx 6.02 \cdot b + \rho \tag{10}$$

where  $\rho$ ,  $-4.2~{\rm dB} < \rho < 19~{\rm dB}$ , depends on the amplitude of the input signal and b is the number of bits. In this case the quantization process is applied to the pulse widths  $\Delta[n]$  given by (9). The quantized values will be referred to as  $\tilde{\Delta}[n]$ .

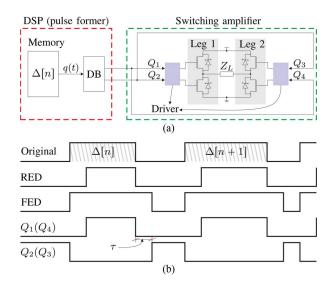

Fig. 4. Block diagram of the (a) amplifier and (b) generation of the control signals.

The limit given by (10) is derived from the additive noise model for the quantization error  $\varepsilon[n]$  [39], [40], a traditional model for the quantization of the amplitudes of a discrete-time signal. However, when the quantization steps are large or the number of bits b is small, this model does not hold because the error signal  $\varepsilon[n]$  is correlated to the unquantized signal  $\Delta[n]$ , resulting in the appearance of harmonic frequency components within the baseband of q(t). One of the techniques used to diminish the correlation is dithering [41], consisting on adding a random value r[n] to the signal  $\Delta[n]$  prior quantization so that  $\Delta[n]$  and  $\varepsilon[n]$  are uncorrelated

$$\tilde{\Delta}[n] = \Delta[n] + r[n]. \tag{11}$$

The result is an almost white quantization error  $\varepsilon[n]$  and a flat noise floor. The drawback of the dithering technique is that the noise floor is increased by an amount that depends on the variance of the random process r[n].

There is a trade off between the whitening effect of r[n] and the increment of the noise floor. A practical rule-of-thumb is to set the peak-to-peak amplitude of the random process r[n] equal to the quantization step  $q=1/2^b$  [41], where b is the number of bits and 1 is the peak-to-peak amplitude of the value to be quantized  $\Delta[n]$ . A zero-mean uniform random process is used in this case, i.e.,  $r[n] \sim \mathcal{U}(-q/2,q/2)$ .

# III. EXPERIMENTAL RESULTS

The discrete-time modulation algorithm was tested using a switching power amplifier built using standard components. The system is composed of two main blocks, namely, the pulse former and the switching stage. The pulse former is implemented with two integrated PWM modules of the TMS320F8335 DSP. It reconstructs the modulated signal q(t) and adds dead-time to avoid cross-conduction. The switching stage is built with a pair of high-speed synchronous drivers (MCP14700) with two independent PWM inputs. These drivers control the switches (IRF8313PbF), one for each leg. The block diagram of the amplifying system is represented in Fig. 4(a).

To synthesize the modulated signal q(t), a table [containing the values  $\Delta[n]$  given by (9)] is loaded into the memory of the DSP. Prior quantization the random value r[n] is added to  $\Delta[n]$  as indicated by (11), whenever the dithering option is selected. The pulse former is based on a counter that increments its value by one when the clock ticks. When it reaches the value stored in a comparison register (that is proportional to the pulse width  $\tilde{\Delta}[n]$ ), the output toggles. The counter resets at the PWM period  $T_Q$  (sawtooth carrier) and the process starts again. With this architecture, the time-resolution b (in bits) of the edges of the binary signal depends on the switching frequency  $f_Q$  and the DPS's maximum clock frequency

$$b = \log_2\left(\frac{f_{clk}}{f_Q}\right)$$

which results in b=119 bits for  $f_{clk}=150$  MHz and  $f_Q=40375$  Hz. The maximum achievable SNR is given by (10) and results in 67.39 dB < SNR < 90.39 dB, depending on the amplitude of the modulating signal.

The signals  $Q_1,\ Q_2,\ Q_3$  and  $Q_4$  that drive the bridge are generated from q(t) adding the dead time to avoid cross conduction between same-leg switches. This scheme uses the same control signal for the upper (lower) switch of the first leg and the lower (upper) switch of the second leg, i.e.,  $Q_1=Q_4$  and  $Q_2=Q_3$ . Fig. 4(b) shows the waveform of the control signals. The first row depicts the output of the click modulator. The signals labeled RED (rising-edge delayed) and FED (falling-edge delayed) are internally generated by the dead-band generator module [block DB in Fig. 4(a)] of the DSP. From these signals the complementary PWM outputs are derived depending on the configuration of the DSP. In this case it was selected active-high complementary, which means that if the control signal is high the corresponding transistor is on.

The introduction of dead times slightly modifies the switching time of the ideal binary signal distorting the output waveform. This adversely affects the resulting SNR at the output of the amplifier. The effects of the duty cycle variation due to dead times in the spectra of the binary signal are out of the scope of this work [42]–[44]. However, they were minimized by maintaining the dead time less than 0.2% of the PWM period. This value can be achieved as a result of the low switching rate ( $\approx 40~\text{kHz}$ ). Fig. 5 shows a picture of the power bridge with the detail of the switches and the drivers.

To ensure that the full audio bandwidth (20 Hz to 20 kHz) is free from distortion, the baseband's upper limit  $f_U$  is set equal to the carrier frequency  $f_C = f_Q/2$ . This value for  $f_U$  imposes a high order LPF for accurate reconstruction of the signal after amplification. In our experiments it was so chosen to maximize SNR due to hardware limitations. The requirements on the filter can be reduced if  $f_U$  and  $f_C$  are increased.

# A. IMD Measurement

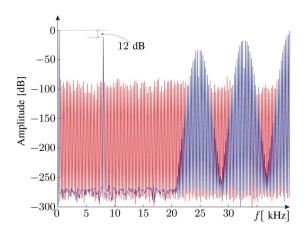

The most widely used technique for IMD measurement employs two sine waves of frequency  $f_1$  and  $f_2$  as the stimulus signal. The nonlinear behavior of the amplifier manifests as an infinite number of IMD products in the output spectrum given by  $\alpha f_1 \pm \beta f_2$ , where  $\alpha$  and  $\beta$  are integer numbers. The

Fig. 5. Picture of the Class-D amplifier detailing the drivers and switches.

Fig. 6. Theoretical spectra of the unquantized (blue) and quantized (red) test signal for IMD measurement.

order of any particular IMD product is  $\alpha+\beta$ . The most common IMD measurement standards are CCIF (twin-tone test) and SMPTE/DIN. The SMPTE/DIN IMD standard specifies a low-frequency, high-amplitude tone linearly combined with a high-frequency tone at 1/4 the amplitude (-12.04 dB) of the low-frequency tone. The DIN specification allows for several choices for both low and high frequencies, being 250 Hz and 8 kHz the most commonly used. The advantage of using this stimulus signal is that several IMD products fall within the audio band.

Fig. 6 shows the spectrum that results from the numerical simulation of the discrete-time modulator, for both infinite precision (blue line) and 11.9 bits quantization of the duty cycle (red line). The quantization process increases the noise floor such as predicted by (10). However, the baseband is free from intermodulation components.

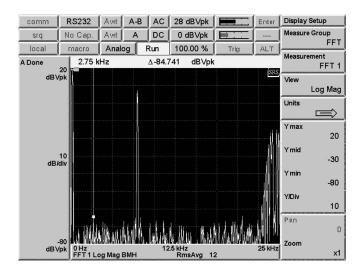

The actual spectrum of the signal measured at the output of the Class-D amplifier (without dithering) is shown in Fig. 7. The spectrum shows spikes harmonically related with the input tones and its combinations, revealing the deleterious effects of direct quantization of the duty cycles on the output spectrum.

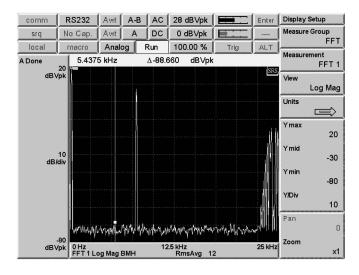

The positive impact of dithering is revealed in Fig. 8 that shows the spectrum of the same signal when dithering is applied by the DSP before quantization. A flat noise-floor is achieved,

Fig. 7. IMD test: spectrum of the amplifier's output with no dithering of the duty cycles.

Fig. 8. MD test: spectrum of the amplifier's output for dithered duty cycles.

entirely in agreement with the numerical simulations shown in Fig. 6. The theoretical SNR of 90.39 dB achievable for a full-swing input signal (i.e., with  $\Delta[n]$  varying between 0% and 100%) is reduced to 88.6 dB. This difference of 1.73 dB results from limiting the duty cycle variations in the actual modulator between 2.2% and 97.8% for safety reasons.

# B. Total Harmonic Distortion (THD) Measurement

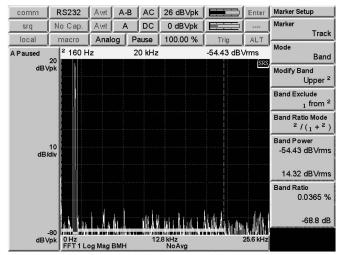

The THD measurements are used to analyze the linearity of the amplifier under test. The stimulus signal is composed of a single, spectrally pure tone. The nonlinear behavior of the amplifier is revealed by the appearance of harmonic components at its output. The THD is defined as the quotient of the power of the harmonics and the power of the test tone. In most practical situations it is difficult to isolate the harmonics individually, being THD + N computed instead. For THD + N a narrow band  $B_1$  is defined around the frequency of the test tone. A second band  $B_2$  includes the full audio bandwidth of the amplifier except  $B_1$ . The THD + N is computed as the quotient of the power in  $B_2$  to the power in  $B_1$ .

Fig. 9. Spectrum of the test tone for THD + N measurement at the output of the amplifier.

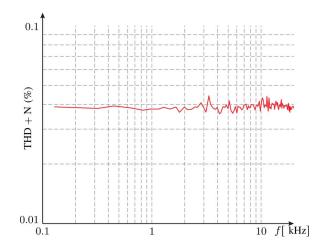

Fig. 10. THD + N as a function of the frequency of the input signal.

The THD + N is measured for a set of modulating signals of different frequencies. For each frequency point, a table of duty cycles  $\Delta[n]$  is computed and downloaded to the DSP. The distortion is measured specifying the bands  $B_1$  and  $B_2$  in the spectral analyzer. Fig. 9 shows the spectrum measured for a sinusoidal of 1792 Hz, generated with one of the test tables. A small band labeled 1 (solid lines) around the test tone defines  $B_1$ . A large band labeled 2 (dashed lines) which includes the full audio band and excludes  $B_1$  defines  $B_2$ . The resulting THD + N can be read at the bottom right of the figure, being 0.0365% (-68.8 dB) in this case.

This procedure is repeated for sinusoidal signals of different frequencies, and the results are collected in Fig. 10 that shows the THD + N as a function of the frequency. The THD + N exhibits a flat characteristic over the entire audio band, with a mean of 0.039065% and minimum and maximum values equal to 0.0359 and 0.0442%, respectively.

A comparison of the proposed amplification system with similar state-of-the-art implementations is summarized in Table I. For the sake of comparison, only those with digital input are included. Although THD + N is less than 0.1% for all the commercial systems, that value is measured using a 1 kHz

|                      | Input Type | Open/Closed<br>Loop | Max Output<br>Power (W) | Load<br>Impedance (Ω) | Supply<br>Voltage (V) | THD+N (%) | Switching<br>Freq. (kHz) |

|----------------------|------------|---------------------|-------------------------|-----------------------|-----------------------|-----------|--------------------------|

| TAS5704 [45]         | $I^2S$     | Closed              | 20                      | 4                     | 10–26                 | 0.03      | 384                      |

| TAS5721 [45]         | $I^2S$     | Open                | 15                      | 4                     | 8–26                  | 0.07      | 384                      |

| TAS5508+TAS5162 [45] | $I^2S$     | Closed              | 200                     | 6                     | 10.8-13.32            | 0.09      | 384                      |

| TAS5518+TAS5612 [45] | $I^2S$     | Closed              | 125                     | 4                     | 10.8-13.32            | 0.03      | 384                      |

| MAX98355 [46]        | PCM        | Open                | 3.2                     | 4                     | 2.5–5.5               | 0.02      | 300                      |

| MAX98356 [46]        | PDM        | Open                | 3.2                     | 4                     | 2.5-5.5               | 0.02      | 300                      |

| Proposed             | PCM        | Open                | 16                      | 4                     | 5–12                  | 0.04      | 40                       |

TABLE I

COMPARISON OF THE PROPOSED SYSTEM WITH STATE-OF-THE-ART COMMERCIAL ICS OF SIMILAR CHARACTERISTICS

sinusoidal modulating signal at 1 W output power. The data sheets show that THD + N increases with the modulating frequency. However, the click-modulator achieves a flat THD + N for the entire audio band (see Fig. 10). The table also reveals that it achieves a similar values of THD + N using a switching frequency that is 10 times lower than that of competing systems, increasing the efficiency of the stage and reducing the speed requirements of the drivers and switches.

#### IV. CONCLUSION

In this paper, a Class-D amplifier based on a discrete-time version of the click modulator was presented. Although the method resembles the ideas of the continuous-time click modulator, this architecture exploits the advantages of discrete-time processing tools requiring neither interpolation nor approximation to process the signal. The input to the algorithm is a discrete-time sequence and the output are the pulse widths of the binary waveform. The power stage was driven by a standard DSP frequently used for motor control applications.

The computation is carried out completely in the frequency domain, including zero-crossing detection. The aliasing problems reported in previous versions of the discrete-time click modulator are avoided by using the DT-AEMF method, that is based on grouping the AEM and LPF of the original click modulator in one single processing block. On the other hand, zero-crossings were obtained by means of a novel method that uses frequency information, allowing a very low sampling frequency compared to polynomial interpolation.

Quantization of the duty cycles is the main responsible of the resulting noise floor at the output of the amplifier. Dithering was proven useful to reduce the spikes in the frequency response, allowing to obtain a flat noise floor. Although the overall noise floor is augmented by an amount proportional to the variance of the random process, its flat characteristic remains close to the theoretically maximum achievable SNR.

The zero in-band distortion is revealed by the IMD test, that did not show any noticeable intermodulation product falling within the audio band. The THD + N remains almost flat for the entire audio band with variations less than 0.04% with a switching frequency around 40 kHz.

Although this work focuses on audio applications, the same ideas can be used with slight hardware modifications for high-power, high-quality and high-efficiency signal generation using switching stages.

### REFERENCES

- [1] C. Buccella, C. Cecati, and H. Latafat, "Digital control of power converters—A survey," *IEEE Trans. Ind. Informat.*, vol. 8, no. 3, pp. 437–447, Aug. 2012.

- [2] J. Álvarez, O. López, F. D. Freijedo, and J. Doval-Gandoy, "Digital parameterizable VHDL module for multilevel multiphase space vector PWM," *IEEE Trans. Ind. Electron.*, vol. 58, no. 9, pp. 3946–3957, Sep. 2011.

- [3] N. Milivojevic, M. Krishnamurthy, Y. Gurkaynak, A. Sathyan, Y. J. Lee, and A. Emadi, "Stability analysis of FPGA-based control of brushless DC motors and generators using digital PWM technique," *IEEE Trans. Ind. Electron.*, vol. 59, no. 1, pp. 343–351, Jan. 2012.

- [4] A. Sathyan, N. Milivojevic, Y. J. Lee, A. Krishnamurthy, and M. Emadi, "An FPGA-based novel digital PWM control scheme for BLDC motor drives," *IEEE Trans. Ind. Electron.*, vol. 56, no. 8, pp. 3040–3049, Aug. 2009.

- [5] T. D. Nguyen, J. Hobraiche, N. Patin, G. Friedrich, and J. P. Vilain, "A direct digital technique implementation of general discontinuous pulse width modulation strategy," *IEEE Trans. Ind. Electron.*, no. 9, pp. 4445– 4454, Sep. 2011.

- [6] S. Pan, J. Pan, and Z. Tian, "A shifted SVPWM method to control DC-link resonant inverters and its FPGA realization," *IEEE Trans. Ind. Electron.*, vol. 59, no. 9, pp. 3383–3391, Sep. 2012.

- [7] E. R. C. Da Silva, E. C. Dos Santos, Jr., and C. B. Jacobina, "Pulsewidth modulation strategies," *IEEE Ind. Electron. Mag.*, vol. 5, no. 2, pp. 37–45, Jun. 2011.

- [8] Z. Song and D. V. Sarwate, "The frequency spectrum of pulse modulated signals," *Signal Process.*, vol. 83, no. 10, pp. 2227–2258, Oct. 2003.

- [9] M. Yang and J. H. Oh, "Adaptive predistortion filter for linearization of digital PWM power amplifier using neural networks," presented at the Proceedings of the 113th AES Convention, Los Angeles, CA, USA, Oct. 2002, Paper 5657. [Online]. Available: http://www.aes.org/e-lib/ browse.cfm?elib=11280

- [10] F. Chierchie, A. Soto, E. Paolini, and A. Oliva, "Real-time low-distortion digital PWM modulator for switching converters," *Int. Rev. Elect. Eng.*, vol. 7, no. 5, pp. 5348–5358, Sep. 2012.

- [11] P. Midya, B. Roeckner, and S. Bergstedt, "Digital correction of PWM switching amplifiers," *IEEE Power Electron. Lett.*, vol. 2, no. 2, pp. 68– 72, Jun. 2004.

- [12] P. Midya, B. Roeckner, and T. Paulo, "High performance digital feed-back for PWM digital audio amplifiers," presented at the Proceedings of the 121st AES Convention, San Francisco, CA, USA, Oct. 2006, Paper 6862.

- [13] P. Midya, B. Roeckner, and T. Paulo, "Recursive natural sampling for digital PWM," presented at the Proceedings of the 123rd AES Convention, New York, NY, USA, Oct. 2007, Paper 7228.

- [14] S. C. Huerta, A. de Castro, O. Garcia, and J. A. Cobos, "FPGA-based digital pulsewidth modulator with time resolution under 2 ns," *IEEE Trans. Power Electron.*, vol. 23, no. 6, pp. 3135–3141, Nov. 2008.

- [15] M. G. Batarseh, W. Al-Hoor, L. Huang, C. Iannello, and I. Batarseh, "Window-masked segmented digital clock manager-FPGA-based digital pulsewidth modulator technique," *IEEE Trans. Power Electron.*, vol. 24, no. 11, pp. 2649–2660, Nov. 2009.

- [16] A. De Castro and E. Todorovich, "High resolution FPGA DPWM based on variable clock phase shifting," *IEEE Trans. Power Electron.*, vol. 25, no. 5, pp. 1115–1119, May 2010.

- [17] J. de la Rosa, "Sigma-Delta modulators: Tutorial overview, design guide, and state-of-the-art survey," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 1, pp. 1–21, Jan. 2011.

- [18] M. Hawksford, "Modulation and system techniques in PWM and SDM switching amplifiers," *J. Audio Eng. Soc.*, vol. 54, no. 3, pp. 107–139, Mar. 2006.

- [19] H. His and C. Dufaza, "Digital-input Class-D audio amplifier," presented at the Proceedings of the 128th AES Convention, London, U.K., May 2010, Paper 8128.

- [20] M. Hawksford, "SDM versus PWM Power Digital-to-Analogue Converters (PDAC) in high-resolution digital audio applications," presented at the Proceedings of the 118th AES Convention, Barcelona, Spain, May 2005, Paper 6471.

- [21] R. Esslinger, G. Gruhler, and R. Stewart, "Digital audio power amplifiers using Sigma Delta modulation: Linearity problems in the Class-D power stage," presented at the Proceedings of the 110th AES Convention, Amsterdam, The Netherlands, May 2001, Paper 5400.

- [22] R. Esslinger, G. Gruhler, and R. Stewart, "Sigma-Delta modulation in digital Class-D power amplifiers: Methods for reducing the effective pulse transition rate," presented at the Proceedings of the 112th AES Convention, Munich, Germany, May 2002, Paper 5634.

- [23] J. A. S. Angus, "The practical performance limits of multi-bit Sigma-Delta modulation," presented at the Proceedings of the 110th AES Convention, Amsterdam, The Netherlands, May 2001, Paper 5394.

- [24] E. Gaalaas, B. Liu, N. Nishimura, R. Adams, and K. Sweetland, "Integrated stereo  $\Delta\Sigma$  Class D amplifier," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2388–2397, Dec. 2005.

- [25] E. Gaalaas, B. Y. Liu, N. Nishimura, R. Adams, K. Sweetland, and R. Morajkar, "Integrated stereo ΣΔ Class D amplifier," presented at the Proceedings of the 118th AES Convention, Barcelona, Spain, May 2005, Paper 6452

- [26] L. Dooper and M. Berkhout, "A 3.4 w digital-in Class-D audio amplifier in 0.14 μm CMOS," *IEEE J. Solid-State Circuits*, vol. 47, no. 7, pp. 1524– 1534, Jul. 2012.

- [27] B. F. Logan, Jr., "Click modulation," Bell Lab. Tech. J., vol. 63, no. 3, pp. 401–423, Mar. 1984.

- [28] M. Streitenberger, H. Bresch, and W. Mathis, "A new concept for high performance Class-D audio amplification," presented at the Proceedings of the 106th AES Convention, Munich, Germany, May 1999, Paper 4941.

- [29] M. Streitenberger and H. Bresch, "First implementation of a Class-D amplifier with separated baseband," in *Proc. Int. Symp. Theor. Elect. Eng.*, Sep. 1999, pp. 157–163.

- [30] M. Streitenberger, H. Bresch, J. Kaszubiak, and T. Schindler, "A novel approach to high speed digital pulse-formers based on ring oscillators for PWM and Class-D applications," presented at the Proceedings of the 112nd AES Convention, Munich, Germany, 2002, Paper 5632.

- [31] M. Streitenberger, H. Bresch, and W. Mathis, "Theory and implementation of a new type of digital power amplifier for audio applications," in *Proc. IEEE ISCAS*, May 2000, pp. 511–514.

- [32] M. Streitenberger, F. Felgenhauer, H. Bresch, and W. Mathis, "Class-D audio amplifiers with separated baseband for low-power mobile applications," in *Proc. IEEE ICCSC*, Jun. 2002, pp. 186–189.

- [33] M. Streitenberger, F. Felgenhauer, H. Bresch, and W. Mathis, "Zero-position coding with separated baseband in low-power Class-D audio amplifiers for mobile communications," in *Proc. Int. Conf. TELSIKS Telecommun. Modern Satellite, Cable Broadcast. Service*, Nis, Yugoslavia, Sep. 2001, vol. 2, pp. 567–570.

- [34] M. Streitenberger, F. Felgenhauer, H. Bresch, and W. Mathis, "Zero Position Coding (ZePoC)—A generalised concept of pulse-length modulated signals and its application to Class-D audio power amplfiers," presented at the Proceedings of the 110th AES Convention, Amsterdam, The Netherlands, May 2001, Paper 5365.

- [35] M. Streitenberger and W. Mathis, "A novel coding topology for digital Class-D audio power amplifiers with very low pulse-repetition rate," in *Proc. 28th ESSCIRC*, Sep. 2002, pp. 515–518.

- [36] L. Stefanazzi, E. Paolini, and A. Oliva, "Click modulation: An off-line implementation," in *Proc. 51st MWSCAS*, 2008, pp. 946–949.

- [37] K. P. Sozanski, "A digital click modulator for a Class-D audio power amplifier," in *Proc. Signal Process. Algorithms, Architect., Arrangements Appl.*, 2009, pp. 121–126.

- [38] L. Stefanazzi, A. R. Oliva, and E. E. Paolini, "Alias-free digital click modulator," *IEEE Trans. Ind. Informat.*, vol. 9, no. 2, pp. 1074–1083, May 2013.

- [39] B. Widrow and I. Kollár, Roundoff Error in Digital Computation, Signal Processing, Control, and Communications. Cambridge, U.K.: Cambridge Univ. Press, 2008.

- [40] A. V. Oppenheim and R. W. Schafer, *Discrete-Time Signal Processing*, 3rd ed. Upper Saddle River, NJ, USA: Prentice-Hall, 2009.

- [41] A. Devices, The Data Conversion Handbook, W. Kester, Ed. Boston, MA, USA: Newnes, 2004.

- [42] F. Chierchie and E. Paolini, "Analytical and numerical analysis of deadtime distortion in power inverters," in *Proc. EAMTA Argentine School Micro-Nanoelectron. Technol. Appl.*, Montevideo, Uruguay, Oct. 2010, pp. 6–11.

- [43] F. Chierchie and E. Paolini, "Quasi-analytical spectrum of PWM signals with dead-time for multiple sinusoidal input," in *Proc. IEEE ISCAS*, Rio de Janeiro, Brazil, May 2011, pp. 1033–1036.

- [44] F. Chierchie, L. Stefanazzi, E. Paolini, and A. Oliva, "Frequency analysis of PWM inverters with dead-time for arbitrary modulating signals," *IEEE Trans. Power Electron.*, to be published. [Online]. Available: http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=6572859&isnumber=4359240

- [45] Texas Instruments Audio. [Online]. Available: http://www.ti.com

- [46] Maxim Integrated Audio Products. [Online]. Available: http://www.maximintegrated.com/

**Leandro Stefanazzi** received the B.S. degree in electronic engineering, the M.S. degree in control systems, and the Ph.D. degree from Universidad Nacional del Sur, Bahía Blanca, Argentina, in 2006, 2008, and 2013, respectively.

From June 2009 to November 2010, he joined the Electronics and Information Technology Laboratory of the French Atomic Energy Commission (CEA-LETI) as a research engineer. His research interests are digital signal processing and power electronics.

**Fernando Chierchie** (M'10) received the B.S. degree in electronic engineering and the M.S. degree in control systems both from Universidad Nacional del Sur, Bahía Blanca, Argentina, in 2009 and 2011, respectively.

He is a Teaching Assistant at Universidad Nacional del Sur. His research interests are switching amplifiers, signal processing, power electronics and DSP implementations of digital control, and signal processing algorithms.

**Eduardo E. Paolini** received the BSEE degree from the Universidad Nacional del Sur, Bahía Blanca, Argentina, in 1987.

He is Adjunct Professor at Universidad Nacional del Sur since 1998 and a member of Comisión de Investigaciones Científicas de la Provincia de Buenos Aires (CIC), Buenos Aires, Argentina, since 2011. His research interests are digital signal processing, and switched and nonlinear systems.

power management.

**Alejandro R. Oliva** received the BSEE degree from the Universidad Nacional del Sur, Bahía Blanca, Argentina, in 1987, and the M.S. and Ph.D. degrees in electrical engineering from the University of Arkansas at Fayetteville, AK, USA, in 1996 and 2004, respectively.

He is a Professor at the Department of Electrical Engineering of the Universidad Nacional del Sur. Since 2005 he is a member of Consejo Nacional de Investigaciones Científicas y Técnicas (CONICET). His main research interests are power electronics and