## Power Semiconductor Devices - Silicon vs. New Materials

Jim Plummer Stanford University IEEE Compel Conference July 10, 2017

- Market Opportunities for Power Devices

- Materials Advantages of SiC and GaN vs. Si

- Si Power Devices The Dominant Solution Today

- Current Status of GaN and SiC Power Switches

- Will GaN and SiC really capture a large part of the power switch market?

- What Are the Big Challenges/Opportunities Going Forward?

- Conclusions. Stanford ENGINEERING

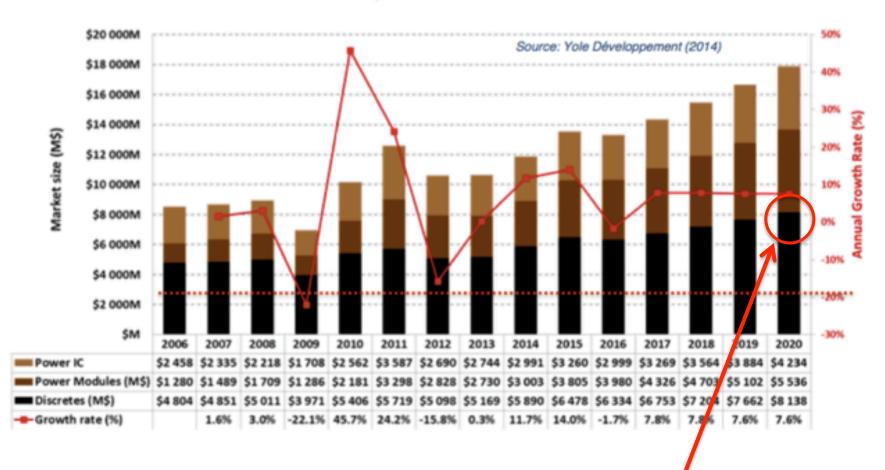

#### **Estimated Overall Power Device Market**

#### 2006-2020 power device market size

Overall discrete device market estimated at \$8B in 2020.

## Estimated Overall WBG Power Device Market

These projections suggest WBG devices will have < 10% of the discrete market in 2020. If they have much higher performance, WHY?

### Power Devices - Silicon vs. New Materials

|                                                              | Si        | GaAs            | GaN          | 4H-SiC    |

|--------------------------------------------------------------|-----------|-----------------|--------------|-----------|

| Bandgap energy (eV)                                          | 1.12      | 1.4             | 3.49         | 3.26      |

| Breakdown field (MV/cm)                                      | 0.3       | 0.4             | 3.5          | 3         |

| Electron mobility at 300 K (cm²/V·s)                         | 1400      | 8500<br>*10,000 | 900<br>*2000 | 700       |

| Saturated (peak) electron velocity<br>(10 <sup>7</sup> cm/s) | 1.0 (1.0) | 1.3 (2.1)       | 1.3 (2.7)    | 2.0 (2.0) |

| Relative dielectric constant                                 | 11.8      | 12.8            | 9            | 10        |

| Thermal conductivity (W/cm·K)                                | 1.5       | 0.5             | 1.7          | 3.5       |

| Thermal expansion (10-6/K)                                   | 2.6       | 5.7             | 5.6          | 5.1       |

| Lattice constant (Å)                                         | 5.43      | 5.65            | 3.19         | 3.07      |

\* Values of corresponding heterostructures.

(F. lacopi et al., MRS Bulletin, May 2015, pg. 390)

The opportunity for major advances occurs primarily because of the higher bandgap and breakdown fields in GaN and SiC.

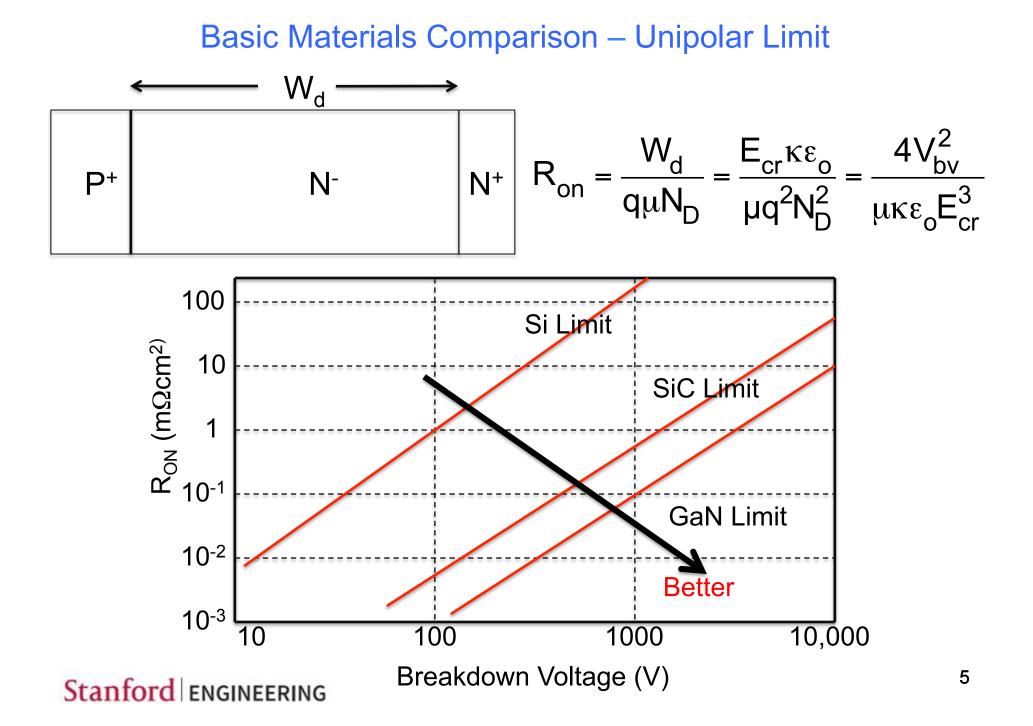

# **Basic Materials Comparison**

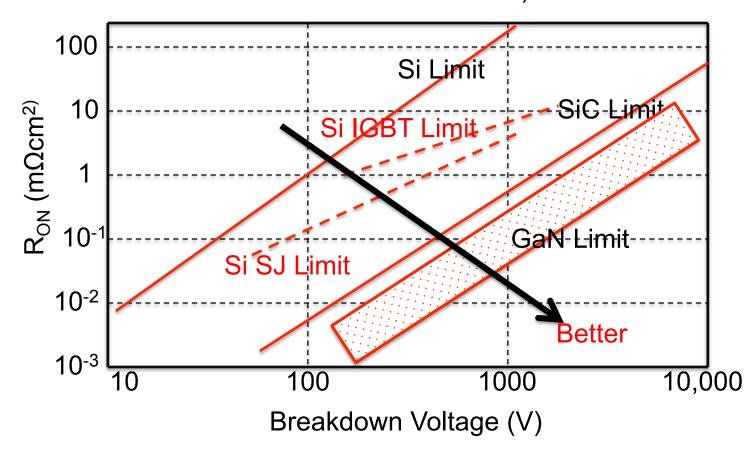

But in reality, the situation is more complicated.

- More sophisticated Si devices than simple unipolar MOSFETs.

- GaN limit depends on µ: > 2000 cm<sup>2</sup>/Vsec HEMT,

≈ 1600 Bulk, < 200 MIS</li>

Stanford ENGINEERING

(IGBT limit – A Nakagawa (Toshiba), ISPSD 2006) 6

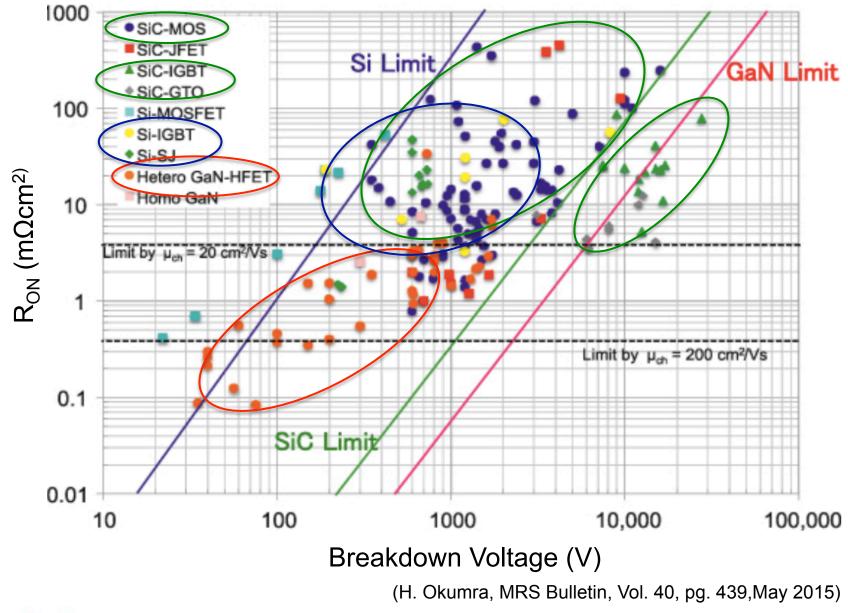

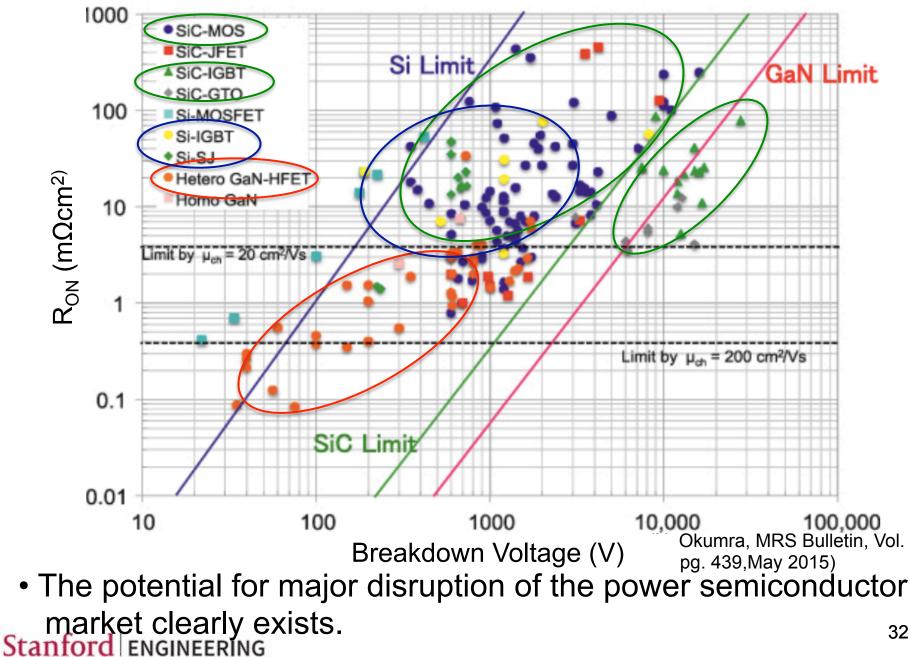

#### **Experimental Data**

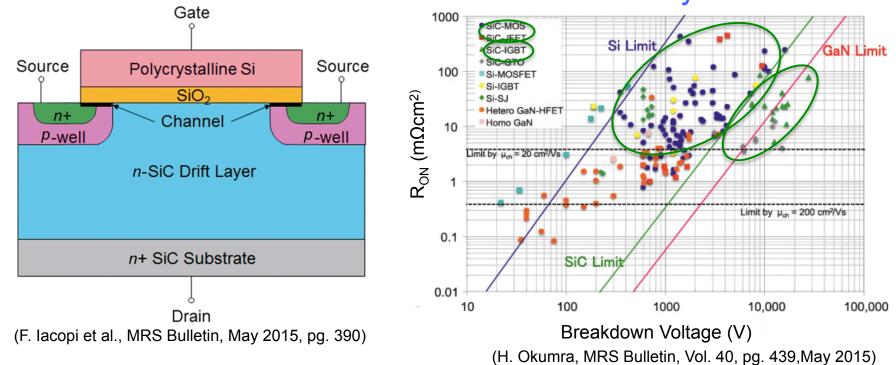

# Observations

- 1. Silicon devices (IGBTs, superjunction devices) are significantly better than the unipolar Si "material limit".

- Low voltage SiC MOSFETs are ≈ same as Si MOSFETs. High voltage SiC MOSFETs are much better than Si. SiC IGBTs break the SiC unipolar "material limit" just as Si IGBTs break the Si limit.

- 3. GaN experimental results are all < 600V and are well below the material limits expected for GaN but they do achieve the lowest  $R_{ON}$ .

- 4. And then, of course, there are cost, reliability, plug in replacement . . . . issues to deal with.

First let's look at the silicon competition Stanford ENGINEERING

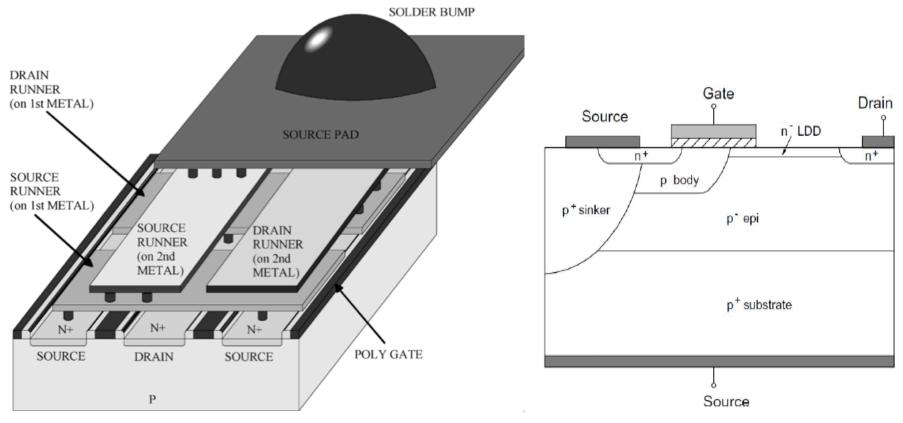

### Low Voltage Si Power Devices: NMOS or LDMOS ≤ 20 Volts

**Figures** : Z.John Chen et.al. IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 21, NO. 1, JANUARY 2006 p. 11-17

DMOS – Double diffused MOSFET

Conventional planar, lateral Si MOS devices. Cost reductions through manufacturing efficiencies. Mostly older nodes. CHEAP!

#### Moderate Voltage Si Power Devices: Vertical UMOS 15 - 200 Volts

Basic structure unchanged in many years. Cost reductions through manufacturing efficiencies. Mostly older nodes. CHEAP! Stanford ENGINEERING

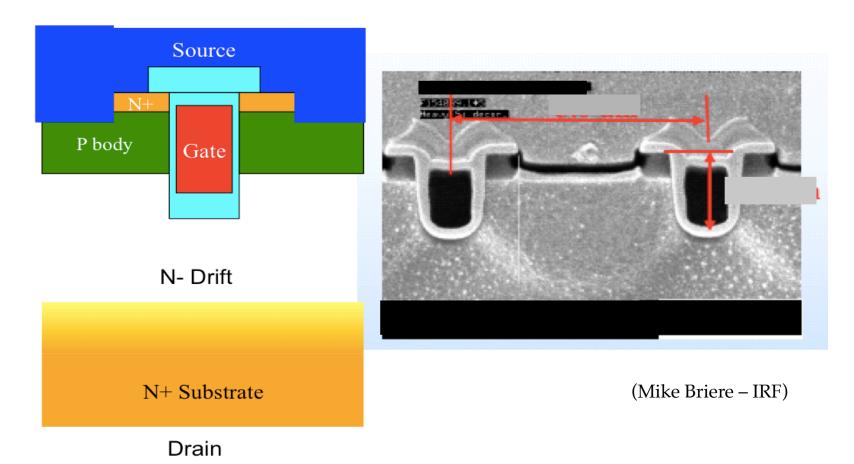

#### Silicon Trench Power IGBT 200 – 1200 Volts

(Mike Briere – IRF)

Basic structure unchanged in many years. Cost reductions through manufacturing efficiencies. Mostly older nodes. CHEAP! Stanford ENGINEERING

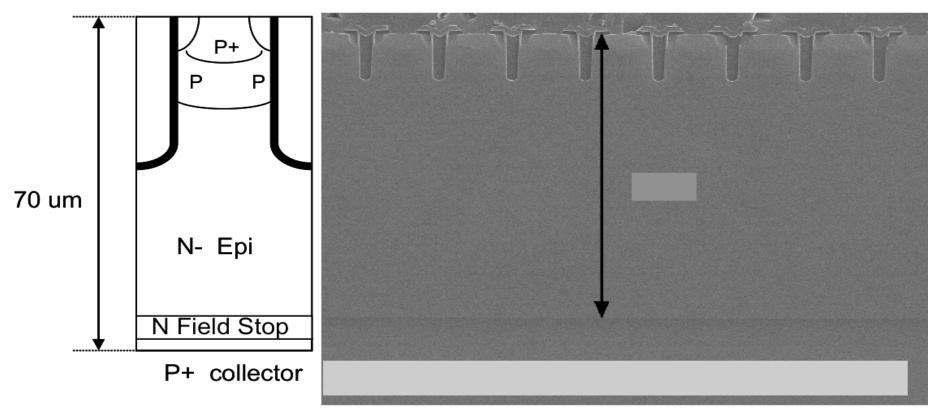

# IGBT – Insulated Gate Bipolar Transistor

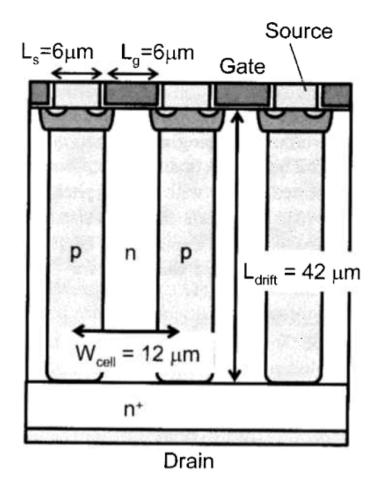

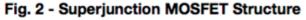

#### Superjunction Vertical MOSFET 100 – 1000 Volts

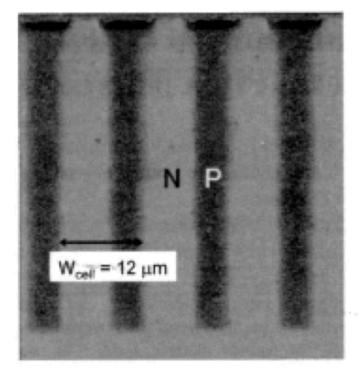

Fig. 2 SCM image of the fabricated SJ-MOSFET with the lateral pitch of 12 µm.

W. Saito et.al. (Toshiba) ISPSD 2004 p. 293

#### Stanford ENGINEERING

ISPSD 2004 p 293 13

1

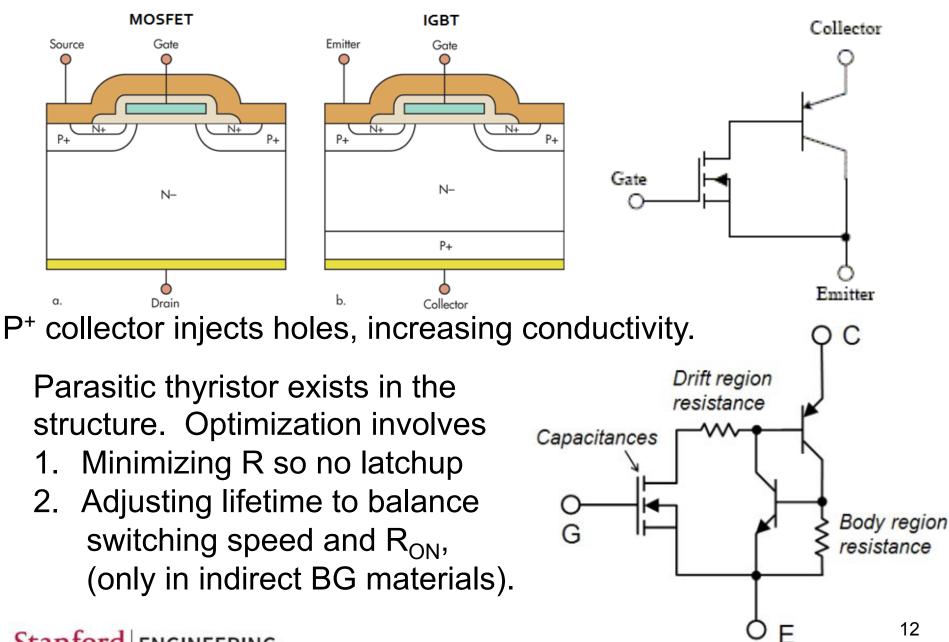

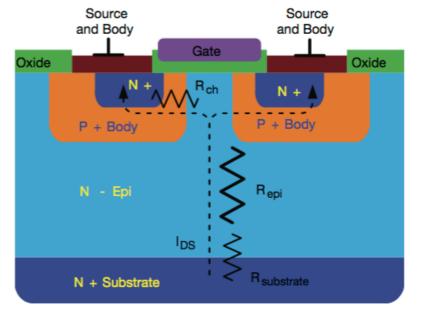

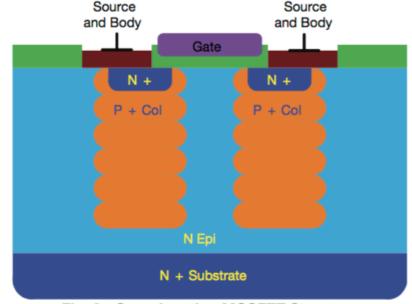

# Superjunction MOSFET

Fig. 1a - Conventional Planar MOSFET Structure

(Vishay Siliconix App. Note AN849)

- In a conventional power MOSFET, V<sub>dd</sub> depletes N<sup>-</sup> epi vertically. Increasing BV ⇒ thicker epi and lighter epi doping.

- In a superjunction power MOSFET, the N epi is fully depleted and charge balance occurs with P<sup>+</sup> columns. BV is proportional to epi thickness and N epi can be more heavily doped decreasing R<sub>epi</sub>.

### Will Silicon Power Devices Continue to Improve?

- The basic observation is often that Si power devices are "mature" and thus won't get much better.

- But because Si is the basis of the electronics industry, many \$B in R&D continue to be spent each year. Some of this investment will likely result in Si power device improvements.

- Si will likely always be much better at integrating control with power devices. So major parts of the power market are simply not addressable by SiC and GaN at least in monolithic form.

- Cost will always be lower for Si power devices so cost sensitive applications will continue to use Si whenever possible.

- Bottom line Si isn't going away. So what are the opportunities for SiC and GaN?

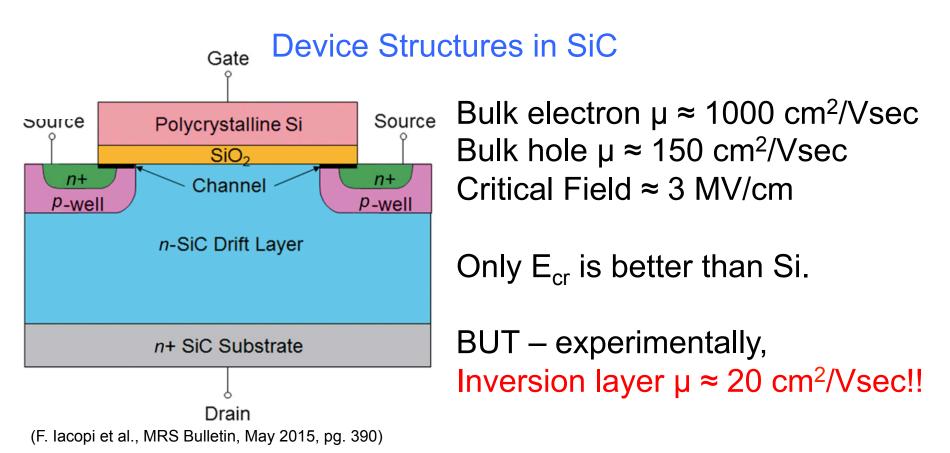

- Primarily vertical MOSFET structures similar to Si.

- Low V SiC MOSFETs ≈ same as Si (because of low channel μ). High V devices much better than Si.

- Vertical IGBT devices similar to Si structures, but beat Si in performance at high voltages.

• 6" SiC wafers are available, but expensive. Stanford ENGINEERING

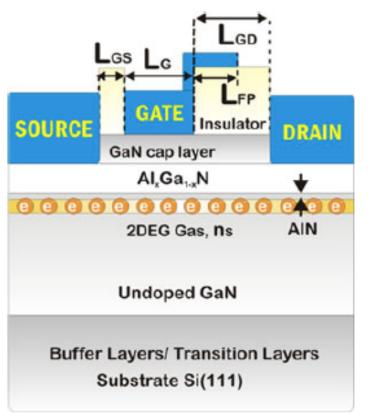

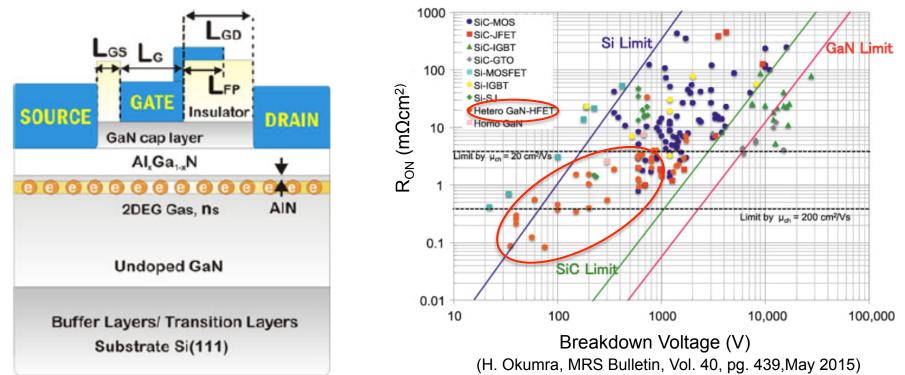

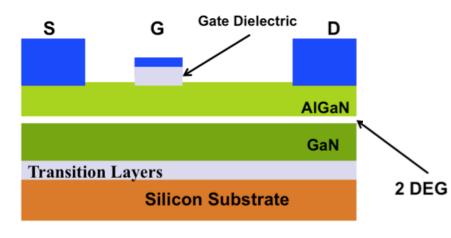

### **Device Structures in GaN**

Bulk electron  $\mu \approx 1600 \text{ cm}^2/\text{Vsec}$ 2DEG electron  $\mu \approx 2000 \text{ cm}^2/\text{Vsec}$ Bulk hole  $\mu \approx 175 \text{ cm}^2/\text{Vsec}$ Critical Field  $\approx 3.5 \text{ MV/cm}$

$E_{cr}$  is much better than Si. 2DEG  $\mu$  is better than Si.

BUT – normally OFF devices have lower performance.

- Heteroepitaxy on Si, SiC limits GaN to lateral devices, < 1000 V.

- Basic device is depletion mode (normally ON).

- No large diameter GaN wafers available.

# What Limits Adoption Rate of New Power Devices?

- First, quality, reliability and robustness must be demonstrated or there is no product, only a science project!

- Governing metric for market adoption = Performance/cost = P/C.

- For power semiconductors,

$P/C = (conduction loss)^{-1}(switching loss)^{-1}/Cost$

- For new switching materials/technologies, to displace Si in an existing application

- If P/C  $\leq$  1, niche market

- If P/C > 2-3X, widespread adoption

Opportunities:

- Replace Si in existing applications either P needs to be higher or C needs to be lower to achieve P/C > 2-3X.

- Enable new applications currently not achievable with Si.

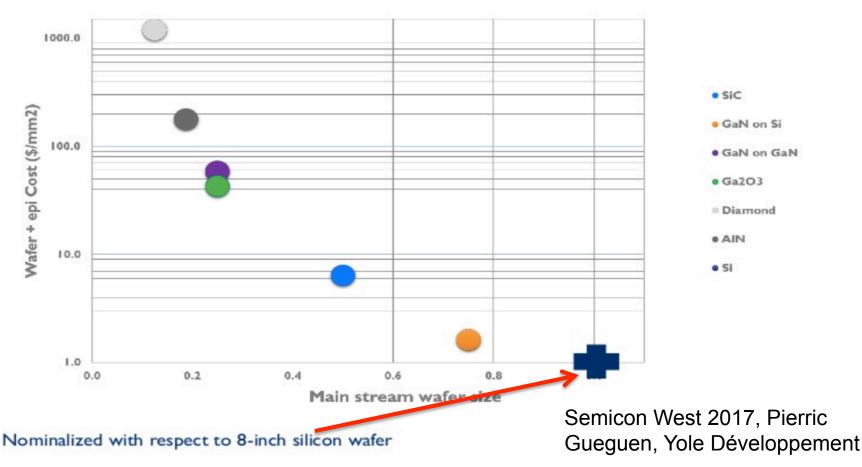

## **Cost of Wafer Substrates**

- Neither SiC nor GaN have a cost advantage with respect to silicon today, largely because of wafer costs.

- GaN may reach ≈ parity soon (because it's on a Si wafer!)

- But these numbers don't give GaN or SiC a P/C advantage. Stanford ENGINEERING

### What's Needed To Increase Market Penetration by SiC Devices?

- SiC devices are often derated for reliability or material defect reasons, but still offer large performance advantages over Si.

- Material defect issues include micropipes and dislocations.

- Cost remains an issue 6" SiC substrates are available but \$\$.

- SiC/SiO<sub>2</sub> interface not as good as Si/SiO<sub>2</sub> interface. ∴ lower µ than might be possible. ∴ Only high V SiC MOSFETs > Si.

# What's Needed To Increase Market Penetration by SiC Devices?

- Much progress has been made in reducing SiC crystal defects in substrates and in epi layers. But the quality is not nearly as good as Si wafers.

- The SiC/insulator interface still needs to be significantly improved to reduce interface states. Current low μ limits SiC MOSFETs to high voltage applications. In low V devices, the 10X smaller SiC channel μ mitigates SiC's ε<sub>CR</sub> 10X advantage.

- Manufacturing costs are much higher than Si. A significant component of this cost is the starting wafer cost.

So currently P/C is not > 2-3X silicon and SiC is largely addressing markets where Si cannot compete or which are not cost sensitive and these markets are not huge!

# What's Needed To Increase Market Penetration by GaN Devices?

- GaN devices are primarily lateral HEMTs. This limits GaN applications to < 1000V. Most devices are far below GaN limit.</li>

- Intrinsic device is normally ON.

need Si MOSFET in a cascode configuration, or modified GaN gate structure which can degrade performance.

• Reliability issues remain with ON current collapse. Stanford ENGINEERING

# **Enhancement Mode GaN Devices**

What's Needed?

- $V_T > 2$  volts

- $V_G$  > 10 volts

- Cascode circuit with Si

MOSFET + GaN HEMT can achieve this.

Eliminate 2DEG under gate:

- Sub-critical barrier, e.g. recessed gate

- MOS-hybrid device

- Piezoelectric gate

- N-polar HEMT

- Lattice matched barrier (InAIN)

Negative charge between external gate electrode and 2DEG:

- PN junction (p GaN, p AlGaN under gate)

- Negative ions in insulator or barrier (e.g. F-)

- Trapped electrons in gate insulator (floating gate or SiN-SiO<sub>2</sub>)

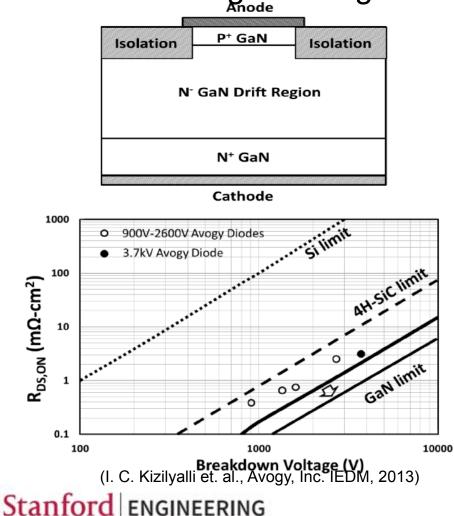

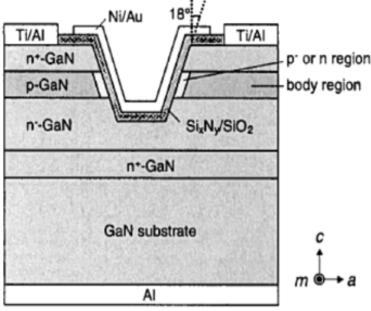

### Vertical GaN Devices Homoepitaxy Examples

The biggest challenge here is bulk GaN wafers. Only very small (2") wafers currently available and the wafer manufacturing challenges are formidable.

Fig. 2. Device structure of our trench gate MOSFET.

H. Otake et.al. APEX vol 1 (2008) p. 011105-1

# What's Needed To Increase Market Penetration by GaN Devices?

- Much progress has been made in reducing crystal defects in GaN epi layers grown on Si. But the quality is not nearly as good as Si wafers. Si substrates are likely the best route to reduce lateral GaN HEMT manufacturing costs.

- Enhancement mode device structures need further development.

- Reliability, ON current collapse after high reverse bias, need further investigation.

- A breakthrough is needed in producing GaN bulk substrates.

So currently P/C is not > 2-3X silicon and GaN is largely addressing markets where Si cannot compete or which are not cost sensitive and these markets are not huge!

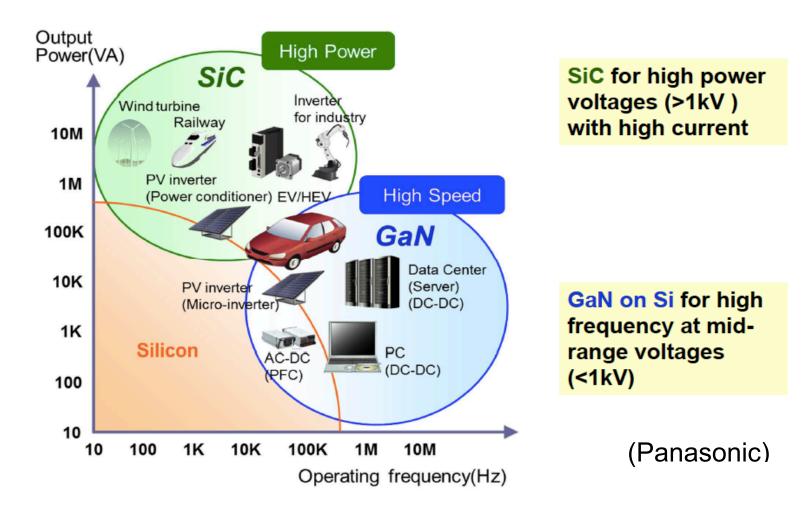

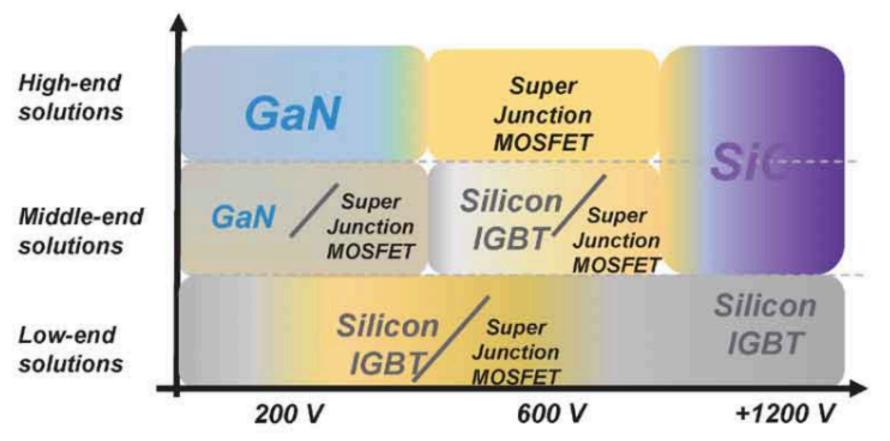

## Current Market Opportunities for Gan and SiC

Given the current limitations of Gan and SiC in P/C, most applications are in regions where Si cannot compete. Stanford ENGINEERING

# The Situation Today

- GaN and SiC have very clear materials advantages over Si.

- In principle they allow power electronic components to be faster, smaller, more efficient and more reliable than Si parts.

- In principle they allow devices to operate at higher voltages, higher temperatures and higher frequencies than Si devices.

- Yet their market penetration is very small today. Some market projections (Lux) suggest Si will still have 87% of the power device market in 2024.

- What needs to happen to change this? Will it change?

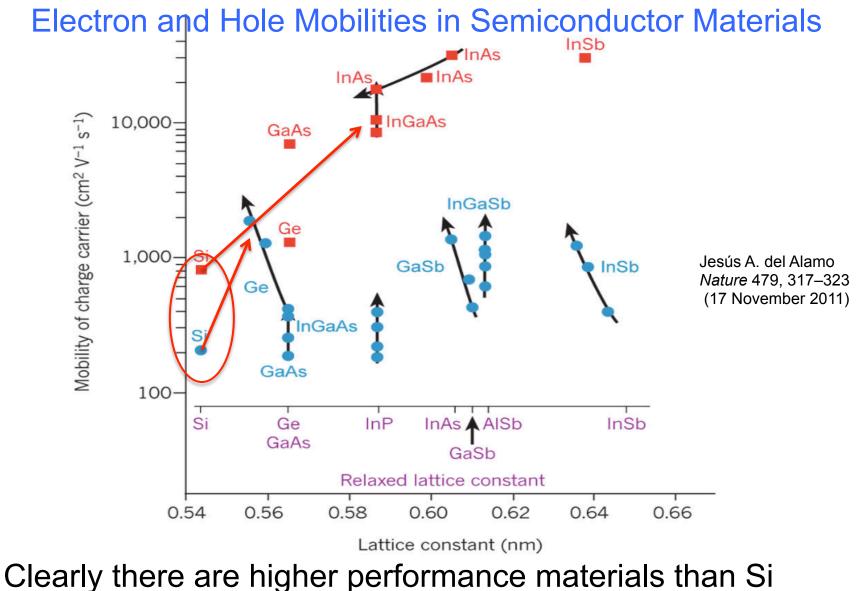

- Perhaps there are some lessons we can learn from Si CMOS.

for logic applications. > 10X improvement in  $\mu$  is possible. NMOS  $\longrightarrow$ InGaAs, PMOS  $\longrightarrow$ Ge. Stanford ENGINEERING

28

# Higher Performance Materials for CMOS Logic

- Many demonstrations of higher performance III-V logic devices over the past 20 years. Also many demonstrations integrating these devices in a Si CMOS process flow.

- Yet it is unlikely that this transition will ever take place. Performance/Cost ratio not sufficient to justify manufacturing.

- Si CMOS has many advantages that offset lower mobilities:

- "Ideal" semiconductor/insulator interfaces

- Decades of manufacturing experience, ... low cost

- Constant scaling, improving performance

- Well understood reliability issues

- III-V inversion layer  $\mu$  not as high as bulk  $\mu$ .

- etc., etc.

- Many of these same arguments apply to Si vs. GaN or SiC power devices, except for the item in red above.

Where Have Other Materials "Competed" With Si CMOS?

- III-V materials have other advantages besides  $\mu$ .

- Direct bandgaps.

- Higher frequency operation possible.

- So even though III-V materials have not (and likely will not) displace Si in digital logic, they have

- Dominated photonics markets where Si cannot compete.

- Dominated high frequency communications markets where CMOS is too slow. (This is a moving target!)

- What's the lesson for GaN and SiC?

- Look for markets Si power devices simply can't reach or which are not cost sensitive.

- Grow scale, establish reliability, gain acceptance in these markets.

- Drive manufacturing costs down through volume.

# Yole Développement Technology Forecast

- Similar to the Panasonic market projection slide shown earlier.

- Given the current limitations of Gan and SiC in P/C, most applications are in regions where Si cannot compete.

Stanford ENGINEERING

#### Conclusions

# Conclusions

- As long as costs are significantly higher for SiC and GaN, market share will be difficult to win in existing applications. P/C is critical. Cost parity with Si will likely only be achieved with significant market penetration (scale).

- New technologies usually create new markets before they displace existing technologies in established markets.

- Some existing applications are less cost sensitive (usually very high performance markets). These are likely targets for early adopters.

- R&D on new circuits/packages/systems and new applications may be as important as R&D on devices and technology.

Thank you.

**Questions?**