## Optimisation de la performance des applications de mémoire transactionnelle sur des plates-formes multicoeurs: une approche basée sur l'apprentissage automatique

Márcio Bastos Castro Castro

#### ▶ To cite this version:

Márcio Bastos Castro Castro. Optimisation de la performance des applications de mémoire transactionnelle sur des plates-formes multicoeurs : une approche basée sur l'apprentissage automatique. Autre [cs.OH]. Université de Grenoble, 2012. Français. NNT : 2012GRENM074 . tel-00766983

### HAL Id: tel-00766983 https://theses.hal.science/tel-00766983v1

Submitted on 19 Dec 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ DE GRENOBLE

## THÈSE

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Mathématiques-informatique

Arrêté ministérial : 7 août 2006

Présentée par

## Márcio BASTOS CASTRO

Thèse dirigée par Jean-François MÉHAUT

préparée au sein du Laboratoire d'Informatique de Grenoble et de l'École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

## Improving the Performance of Transactional Memory Applications on Multicores : A Machine Learning-based Approach

Thèse soutenue publiquement le **3 décembre 2012**, devant le jury composé de :

#### M. Philippe O. A. NAVAUX

Professeur, Universidade Federal do Rio Grande do Sul (UFRGS), Président **M. Pascal FELBER** Professeur, Université de Neuchâtel, Rapporteur **M. Raymond NAMYST** Professeur, Université de Bordeaux 1, Rapporteur **M. Miguel SANTANA** Directeur du centre IDTEC, STMicroelectronics, Crolles, Examinateur **M. Jean-François MÉHAUT** Professeur, Université de Grenoble - CEA, Directeur de thèse **M. Luiz Gustavo L. FERNANDES**

Professeur, Pontifícia Universidade Católica do Rio Grande do Sul (PUCRS), Co-Encadrant de thèse

# Acknowledgements

"When we least expect it, life sets us a challenge to test our courage and willingness to change; at such a moment, there is no point in pretending that nothing has happened or in saying that we are not yet ready. The challenge will not wait. Life does not look back. A week is more than enough time for us to decide whether or not to accept our destiny." — Paulo Coelho, The Devil and Miss Prym, 2000.

This extract from a book written by Paulo Coelho (a Brazilian novelist and one of the most widely read authors in the world) summarizes what happened in my life in early 2009. I had the opportunity to meet Jean-François Méhaut in Porto Alegre, Brazil. After a short presentation of the research I'd done during my Master's, Jean-François asked me if I would be interested in doing a Ph.D. in France. Deciding whether to do a Ph.D. in a foreign country is tough. It's a huge investment in terms of time and effort. It puts several technical and personal skills to the test such as the ability to: do good quality research, absorb a new culture, learn a foreign language and live far away from home. I accepted the challenge and it is with great happiness that I write these words to thank many people involved in that.

Firstly, I would like to thank my advisor Jean-François Méhaut, for accepting me as his Ph.D. student and for giving me the opportunity to prepare and write this thesis in France. You were always present to discuss about my research and to motivate me during all this time. I really appreciate your efforts to make collaborations with Brazilian universities. This is very important, since most of us (Brazilians) come back to Brazil after finishing the thesis. Thank you for giving me all the support I needed to participate and present my work in different conferences and also for putting me in contact with many people from the HPC community in France and abroad.

Secondly, I would like to thank all my friends and colleagues from Brazil (PUCRS, UFRGS, PUC Minas and USP) and France (LIG). Special thanks to my big friend Pedro Velho, who helped me a lot when I arrived in France as well as the people from Nanosim, Mescal and Moais research teams for the technical and personal discussions during these years. I really appreciated to share these moments with you!

Finally, I would like to thank my family for supporting me during all my life. A very special thank to my love, Evanaska, who always encouraged me and helped me in all possible ways to achieve this goal. I dedicate this achievement to you all.

*Muito obrigado!*

# Contents

| Lis | List of Figures v       |         |                                                   |    |

|-----|-------------------------|---------|---------------------------------------------------|----|

| Lis | List of Tables vii      |         |                                                   |    |

| Lis | List of Abbreviations i |         |                                                   | ix |

| 1   | Intro                   | oductio | n                                                 | 1  |

|     | 1.1                     | Resear  | ch issues                                         | 4  |

|     |                         | 1.1.1   | Understanding the performance of TM applications  | 4  |

|     |                         | 1.1.2   | Improving the performance of TM applications      | 5  |

|     | 1.2                     | Contri  | butions                                           | 7  |

|     | 1.3                     | Scient  | ific context of the thesis                        | 10 |

|     | 1.4                     | Thesis  | outline                                           | 11 |

| 2   | Back                    | ground  | đ                                                 | 13 |

|     | 2.1                     | Multic  | ore platforms                                     | 13 |

|     |                         | 2.1.1   | Architectural concept                             | 14 |

|     |                         | 2.1.2   | Performance of multicores                         | 14 |

|     |                         | 2.1.3   | Impacts of the memory hierarchy                   | 16 |

|     |                         | 2.1.4   | Synchronization of shared data                    | 18 |

|     | 2.2                     | Transa  | ctional memory                                    | 21 |

|     |                         | 2.2.1   | General concepts                                  | 21 |

|     |                         | 2.2.2   | Design choices                                    | 25 |

|     |                         | 2.2.3   | Implementation approaches                         | 27 |

|     |                         | 2.2.4   | Software transactional memory systems             | 29 |

|     | 2.3                     | Bench   | marks for evaluating transactional memory systems | 34 |

|     |                         | 2.3.1   | Data structure-based microbenchmarks              | 34 |

|     |                         | 2.3.2   | Realistic benchmarks                              | 34 |

|     |                         | 2.3.3   | Highly configurable workload generators           | 39 |

|     | 2.4                     | Conclu  | iding remarks                                     | 42 |

| 3 | Und | erstanding the Performance of TM Applications           | 45  |

|---|-----|---------------------------------------------------------|-----|

|   | 3.1 | STM vs. traditional synchronization                     | 46  |

|   | 3.2 | Performance impact of STM systems                       | 48  |

|   | 3.3 | Tracing TM applications                                 | 50  |

|   |     | 3.3.1 Goals                                             | 51  |

|   |     | 3.3.2 Which events to trace?                            | 52  |

|   | 3.4 | A tracing mechanism adapted for TM applications         | 53  |

|   |     | 3.4.1 Function interceptions                            | 56  |

|   |     | 3.4.2 Timestamps                                        | 59  |

|   |     | 3.4.3 Intrusiveness                                     | 60  |

|   | 3.5 | Case studies: STAMP applications                        | 62  |

|   |     | 3.5.1 Intruder                                          | 63  |

|   |     | 3.5.2 Genome                                            | 65  |

|   |     | 3.5.3 Labyrinth                                         | 66  |

|   | 3.6 | Concluding remarks                                      | 68  |

| 4 | Imp | roving the Performance of TM Applications on Multicores | 71  |

|   | 4.1 | Impact of thread mapping on TM applications             | 71  |

|   | 4.2 | A machine learning-based approach for thread mapping    | 75  |

|   |     | 4.2.1 Overview of the ML-based approach                 | 75  |

|   |     | 4.2.2 Application profiling                             | 76  |

|   |     | 4.2.3 Data pre-processing                               | 77  |

|   |     | 4.2.4 Learning process                                  | 79  |

|   |     | 4.2.5 Prediction                                        | 81  |

|   | 4.3 | Static thread mapping                                   | 82  |

|   |     | 4.3.1 Gathering input data to feed the learning process | 82  |

|   |     | 4.3.2 Generating the decision trees                     | 84  |

|   |     | 4.3.3 Predicting and applying thread mapping strategies | 86  |

|   | 4.4 | Dynamic thread mapping                                  | 87  |

|   |     | 4.4.1 From static to dynamic thread mapping             | 88  |

|   |     | 4.4.2 Implementation on TinySTM                         | 89  |

|   | 4.5 | Concluding remarks                                      | 91  |

| 5 | Exp | erimental Evaluation                                    | 95  |

|   | 5.1 | Experimental setup                                      | 95  |

|   |     | 5.1.1 Multicore platforms                               | 95  |

|   |     | 5.1.2 Performance metrics                               | 96  |

|   | 5.2 | Static thread mapping analysis                          | 97  |

|   |     | 5.2.1 Varying concurrency                               | 99  |

|   |     |                                                         | 101 |

|   |     |                                                         | 102 |

|    | 5.3            | Dynamic thread mapping analysis                        | 104 |

|----|----------------|--------------------------------------------------------|-----|

|    |                | 5.3.1 Workloads                                        | 105 |

|    |                | 5.3.2 Dynamic thread mapping vs. static thread mapping | 106 |

|    |                | 5.3.3 Varying concurrency                              | 108 |

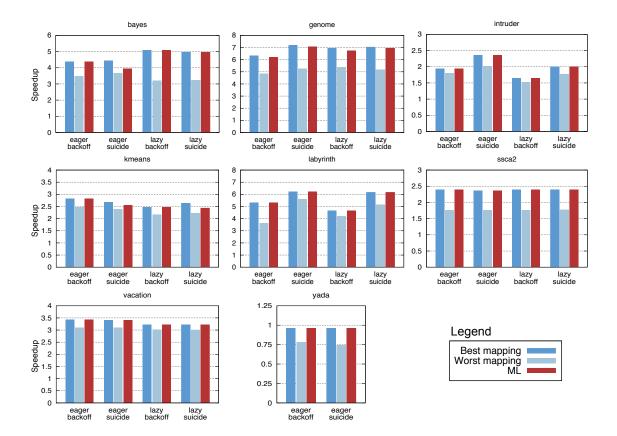

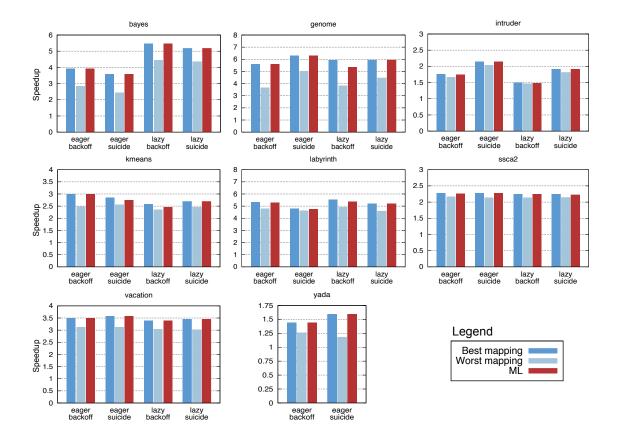

|    |                | 5.3.4 Modifying the STM parameters                     | 110 |

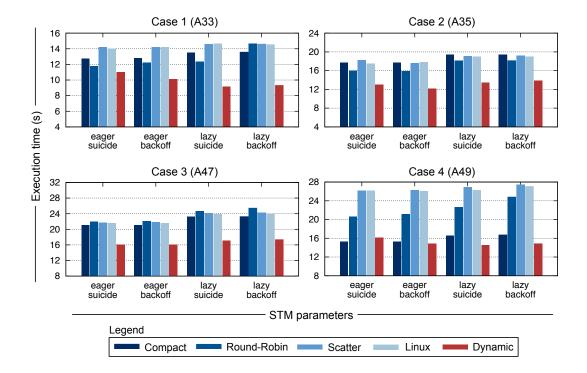

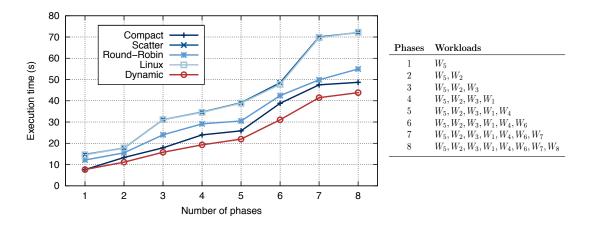

|    |                | 5.3.5 Varying the number of phases                     | 112 |

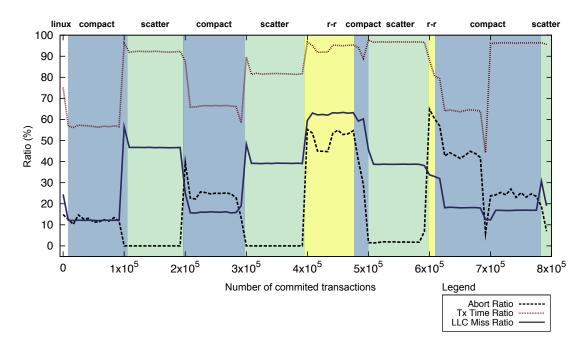

|    |                | 5.3.6 Dynamic thread mapping in action                 | 113 |

|    | 5.4            | Concluding remarks                                     | 114 |

| 6  | <b>D</b> 1     | . 1 747 1                                              | 110 |

| 6  |                | ited Work                                              | 117 |

|    | 6.1            |                                                        | 117 |

|    |                | 6.1.1 Performance evaluation of TM systems             |     |

|    | 6.0            | 6.1.2 Post-mortem analysis of TM applications          | 118 |

|    | 6.2            | Thread and process mapping                             | 120 |

|    | 6.3            | Machine learning                                       | 122 |

| 7  | Con            | clusion and Perspectives                               | 125 |

|    | 7.1            | Contributions                                          | 126 |

|    | 7.2            | Future works                                           | 128 |

|    |                |                                                        |     |

| Α  | Stat           | ic Thread Mapping Results                              | 131 |

| В  | Exte           | ended Abstract in French                               | 135 |

|    |                |                                                        | 179 |

| Bi | Bibliography 1 |                                                        |     |

# List of Figures

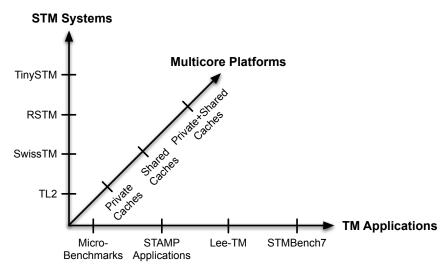

| 1.1  | Software Transactional Memory (STM) systems, TM applications and multicore platforms. | 3  |

|------|---------------------------------------------------------------------------------------|----|

| 2.1  | Example of a multicore platform with two levels of shared caches                      | 14 |

| 2.2  | Example of the scalability potential of multicore processors                          | 15 |

| 2.3  | Example of the impacts of memory hierarchy on the performance of a                    |    |

|      | synthetic parallel application.                                                       | 17 |

| 2.4  | Snippets of the strict (left) and relaxed (right) versions of TSP                     | 19 |

| 2.5  | Execution times of the two variations of TSP (strict vs. relaxed)                     | 20 |

| 2.6  | Transactional Memory basic concepts.                                                  | 23 |

| 2.7  | Example of conflicting and non-conflicting scenarios                                  | 23 |

| 2.8  | STM integration with programming languages.                                           | 30 |

| 2.9  | Pseudo-code description of EigenBench extracted from [Hon+10]                         | 40 |

| 3.1  | Snippets of the lock-strict (left) and STM (right) versions of TSP                    | 46 |

| 3.2  | Execution times of the three variations of TSP (locks vs. STM)                        | 47 |

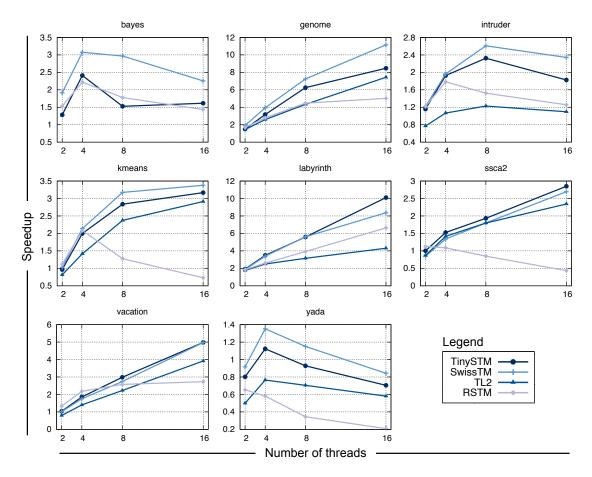

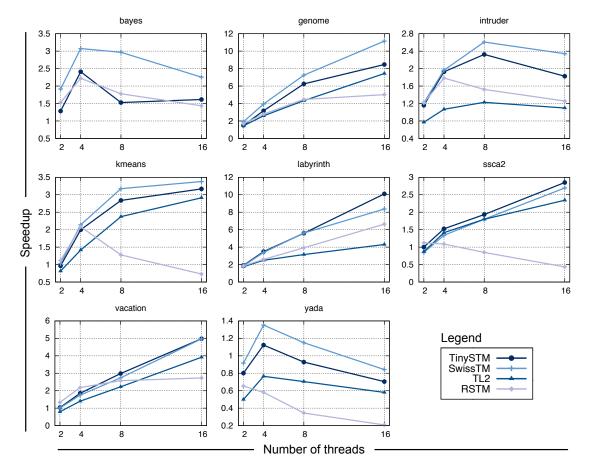

| 3.3  | Speedups off all STAMP applications with four state-of-the-art STM systems.           | 49 |

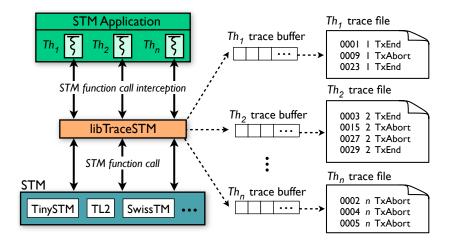

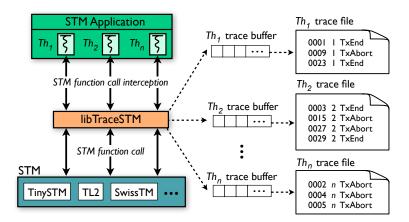

| 3.4  | Overview of the tracing mechanism                                                     | 54 |

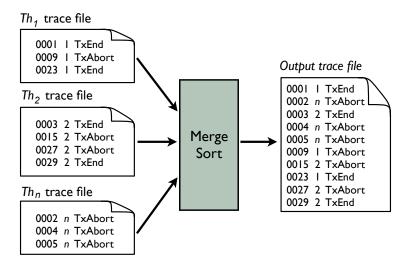

| 3.5  | Merge sort of individual trace files.                                                 | 55 |

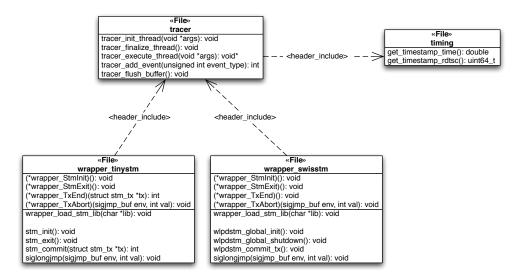

| 3.6  | File diagram of the main source files of libTraceSTM                                  | 56 |

| 3.7  | Snippets of the function wrappers to register the events <i>StmInit</i> and           |    |

|      | StmExit for TinySTM                                                                   | 57 |

| 3.8  | Snippets of the function wrappers to register the events $TxEnd$ (left) and           |    |

|      | <i>TxAbort</i> (right) for TinySTM.                                                   | 59 |

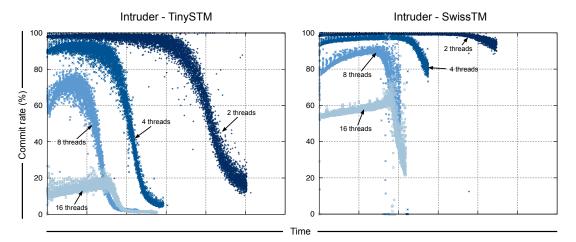

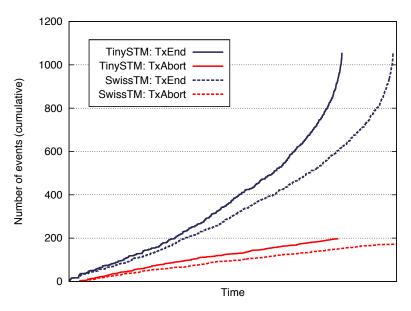

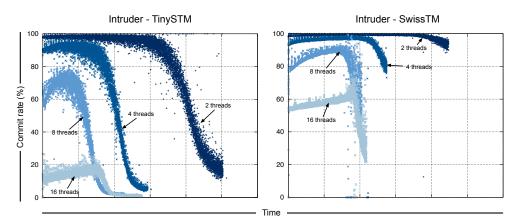

| 3.9  | Instantaneous commit rates of intruder with TinySTM and SwissTM                       | 64 |

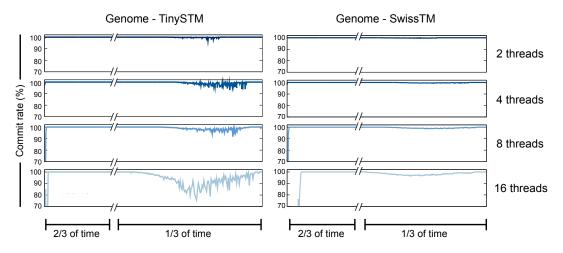

|      | Instantaneous commit rates of genome with TinySTM and SwissTM                         | 65 |

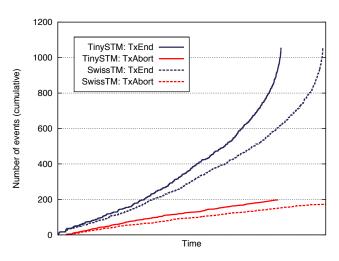

| 3.11 | Cumulative number of $TxEnd/TxAbort$ in labyrinth with 16 threads                     | 67 |

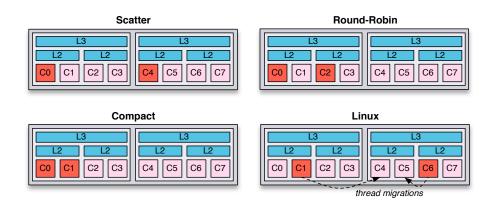

| 4.1  | Thread mapping strategies.                                                            | 73 |

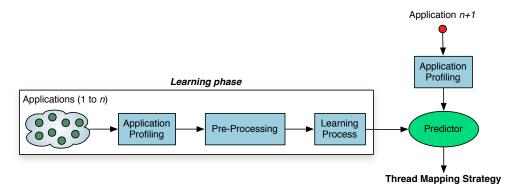

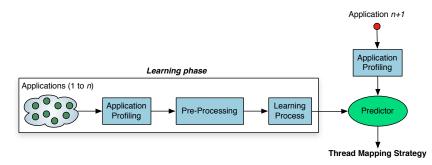

| 4.2  | Overview of our ML-based approach                                                     | 75 |

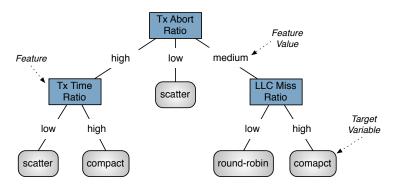

| 4.3  | Hypothetical example of a decision tree                                               | 79 |

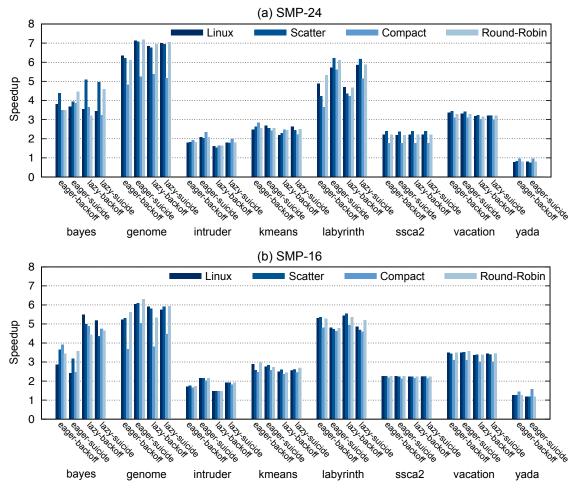

| 4.4 | Impact of thread mapping strategies on the performance of TM applica-             | ~~~ |

|-----|-----------------------------------------------------------------------------------|-----|

|     | tions with different STM configurations.                                          | 83  |

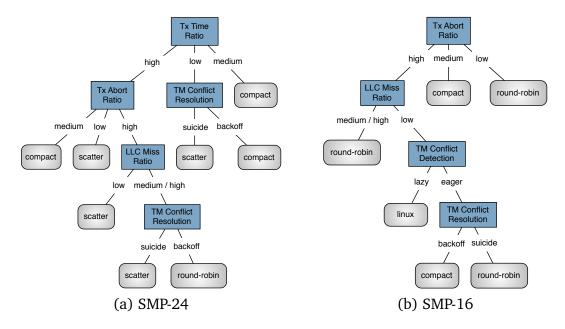

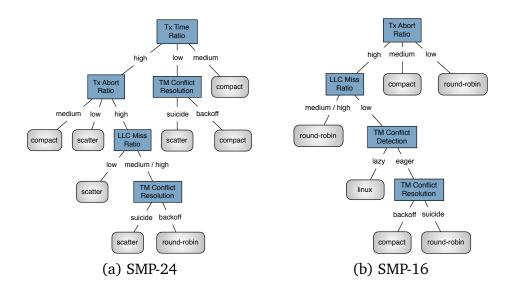

| 4.5 | Decision trees generated by the ID3 learning algorithm on both platforms          |     |

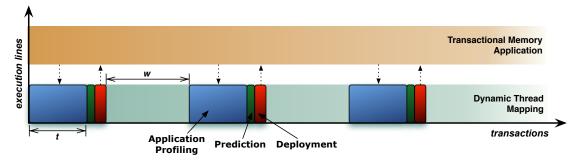

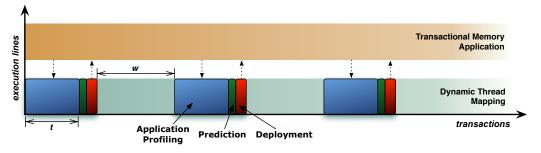

| 4.6 | Application execution with dynamic thread mapping.                                | 88  |

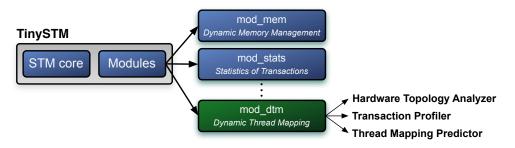

| 4.7 | Implementation of our dynamic thread mapping in TinySTM                           | 89  |

| 4.8 | Transaction profiler pseudo-codes                                                 | 91  |

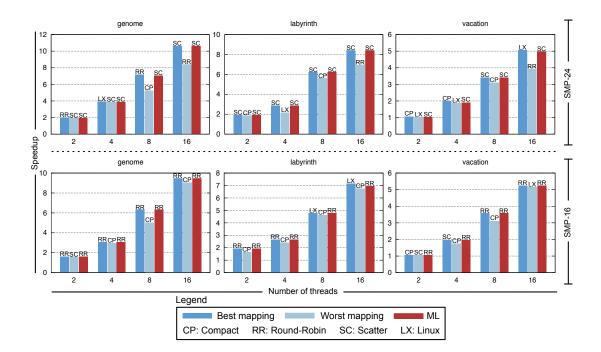

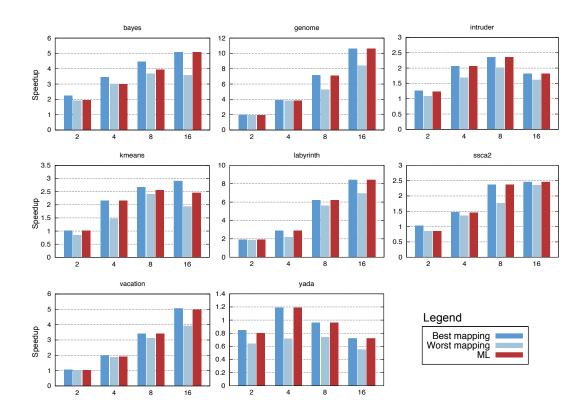

| 5.1 | Speedups of the best and worst thread mappings in comparison to the               |     |

|     | ML when varying concurrency.                                                      | 99  |

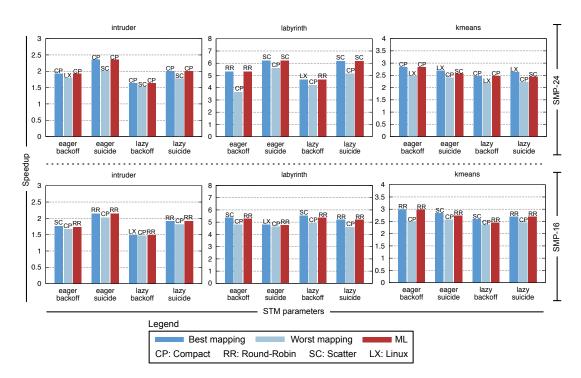

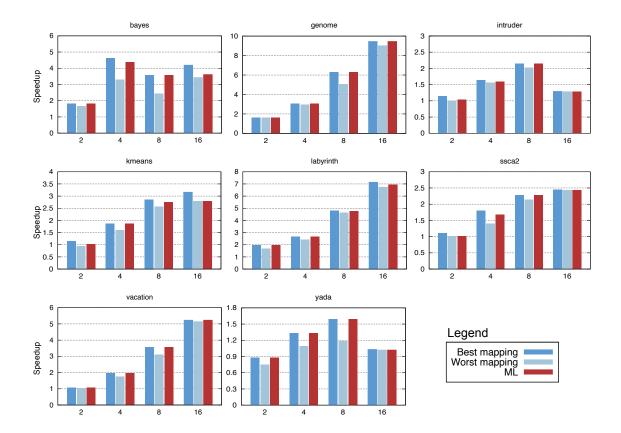

| 5.2 | Speedups of the best and worst thread mappings in comparison to the               |     |

|     | ML when varying the STM parameters.                                               | 101 |

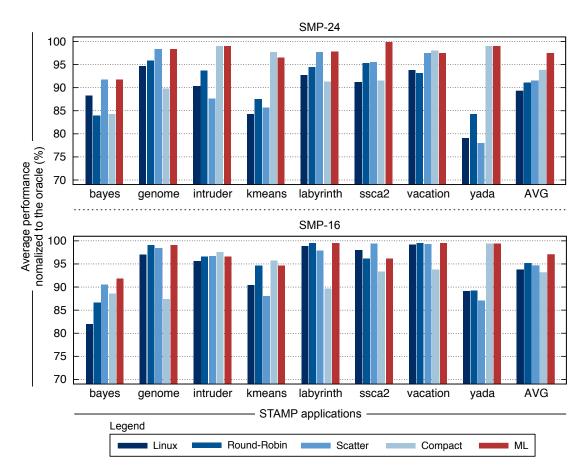

| 5.3 | The average speedup of all benchmarks considering the fixed thread                |     |

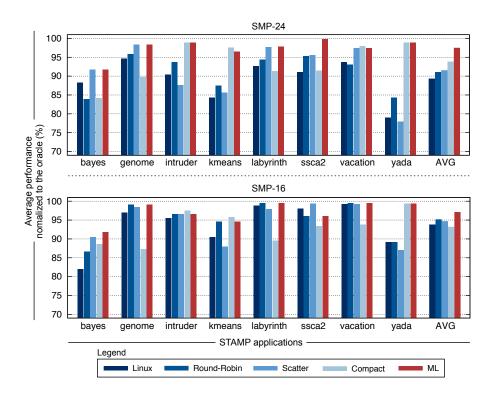

|     | mapping strategies, our ML approach and the oracle on both platforms.             | 103 |

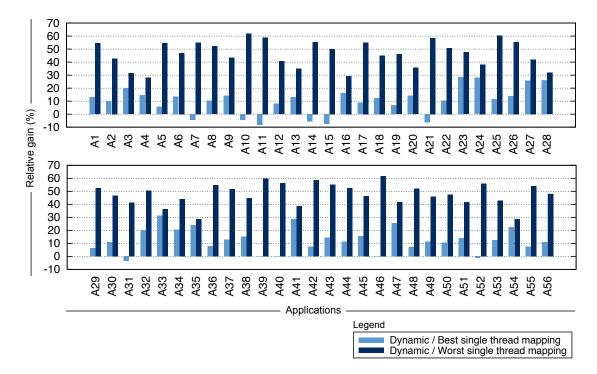

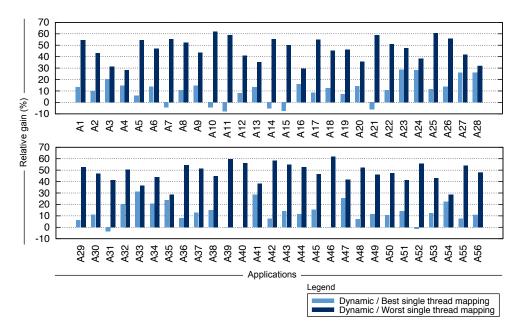

| 5.4 | Relative gains of the dynamic thread mapping compared to the best and             |     |

|     | worst static mappings on applications composed of 3 phases ( $A_1$ to $A_{56}$ ). | 107 |

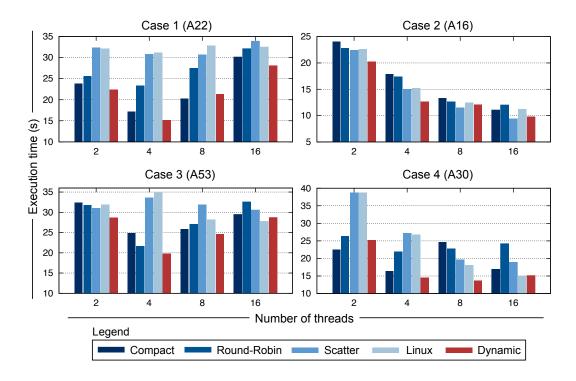

| 5.5 | Execution times when varying the number of threads                                | 108 |

| 5.6 | Execution times when varying the STM parameters                                   | 110 |

| 5.7 | Performance of individual thread mapping strategies and the dynamic               |     |

|     | approach when varying the number of phases                                        | 112 |

| 5.8 | Profiled metrics during the execution of an application with 8 phases             | 113 |

| A.1 | Speedups of the best and worst thread mappings in comparison to the               |     |

|     | ML when varying concurrency on the SMP-24                                         | 131 |

| A.2 | Speedups of the best and worst thread mappings in comparison to the               |     |

|     | ML when varying concurrency on the SMP-16                                         | 132 |

| A.3 | Speedups of the best and worst thread mappings in comparison to the               |     |

|     | ML when varying the STM parameters on the SMP-24                                  | 133 |

| A.4 | Speedups of the best and worst thread mappings in comparison to the               |     |

|     | ML when varying the STM parameters on the SMP-16                                  | 134 |

|     |                                                                                   |     |

vi

# List of Tables

| 3.1 | The most common STM operations                                   | 52  |

|-----|------------------------------------------------------------------|-----|

| 3.2 | Intrusiveness of the tracing mechanism on all STAMP applications | 61  |

| 4.1 | Impact of thread mapping strategies on TM applications           | 74  |

| 4.2 | TM application, STM system features and the target variable      | 76  |

| 5.1 | Overview of the multicore platforms and softwares                | 96  |

| 5.2 | TM characteristics used to compose our set of workloads          | 105 |

| 5.3 | Transactional workloads.                                         | 106 |

# List of Abbreviations

| DBMS   | Transactional Database Management Systems                |

|--------|----------------------------------------------------------|

| DRAM   | Dynamic Random Access Memory                             |

| GCC    | GNU Compiler Collection                                  |

| GFlops | Billions of floating-point operations per second         |

| HTM    | Hardware Transactional Memory                            |

| hwloc  | Hardware Locality                                        |

| HyTM   | Hybrid Transactional Memory                              |

| ID3    | Iterative Dichotomiser 3                                 |

| LLC    | Last Level Cache                                         |

| ML     | Machine Learning                                         |

| MPI    | Message Passing Interface                                |

| NUMA   | Non-Uniform Memory Access                                |

| PAPI   | Performance Application Programming Interface            |

| STAMP  | Stanford Transactional Applications for Multi-Processing |

| STM    | Software Transactional Memory                            |

| TAU    | Tuning and Analysis Utilities                            |

| ТМ     | Transactional Memory                                     |

| TSC    | Time Stamp Counter                                       |

| TSP    | Traveling Salesman Problem                               |

| UMA    | Uniform Memory Access                                    |

## CHAPTER .

# Introduction

There was a 30-year period in which the advances in semiconductor technology and computer architectures improved the performance of a single processor at a high annual rate of 40% to 50% [LK08]. However, some issues such as dissipating heat from increasingly densely packed transistors begun to limit the rate at which processor frequencies could be increased. This was one of the reasons why most semiconductor industries are now investing in multicore processors.

Indeed, multicore processors are a mainstream approach to deliver higher performance to parallel applications [Asa+09].Unfortunately, the growing disparity between how fast a processor can operate on data and how fast it can get the data it needs leads to the so-called "memory wall problem" [McK04]. Consequently, these platforms usually feature complex memory hierarchies composed of different levels of cache to alleviate the penalties of accessing the main memory.

Considering the fact that the semiconductor technology is still capable of doubling the transistors on a chip every two years, it is clear that the number of cores on a chip will continue to increase. For instance, the Intel Tera-scale Computing Research Program has recently created a prototype chip containing 80 cores. In this context of many-core architectures, researchers are also exploring the use of 3D chip stacking to provide large, low-latency, last-level caches stacked on top of processors. This reduces power consumption and also improves bandwidth [HBK06].

Consequently, applications must evolve to efficiently exploit the potential of

multicore platforms. Old sequential applications must now be split into pieces (*e.g.*, tasks) that can be executed in parallel by threads, each one running on a specific core. The side effect is that the application data, which were accessed by a single thread on a sequential application, is now shared among several concurrent threads. Since usually applications are not embarrassingly parallel, it is necessary to use synchronization mechanisms to coordinate concurrent accesses to these shared data.

Traditional synchronization mechanisms such as *locks*, *mutexes* and *semaphores* have been extensively used to synchronize threads on multicore platforms and systems. They are simple to implement in hardware and they are safe mechanisms to deal with concurrent accesses to shared data. However, such simplicity comes with significant drawbacks. Firstly, they are considered as "low-level" mechanisms, since one must explicitly control the access of shared variables. Secondly, they cause blocking, so threads always have to wait until a lock (or a set of locks) is released. Thirdly, the careless use of such mechanisms can easily result in deadlocks or livelocks [Tai94]. Finally, blocking considerably limits scalability and adds complexity to the source code.

Due to the previously discussed issues, researchers have been looking for alternative mechanisms. One of such alternative mechanisms that has been subject of intense research in the last years is Transactional Memory (TM). The TM programming model allows programmers to write parallel portions of the code as transactions, which are guaranteed to execute atomically and in isolation regardless of eventual data races [Dal+10; HLR10]. At runtime, transactions are executed speculatively and the TM runtime system continuously keeps track of concurrent accesses and detects conflicts. Conflicts are then solved by re-executing conflicting transactions. Therefore, it removes from the programmer the burden of correct synchronization of threads and provides an efficient model for extracting parallelism from the applications.

Different implementations of TM systems make tradeoffs that impact both performance and programmability. The most common design choices are STM, Hardware Transactional Memory (HTM) and Hybrid Transactional Memory (HyTM). STM implements everything in software, so there is no need for a specific hardware [DGK09; DSS06; FFR08]. On the contrary, HTM implements all functionalities in hardware [McD+05; Moo+06]. The HyTM is a hybrid approach in which the hardware simply serves to optimize the performance of transactions that are controlled fundamentally by software [Kum+06; Shr+06].

STM has some advantages over the other two approaches. It offers flexibility in implementing different mechanisms and conflict detection/resolution policies. It is easier to be modified or extended, it is not limited by small fixed-size hardware structures (such as cache memories) and it does not require specific hardware (thus it can be used on current platforms). Additionally, hardware and hybrid solutions are still in a premature stage and their implementation on commercial processors has just get started. The disadvantage is that STM performs worse than HTM and HyTM.

In general, the efficiency of parallel applications relies upon matching the behavior of the application with the underlying system and platform characteristics. This issue becomes much more complex in STM basically due to two reasons: (i) the TM model uses speculation, hence TM applications present an irregular behavior (data dependencies between threads are only known at runtime); and (ii) each STM system implements its own mechanisms to detect and solve conflicts and thus the same TM application can behave differently when the underlying STM system is changed.

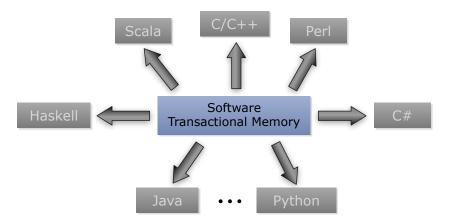

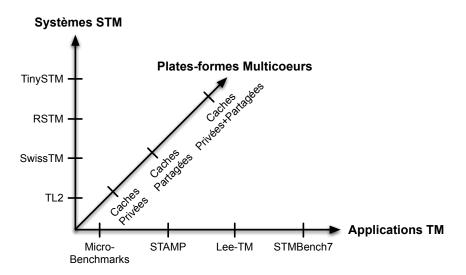

Figure 1.1: STM systems, TM applications and multicore platforms.

Figure 1.1 illustrates this scenario. On the *STM system*-axis, we included some of the STM systems currently available. Each one has its peculiarities such as the aforementioned mechanisms to detect and solve conflicts. On the *TM applications*-axis, we included the most known applications and benchmarks that are used to

evaluate STM systems. Some benchmarks such as the Stanford Transactional Applications for Multi-Processing (STAMP) are composed of several applications [Min+08]. TM applications may differ in several aspects such as the level of concurrency, the probability of conflicts, the size and the time spent inside transactions. Finally, on the *multicore platforms*-axis, we represented the differences in terms of memory hierarchy of multicore platforms: only private caches, only shared caches or mixes of both. All those aspects can have an important impact on the performance of applications.

In this thesis, we plan to **understand** and **improve** the performance of TM applications on multicore platforms. However, this is not trivial due to the several possible combinations of the previously cited aspects. We intend to analyze the performance and propose improvements to TM applications by using low-intrusive techniques to both TM applications and STM systems.

#### 1.1 Research issues

As previously mentioned, the contributions of this thesis are situated around the analysis and improvement of the performance of TM applications on multicore platforms. In this section, we present some possible ways of exploring these issues and we define our main focus on each issue.

#### 1.1.1 Understanding the performance of TM applications

The increased complexity in the development of parallel programs can be eased up by a good understanding of the effective application behavior in its specific hardware and software execution contexts [Lou+09]. Such information can be useful to understand and improve the performance of parallel applications. There are basically two main approaches to achieve this goal, *i.e.*, runtime analysis and post-mortem analysis.

Runtime analysis: collects runtime information about the application behavior and uses such information to perform some action at runtime. Runtime analysis usually requires a small amount of storage and frequently relies on *sampling* techniques to reduce the overhead [SBS11]. As an example, we can cite the work presented in [SH11], in which the authors use runtime analysis to characterize the workloads and adapt processor frequencies based on performance counter measures at runtime.

▶ Post-mortem analysis: the collected runtime information is recorded in a detailed log (trace file) for later analysis. The trace file is usually composed of timestamped *events* and their *attributes* [She99]. An event is typically represented by an ordered tuple that consists of the event identifier, the timestamp when the event occurred, where it occurred (*e.g.*, a thread identifier) and optional fields for specific information. The trace file can then be analyzed with a visualization tool such as Vampir [Knu+08].

In this thesis we explore both techniques to understand and improve the performance of TM applications. More precisely, we focus on techniques that do not add considerable intrusiveness to both TM applications and STM systems. This subject is further discussed in Chapters 3 and 4.

#### **1.1.2** Improving the performance of TM applications

The performance of TM applications can be improved in several ways. In this section, our main objective is not to present an exhaustive list of works that aim at improving the performance of TM applications. Instead, we intend to show that the performance can be improved at different levels, ranging from the application to the platform levels. Then, we situate our approach proposed in this thesis.

► TM application: There are several ways of improving the performance at the TM application level. One possible approach is to change the TM application source code in such a way that the probability of having conflicts is reduced. One of such techniques is called *privatization*, which temporarily privatizes a shared data during a computation to reduce conflicts [MSS08]. When conflicts are reduced, there will be less transactions being re-executed due to conflicts. Consequently, the application will take less time to execute.

- ► STM system: Another alternative to improve the overall performance of a TM application is modifying the STM system algorithms to fit the application workload. For instance, some STM systems present better performance with read-dominant workloads whereas others are more suitable for write-dominant workloads. In [MIS05], the authors proposed an Adaptive STM system (ASTM) that automatically adapts its behavior to the application workload, allowing it to closely approximate the performance of the best existing system for that workload.

- ► Operating system: Current mainstream operating systems do not have any integration with Transactional Memory. The performance of TM applications can be enhanced if operating systems offer special integration with HTM as proposed in [Ros+07]. Another example of optimizations at the operating system level is proposed in [Mal+11]. In this work, the authors extended the Linux scheduler to support deadlines for reactive TM applications.

- Platform: At the platform level, we can consider two possible types of optimizations. On the one hand, it is possible to construct a specific platform that implements TM in hardware to accelerate the execution of TM applications. As an example, we can cite the Intel's next generation processor microarchitecture named *Haswell*<sup>1</sup>, which will provide instruction set extensions that allow programmers to specify regions of code for transactional synchronization. On the other hand, TM applications can better exploit the full potential of current multicore platforms by taking into consideration the platform characteristics such as the memory hierarchy [WL10]. In this case, the performance gains can be obtained by matching the characteristics of the TM application to those of the underlying platform.

We believe that the performance of TM applications can be improved if we match its characteristics (along with the characteristics of the STM system) to the underlying multicore platform. More precisely, we propose to gather these characteristics from the TM applications and STM systems and then use such information to better exploit the memory hierarchy of modern multicore platforms.

$<sup>^1 \</sup>rm More$  information available at http://software.intel.com/en-us/blogs/2012/02/07/transactional-synchronization-in-haswell/

One technique to deal with that is called thread or processes mapping, which aims at mapping threads or processes to specific cores to improve the use of resources such as interconnections and cache memories. Although the impacts of applying thread mapping on TM applications has not been explored yet, we believe that it could be beneficial due to some intuitions. For instance, consider a TM application in which transactions constantly access the same amount of shared data. In this case, placing threads on sibling cores may reduce the latency because the data will probably be stored into the cache shared by these threads. This may be the case of high-conflicting TM applications. Now, consider an opposite case where a TM application is composed of several transactions that usually access a large amount of disjoint data, thus rarely conflicting. In this case, distributing threads across different processors (thus avoid cache sharing) may reduce the contention on the same cache, making more cache available for each thread.

In this thesis we want to confirm these intuitions and propose an approach capable of predicting suitable thread mappings for TM applications to improve their performances. This subject is discussed in more details in Chapter 4.

#### **1.2 Contributions**

The first contribution of this thesis concerns the comprehension of the performance of TM on multicore platforms. In order to do that, we first take a deeper look on the impacts of STM systems on the performance of TM applications. We show that the performances of applications using TM-based synchronization solutions depend on both the applications themselves and the STM system specifics. We support this fact by demonstrating that the use of TM may result in worse or better performance for the application, depending on these specifics. In order to gain some insight on these issues, helping developers to understand and improve their performance, we propose a generic approach for collecting and tracing relevant information about transactions. Our solution can be applied to different STM systems and applications as it does not modify neither the target application nor the STM system source codes. We then show that the collected information can be helpful in order to comprehend the performance of TM applications.

This joint work with Kiril Georgiev (Ph.D. student at Université de Grenoble),

Vania Marangozova-Martin (assistant professor at *Université de Grenoble*) and Miguel Santana (head of the Embedded Software Development Tools department in STMicroelectronics Central R&D group) resulted in a publication in the proceedings of the Euromicro International Conference on Parallel, Distributed and Network-Based Computing (PDP) in 2011:

Márcio Castro, Kiril Georgiev, Vania Marangonzova-Martin, Jean-François Méhaut, Luiz Gustavo Fernandes, and Miguel Santana. "Analysis and Tracing of Applications Based on Software Transactional Memory on Multicore Architectures". In: *Euromicro International Conference on Parallel, Distributed and Network-Based Computing (PDP)*. Aya Napa, Cyprus: IEEE Computer Society, 2011, pp. 199–206. ISBN: 978-0-7695-4328-4. DOI: 10.1109/PDP.2011.27

The second contribution of this thesis concerns the proposal of an approach to improve the performance of TM applications through the exploitation of the memory hierarchy of modern multicore platforms. We evaluate and demonstrate that the use of thread mapping strategies allows us to make better use of the underlying multicore platform and thus improve the performance of TM applications. However, the efficiency of such approach relies upon matching the application behavior with system characteristics. Particularly, STM systems make this task even more difficult due to its runtime system. Existing STM systems implement several conflict detection and resolution mechanisms, which leads TM applications to behave differently for each combination of these mechanisms. Thus, the prediction of a suitable thread mapping strategy for a specific application/STM system becomes a daunting task. We tackle this problem by using Machine Learning (ML) to automatically infer a suitable thread mapping strategy for TM applications. Our approach takes into account not only the characteristics of the TM application but also the STM system and the underlying multicore platform.

This joint work with Luís Fabrício Góes (Ph.D. student at University of Edinburgh), Prof. Murray Cole and Prof. Marcelo Cintra (both from the University of Edinburgh) resulted in the following publication in the proceedings of the High Performance Computing Conference (HiPC) in 2011:

#### 1.2. CONTRIBUTIONS

Márcio Castro, Luís Fabricio Wanderley Góes, Christiane Pousa Ribeiro, Murray Cole, Marcelo Cintra, and Jean-François Méhaut. "A Machine Learning-Based Approach for Thread Mapping on Transactional Memory Applications". In: *High Performance Computing Conference (HiPC)*. Bangalore, India: IEEE Computer Society, 2011, pp. 1–10. ISBN: 978-1-4577-1949-3. DOI: 10.1109/HiPC. 2011.6152736

Finally, our third contribution extends the aforementioned approach to predict and apply suitable thread mapping strategies for TM applications in a dynamic fashion. We argue that more complex applications will make use of TM in a near future. Those applications can be composed of multiple execution phases with a potentially different transactional behavior in each phase. Thus, instead of predicting and applying a single static thread mapping strategy, we use profiling techniques to gather useful information during the execution of TM applications, switching the thread mapping strategy to a more adequate one at runtime when necessary. We implemented this approach in a state-of-the-art STM system, making it transparent to the user.

The preliminary results of our third contribution were presented and discussed in the Euro-TM Workshop on Transactional Memory (WTM) in 2012 (co-located with EuroSys 2012). The workshop consisted of short presentations and did not have any published proceedings to facilitate later submission to other venues. The submissions were evaluated by members of the Euro-TM Management Committee.

Márcio Castro, Luís Fabrício Góes, Luiz Gustavo Fernandes, and Jean-François Méhaut. "Dynamic Thread Mapping Based on Machine Learning for Transactional Memory Applications". In: *Euro-TM Workshop on Transactional Memory* (WTM). Extended abstract. Apr. 2012

An extended version of this work was accepted for inclusion in the technical program and the proceedings of the International European Conference on Parallel and Distributed Computing (Euro-Par) in 2012. This was a joint work with Luís Fabrício Góes (Ph.D. student at University of Edinburgh).

Márcio Castro, Luís Fabrício Góes, Luiz Gustavo Fernandes, and Jean-François Méhaut. "Dynamic Thread Mapping Based on Machine Learning for Transactional Memory Applications". In: *International European Conference on Parallel and Distributed Computing (Euro-Par)*. Vol. 7484. Lecture Notes in Computer Science (LNCS). Rhodes Island, Greece: Springer-Verlag, 2012, pp. 465–476. ISBN: 978-3-642-32819-0. DOI: 10.1007/978-3-642-32820-6\_47

#### **1.3** Scientific context of the thesis

This thesis was funded by a subproject of Nano 2012 program called OPM<sup>2</sup>: Analysis and Observation of Multithreaded Applications on Multicore Processors. In the context of this thesis, one of our main contributions to this project was to evaluate and analyze the performance of Transactional Memory on multicore platforms [CD10; Cas10; Cas+10].

The research that led to the published papers cited in the previous section as well as all the contents of this thesis was carried out in the **Nanosim** team. Nanosim stands for *Nanosimulations and Embedded Applications for Hybrid Multi-core Architectures* and it is one of the research teams of the Grenoble Informatics Laboratory (*Laboratoire d'Informatique de Grenoble* - LIG). The main research fields of Nanosim are High Performance Computing (HPC) and Embedded Systems. More precisely, in the field of HPC, the Nanosim team is interested in providing environments to better exploit multiprocessor architectures. Nanosim members have also straight collaborations with Brazilian universities such as the *Universidade Federal do Rio Grande do Sul* (UFRGS), the *Universidade Federal de São Paulo* (USP), the *Pontifícia Universidade Católica do Rio Grande do Sul* (PUCRS) and the *Pontifícia Universidade Católica de Minas Gerais* (PUC Minas).

During this thesis, I have developed other scientific works in collaboration with members from Nanosim and other research teams. Some of these collaborations are closely related to this thesis whereas others are related to high performance computing on parallel platforms in general. These collaborations began when I was a master's student in Brazil under the direction of Prof. Luiz Gustavo Fernandes. My master's thesis was about the parallelization of a Geophysics application that exploited memory affinity strategies for Non-Uniform Memory Access (NUMA) platforms. This work was closely related to the thesis of Christiane Pousa Ribeiro (Nanosim, *Université de Grenoble*). At that time, Christiane was under the direction of Jean-François Méhaut (*Université de Grenoble*) and her main research topic was *memory affinity for NUMA platforms* [Rib11]. Such common research topic allowed us to collaborate during my thesis and resulted in several publications in national and international conferences [Cas+09; Rib+10; Rib+09b; Rib+09a]. All these works aimed at using memory affinity strategies to improve the performance of high performance scientific applications.

More recently, I also collaborated with Prof. Henrique Cota de Freitas and Carlos Augusto Paiva da Silva Martins, both professors at *Pontifícia Universidade Católica de Minas Gerais* (PUC Minas), Brazil. These works concerned the analysis and evaluation of parallel workloads on multicore platforms and also led to publications in international conferences [Oli+11; Rib+11].

#### **1.4** Thesis outline

The remaining chapters of this thesis are organized as follows:

- Chapter 2 reviews the basic concepts and topics that are relevant throughout this thesis. We briefly discuss the evolution of multicore platforms as well as their impacts on the performance of parallel applications, we present an overview of Transactional Memory along with some important design criteria that impact its performance and we describe the most known applications and benchmarks used to evaluate Transactional Memory systems.

- Chapter 3 concerns the comprehension of the performance of TM applications on multicore platforms. We analyze the impacts of both applications and STM systems on the overall performance and propose a generic approach for collecting relevant information from TM applications. We then use such approach to gain some insights about the performance of TM applications.

- Chapter 4 proposes the use of Machine Learning to improve the performance of TM applications through the exploitation of the memory hierarchy of multicore platforms. Our approach considers the characteristics of the TM application, STM system and platform to infer an efficient thread mapping adapted to the underlying environment.

- Chapter 5 presents an experimental evaluation of our ML-based approach for thread mapping on TM applications on two multicore platforms.

- ► Chapter 6 discusses several related works concerning the performance evaluation of TM systems and applications, the use of thread mapping to improve the performance of applications and the use of machine learning to construct heuristics for improving the performance of parallel applications.

- ► Chapter 7 presents our conclusions and perspectives.

# CHAPTER 2

# Background

This chapter aims at reviewing the basic concepts and topics that are relevant throughout this thesis. More precisely, in Section 2.1, we briefly discuss the evolution of multicore platforms as well as their impacts on the performance of parallel applications. In Section 2.2, we present an overview of Transactional Memory along with some important design criteria that impact its performance. In Section 2.3, we describe the most known applications and benchmarks used to evaluate Transactional Memory systems. We then conclude this chapter in Section 2.4.

#### 2.1 Multicore platforms

Historically, processor manufacturers have responded to the demand for more processing power by delivering faster processor speeds. However, the need to achieve higher performance without driving up power consumption and heat has become a critical concern. The solution for this problem is based on the fact that a good overall processing performance can be achieved by reducing individual core clock speeds while increasing the number of cores. Consequently, this can lower the heat of individual cores and increase the overall performance.

#### 2.1.1 Architectural concept

Although the organization of a multicore platform can vary depending on manufacturer and product development over time, they share some basic features: processors have two or more processing units (cores) and cache modules. These cache modules are arranged hierarchically and can either be shared or independent. Usually, cache memories closer to the cores tend to be private whereas higher level caches tend to be shared.

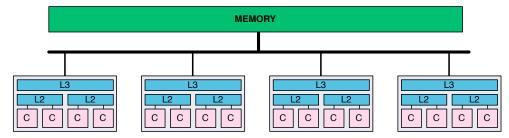

Figure 2.1: Example of a multicore platform with two levels of shared caches.

Figure 2.1 illustrates a multicore platform composed of four quad-core processors. In this example, there are two levels of cache memories (L2 and L3) and a shared main memory. Since the main memory is connected to all processors through a single bus, the time spent to access a data on the main memory is uniform. This design is known as Uniform Memory Access (UMA). Another possible design is to use multiple memory banks physically distributed through the platform. In this case, the main memory still has a unique address space but the time spent to access data is conditioned by the distance between the processor and the memory bank in which the data is physically allocated. This design is called Non-Uniform Memory Access (NUMA).

#### 2.1.2 Performance of multicores

It is well known that the rate of improvement in processor speed exceeds the rate of improvement in Dynamic Random Access Memory (DRAM) speed. Indeed, the performance of processors and DRAMs are improving exponentially, but the exponent for processors is substantially larger than that for DRAMs. This growing disparity leads to the so-called "memory wall problem" [McK04]. Obviously, the effective performance that can be obtained from a multicore platform also depends on several other factors such as memory hierarchy, application, operating system and compiler optimizations.

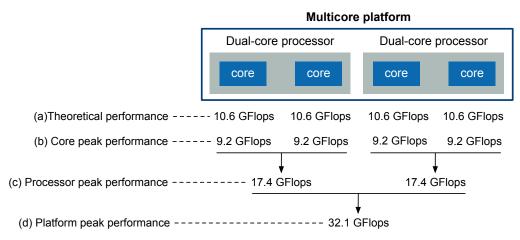

Figure 2.2 illustrates this problem. In this example, we consider a multicore platform composed of two dual-core processors. According to the processor specification, each core has a theoretical performance of 10.6 GFlops<sup>1</sup> as shown in Figure 2.2a. This means that, in theory, this multicore platform would be capable of executing 42.4 GFlops. However, real world performance may not come very close to the theoretical value. To evaluate how far is the effective performance from the theoretical one, we performed a series of experiments with the parallel version of the LINPACK benchmark<sup>2</sup>. LINPACK is benchmark that solves a dense system of linear equations.

Figure 2.2: Example of the scalability potential of multicore processors.

We executed this benchmark with a single thread and obtained a peak performance of 9.2 GFlops (Figure 2.2b), which is lower then the theoretical core performance. Secondly, we executed the benchmark with two threads in the same processor, obtaining a peak performance of 17.4 GFlops (Figure 2.2c), which is inferior to what would be expected (*i.e.*,  $2 \times 9.2$  GFlops). A similar behavior happened when we executed the benchmark with four threads. In this case, we obtained a peak effective performance of 32.1 GFlops (Figure 2.2d), which is inferior to  $2 \times 17.4$

<sup>&</sup>lt;sup>1</sup>GFlops stands for "billions of floating-point operations per second".

<sup>&</sup>lt;sup>2</sup>LINPACK can be download at http://www.netlib.org/linpack/

GFlops and far away from the theoretical performance of the platform (*i.e.*, 42.4 GFlops).

This example must be considered for demonstration purposes only. Since LIN-PACK is cpu-bound and solves a very regular problem, the performance achieved is quite high and gives a good estimation of the peak performance of the platform. However, the effective performance depends on several factors. One of such factors is the memory hierarchy, which can considerably impact the overall performance of applications that make intensive use of memory (memory-bound applications).

#### 2.1.3 Impacts of the memory hierarchy

In the context of memory hierarchy, as the distance between the core and the memory increases, the time needed to access a data physically stored on such memory also increases. This means that cores have a fast access to lower cache levels such as L1 and L2 than higher memory levels such as the main physical memory. Considering this fact, one can realize that it is always better to place threads on sibling cores. This can reduce the memory access latency by sharing all levels of the cache hierarchy, allowing threads to reuse the data that is already on cache. Indeed, this strategy can be used to improve the performance of some applications but it is not suitable for all applications. For instance, consider a memory-bound multithreaded application where threads usually access disjoint data. In this case, it may be better to distribute threads across different processors in such a way that they will not share caches to alleviate contention.

We demonstrate this scenario with a synthetic parallel application. As its core, the application is very simple: each thread executes a for loop with a fixed number of iterations and then exits. Each iteration consists of a fixed number of read and write operations on a one-dimension array of integers. Although the order of read and write operations as well as the array indexes to be accessed are chosen randomly, the algorithm guarantees the number of read and write operations as specified in the input parameters. The number of iterations, threads and the size of the array can also be specified.

We made two variations of this synthetic parallel application. The first one, named *shared array*, has a single shared array that is accessed by all threads. Since

we are only interested on the impact of the memory hierarchy, we do not use any synchronization mechanism to guarantee consistent results. The second one, named *private arrays*, has *t* private arrays, where *t* corresponds to the number of threads. In this case, each thread accesses only its private array.

In order to perform our experiments, we fixed the input parameters of the synthetic application as follows: the number of threads was fixed to 8, each thread executes 100,000 iterations and each iteration performs 1024 reads and 1024 writes. In the shared array variation, we used a single shared array of size 65,536. In the private arrays variation, on the other hand, each thread has a private array of size 65,536.

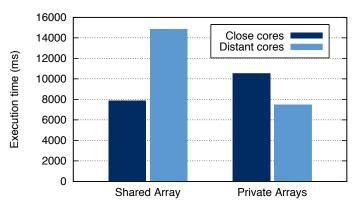

We then carried out several experiments with both variations of the synthetic application using the previously described input values. The target machine was a multicore NUMA platform composed of four 8-core Intel Xeon X7560 at 2.27GHz. Each core has private L1 (32KB) and L2 (256KB) caches and each processors has a shared L3 cache (24MB). During the experiments, we fixed the threads to the cores following two distinct strategies: one that pins all threads on the same processor and other that spreads threads among different processors. The goal is to observe the impact of the cache hierarchy on the performance of the synthetic application. The results are shown in Figure 2.3.

Figure 2.3: Example of the impacts of memory hierarchy on the performance of a synthetic parallel application.

As it can be noticed, the performance of the synthetic application changes when we change the way threads use the cache hierarchy. The shared array variation has better performance when threads are placed on sibling cores, since most of the shared data is on cache, reducing the latency. On the contrary, the use of different caches improved the performance of the private arrays variation, since this scheme reduces cache pollution and contention.

#### 2.1.4 Synchronization of shared data

To efficiently exploit the full potential of multicore platforms, applications must evolve. Old sequential applications are now parallel: they are split into pieces that are executed in parallel by threads, each one running on a specific core. The side effect is that the application data, which were accessed by a single thread on a sequential application, is now shared among several concurrent threads.

In a multithreaded environment, if multiple threads access the same resource for read and write, the value may not be the correct value. For instance, consider an application that contains two threads, one thread for reading the content from a file and another thread writing the content to the file. If the write thread tries to write and the read thread tries to read the same data, the data might become corrupted. One possible solution for this problem is to *lock* the file when the writer thread is modifying the file content. This means that the read thread will have to wait until the lock is released to proceed.

Indeed, the correct synchronization of multiple accesses to shared data is challenging. Depending on the complexity of problem that is parallelized, more or less mechanisms must be used to guarantee the correct execution of a parallel application without decreasing its scalability.

Among all possible synchronization mechanisms, locks are the most commonly used. A mutually exclusive (or **mutex**) lock is used to protect a **critical section**, which is a segment of code that only one thread at a time is allowed access. Differently, a **semaphore** can grant access to one or a limited number of threads. Some languages have a slightly higher level construct, a **monitor**, to prevent concurrent accesses.

The above mechanisms are considered as "low-level" mechanisms, since one must explicitly control the access of shared variables. They cause blocking, so threads always have to wait until a lock (or a set of locks) is released. This may add considerable overhead **even when the chances for collision are very rare**. In some cases, although the chances for collision are very rare, the accesses to shared data must be protected if we want to avoid race conditions, thus limiting the scalability of the application [HLR10; HX98].

We demonstrate how locks can limit the scalability by using the well-known Traveling Salesman Problem (TSP) [App+07], which finds the shortest possible path between two nodes in a graph by visiting each node exactly once. In our parallel implementation, the graph exploration is done by multiple threads. Concurrent threads access different shared data, such as the current shortest path and the pool of paths to explore. To avoid race conditions, we used mutex locks to protect concurrent accesses to shared variables. This was the case of the shared variable minimum, which stores the current shortest distance.

We implemented two variations of TSP. Our first approach is based on the fact that all global shared variables that are accessed concurrently should be protected with mutex locks (named *strict*). For the second approach, after a carefully analysis of the source code, we removed some of the mutex locks without creating data races (named *relaxed*). That was the case of some read-only accesses to the variable minimum, which can be relaxed without breaking the application correctness. Figure 2.4 shows an example of portions of the source code from the strict and relaxed versions, where the synchronization has been removed.

(a) strict

(b) relaxed

```

Figure 2.4: Snippets of the strict (left) and relaxed (right) versions of TSP.

```

This specific portion of code is executed at the beginning of the main recursive function of TSP and avoids the successive recursive calls to the main function when a thread finds a path that is larger than the global shortest path. The reason for allowing the mutex lock to be removed in this portion of code without creating data races is twofold. Firstly, concurrent threads only access this variable for read-only operations in this portion of code. Secondly, this variable can also be updated by concurrent threads (and those accesses are still protected by mutex locks) if a shorter path is found. However, when this occurs, the new value to be written will be inevitably lower than before. Thus, it does not invalidate previous results, since those previous paths continue to be greater or equal to this new value.

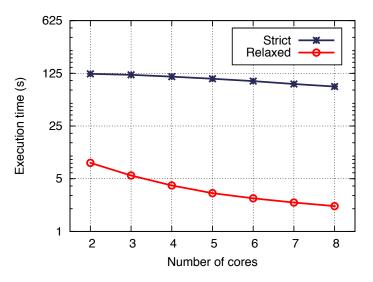

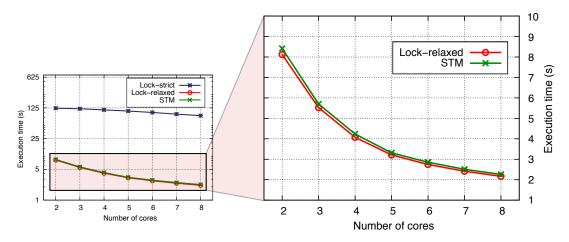

The execution times (in log scale) of these two approaches are shown in Figure 2.5. Results represent arithmetic means of 30 executions on the SMP-24: an SMP multicore platform based on four six-core Intel Xeon X7460 (we present a more detailed description of this platform in Section 5.1.1). In all experiments, we used the same seed for the pseudorandom number generator and a graph composed of 16 nodes.

Figure 2.5: Execution times of the two variations of TSP (strict vs. relaxed).

Considering the first approach, the results show high execution times and poor scalability. This occurs due to the large number of accesses to the shared variable minimum, causing threads to be blocked continuously. When we relaxed some synchronization on read-only accesses to this variable the performance was considerably increased. This is a simple example but it can be very hard to be sure that removing a lock to increase the application scalability will not break data consistency.

Due to all these issues concerning those traditional mechanisms, researchers are looking for alternative synchronization mechanisms. One of those that is attracting considerable attention of researchers is Transactional Memory.

#### 2.2 Transactional memory

The Transactional Memory programming model offers a new attractive way of developing parallel applications using a higher abstraction level. It shifts the problem of correct synchronization to the TM system, which is responsible for making sure that deadlocks will not occur, race conditions are correctly handled and locks are performed at a granularity which allows to indeed exploit the inherent parallelism of the application.

The original idea dates back to 1977, when *D. Lomet* realized that an abstraction similar to a database transaction might make a good programming language mechanism to ensure the consistency of data shared among several processes [Lom77]. Sixteen years later, in 1993, *M. Herlih* and *J. Moss* proposed a hardware-supported Transactional Memory as a mechanism for building lock-free data structures [HM93]. Since then, there has been a growing interest of researches on Transactional Memory.

This section aims at bringing up some important aspects of Transactional Memory. First, we present its general concepts. Then, we discuss the different design choices and approaches for implementing Transactional Memory. Finally, since we are interested in Software Transactional Memory in this thesis, we present a more detailed description of its peculiarities and we briefly describe the most known state-of-the-art STM systems.

#### 2.2.1 General concepts

The basic idea behind Transaction Memory comes from Transactional Database Management Systems (DBMS), in which a transaction is a sequence of actions that appears indivisible and instantaneous to an outside observer [GUW08]. In these systems, two or more queries conflict when different transactions perform read and write instructions over a database in such a way that the result could not arise from a sequential execution of the queries. In this context, transactions ensure that all

queries produce the same result as if they executed serially. A database transaction enforces some properties called **ACID**: atomicity, consistency, isolation and durability.

Atomicity refers to the ability of the DBMS to guarantee that either all tasks of a transaction are performed or none of them is performed. It is not acceptable for a constituent action to fail and for the transaction to finish successfully nor it is acceptable for a failed action to leave behind evidence that it executed [HLR10]. Thus, there are two possibilities for an executing transaction: it can be either committed (if it completes successfully) or aborted (if it fails).

Another important property is the **isolation**, which refers to the requirement that other operations cannot access (or see) the data in an intermediate state during a given transaction. Because of that, transactions must produce a correct result, regardless of which other transactions are executing concurrently.

The next property of a transaction is **consistency**. This property ensures that the database remains in a consistent state before starting a transaction and after finishing it (whether successful or not). Any data written to the database must be valid according to all defined rules, such as integrity constraints, cascades and triggers.

The final property is **durability**, which requires that once a transaction commits, its result must be permanent and available to subsequent transactions even in case of system failures. Many databases implement durability by writing all transactions into a transaction log that can be played back to recreate the system state right after a system failure.

It is important to mention that TM systems usually do not provide durability and consistency properties [LK08]. In general, TM systems assume that changes in memory need not be durable (mainly if the underlying system is not a persistent one) and they do not consider the previously mentioned consistency rules while modifying data inside transactions.

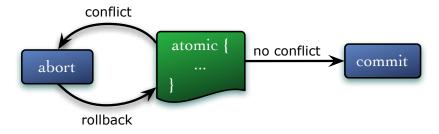

The basic concepts of Transactional Memory are illustrated in Figure 2.6. Transactions are sequences of steps (delimited by a blocks of code) executed by threads [HS08]. The way a transaction is defined inside the source code depends on the implementation. However, most compilers that support TM provide a simple **atomic** statement, which is responsible for executing the inner block of code (and the routines it invokes) as a transaction.

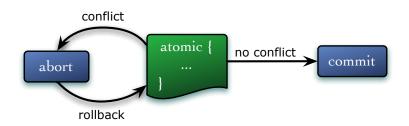

Figure 2.6: Transactional Memory basic concepts.

The portion of code written inside the atomic block is guaranteed to be executed atomically and in isolation regardless of eventual data races [Dal+10; HLR10]. At runtime, transactions are executed speculatively and the Transactional Memory continuously keeps track of concurrent accesses and detects conflicts. When a conflict arises, only one transaction involved in the conflict will **commit** whereas the others will be **aborted** and then re-executed (this action is also called *rollback*). When there is no conflict, all transactions are allowed to commit simultaneously.

Figure 2.7: Example of conflicting and non-conflicting scenarios.

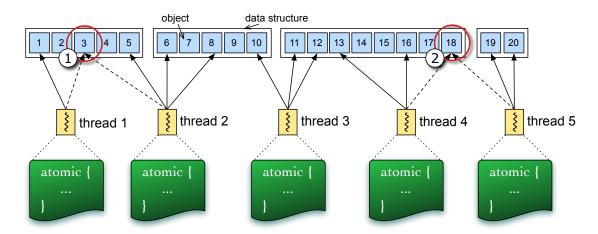

Figure 2.7 illustrates the use of Transactional Memory for guaranteeing atomicity while accessing shared data structures. In this example, there are five threads that read/write values from/to the objects of four shared structures (memory accesses are represented by arrows). In order to guarantee "atomic" accesses, each thread encapsulates all of its operations inside transactions (represented by the atomic

blocks). To simplify the example, we consider an object-based TM system, which can detect conflicts between transactions at object granularity. This means that conflicts may only occur when two or more transactions are accessing the same object at the same time and at least one transaction is modifying this object. We discuss other designs in more detail in Section 2.2.2.

As it can be noticed, there are some threads that access the same object. These accesses are represented by dashed arrows. More precisely, threads 1 and 2 access object **3** simultaneously (Scenario 1) whereas threads 4 and 5 access object **18** (Scenario 2). Let us consider these two different scenarios as read and write operations chronologically represented as follows:

- Scenario 1: no conflict (read-only transactions)

- 1. *thread 1* reads the objects [1, 3] and performs some computation;

- 2. *thread 2* reads the objects [3, 5, 6, 8] and performs some computation;

- 3. thread 2 commits;

- 4. thread 1 commits.

► Scenario 2: read-write conflict

- 1. thread 4 reads the objects [13, 16, 18] and performs some computation;

- 2. *thread* 5 reads the objects [18, 19, 20] and performs some computation;

- 3. *thread* 5 updates the object **18** (write operation);

- 4. *thread 4* aborts and rollbacks;

- 5. thread 5 commits.

In scenario 1, there are two read-only transactions accessing the same shared object **3** at the same time. In this case, the Transactional Memory mechanism can commit both transactions since they do not conflict.

On the contrary, a different situation arises in scenario 2. In this case, there is a conflict due to the fact that *thread 4* reads object **18** which is further updated by the transaction executed in *thread 5*. This conflict is solved automatically by the Transactional Memory, so the developer does not need to take care of it. One possible solution to solve such conflict is shown in steps 4 and 5. In this example,

#### 2.2. TRANSACTIONAL MEMORY

the write transaction in *thread 5* was committed and read-only transaction in *thread* 4 was aborted. Thus, the transaction in *thread 4* will be re-executed and will then use the new value updated by *thread 5*. The decision on what transaction to abort/commit can be different depending on the TM implementation. There exist different mechanisms to solve conflicts between transactions and each one has its pros and cons. We discuss some of the most used mechanisms later on.

It is important to notice in this example that some transactions also access disjoint elements of the shared structures without blocking on the shared structures. If locks were used to protect those concurrent accesses, it would be necessary to use one lock per shared element to obtain such fine granularity. Additionally, one would have to be very careful to not create deadlocks or livelocks. For instance, consider that two threads are trying to acquire two locks (*e.g.*, *l*1 and *l*2) to modify two elements of the shared structure atomically. A deadlock will happen if *thread* 1 acquires *l*1 and blocks on *l*2 due to the fact that *thread* 2 has already acquired *l*2 and is still blocked on *l*1. This problem can be solved by imposing a total order to acquire the locks. However, the problem is that it could limit the program scalability and will add complexity to the source code. These kind of problems are avoided by the Transactional Memory.

Although the Transactional Memory promises to simplify the development of parallel applications, it has also some limitations. For instance, transactions by themselves cannot replace all synchronization mechanisms in parallel programs [ML06]. Beyond mutual exclusion, synchronization is often used to coordinate independent tasks. In this context, Transactional Memory provides little assistance in coordinating independent tasks [LK08]. Forcing a thread to wait until a specific task is finished or limiting the number of threads performing a specific task are examples of such coordination mechanisms that are not implemented by the TM model.

#### 2.2.2 Design choices

Basically, there are four important criteria that must be taken into account while designing Transactional Memory systems: transaction granularity, version management, conflict detection and conflict resolution.

**Transaction granularity** is the unit of storage in which a TM system detects conflicts [HLR10]. For object-based languages, it is common to use **object granularity**, which detects conflicts when threads modify the state of objects. There are also other alternatives such as **word granularity** and **block granularity**. The former uses a memory word as the unit of conflict detection whereas the latter uses a group (block) of words. The chosen granularity can obviously impact the TM performance and it also influences the way it will be implemented by software and/or hardware.

The second important mechanism is **version management**. Since a transaction typically modifies data in memory, it is important to control how these modifications are managed. In general, TM systems use one of these two possible approaches: **direct update** (also known as *eager version management*) and **deferred update** (also known as *lazy version management*). If direct update is applied, the transaction directly modifies the data and the system uses some sort of concurrency control to prevent other transactions from concurrently modifying the object or committing after reading an old value. Direct update requires that the system record the original value, so it can be restored in case of transaction abortion. On the other hand, if deferred update is used, the data is modified in a private location and also read from there. This mechanism allows other transactions to modify their private data concurrently. When a transaction commits, it updates the data using the private copy. In case of abort, the transaction just discards this private copy.

The third important mechanism is **conflict detection**. Basically, a conflict can be detected as soon as it happens or postponed until a transaction commits. In the first approach, called *eager conflict detection*, read/write conflicts are detected as they occur during the transaction execution. In contrast, if *lazy conflict detection* is used, conflicts are only detected at commit-time. This reduces the overhead during the transaction execution at the cost of increasing the overhead on a commit operation.

As soon as a conflict is detected, a **conflict resolution** mechanism is invoked. There are many different algorithms that are used to select which transactions must be aborted in order to guarantee forward progress of the program. This task is usually addressed by the **contention manager**, which implements one or more **contention resolution policies** which determine whether conflicting transactions should abort, wait or proceed. Two common alternatives are to abort one of the conflicting transactions immediately (called suicide) or wait for a random, exponentially increasing, delay before restarting (called backoff). Obviously, the choice of which transaction must be aborted can also affect the performance of the system.

#### 2.2.3 Implementation approaches

The aforementioned design choices are the core of Transactional Memory. However, they can be implemented in three different ways: only in software, only in hardware or both. In the next sections, we discuss this subject, evaluating the pros and cons of each approach.

#### Software Transactional Memory

A Software Transactional Memory (STM) system implements all the transactional semantics in software. The advantage of STM for system programmers is that it offers flexibility in implementing different mechanisms and policies at the software level. Moreover, software is easier to modify and has fewer intrinsic limitations imposed by fixed-size hardware structures (*e.g.*, caches). There is also an important advantage for end users, since they can port their applications for Transactional Memory without needing extra specific hardware [HLR10].

However, STM has also some drawbacks, mainly with respect to performance. Since everything is implemented in software, STM usually presents higher overheads than traditional synchronization mechanisms. More precisely, this overhead is more evident when the application is running with low thread counts [Wam+12].

The performance of STM systems also depends on the workload. In general, STM systems present more expensive overheads than locks when a small number of processors is used. However, as the number of processors increases, the contention for a lock and the cost of locking also increase. When this occurs and conflicts are rare, STM systems have been showing comparable or even better results when compared to traditional locks [LK08]. We discuss this subject in more detail in Section 3.1.

In this thesis, we are interested in STM since it does not imply any specific hardware. We give a brief description of the most known state-of-the-art STM systems later on.

#### Hardware Transactional Memory

Contrary to the STM solution, Hardware Transactional Memory (HTM) implements all transactional functionalities in hardware (it manages data versions and tracks conflicts transparently). The basic idea behind HTM is to modify the modern cache-coherence protocols in order to implement transactions (in fact, they already detect and resolve synchronization conflicts between writers as well as between readers and writers).

Since the mechanisms are implemented in hardware, HTM systems intend to have a better performance when compared to STM systems. However, HTM faces several system challenges that are not an issue for STM implementations. The caches used to track the read set, write set and data versions have finite capacity and may overflow during a long transaction. Thus, many HTM systems make assumptions on hardware, such as maximum transactions size and Operational System support.

The interest in full hardware implementation of TM dates to the initial two papers on TM by *T. Knight* [Kni86] and *M. Herlihy* and *J. Moss* [HM93]. HTM systems usually do not require software instrumentation of memory references within transaction code.

A more recent example of HTM is the Log-based Transactional Memory (LogTM). It is a HTM system that makes commits fast by storing old values to a per-thread log in cacheable virtual memory and storing new values in place [Moo+06]. It extends the directory-based MOESI cache coherence protocol to enable both fast conflict detection and fast commit. The coherence protocol tracks addresses accessed inside transactions and participates in conflict detection. An improvement of LogTM called LogTM-SE was proposed in [Yen+07] to support thread suspension and migration.

#### Hybrid Transactional Memory

Even though recent STM systems scale considerably well, the overhead of the software systems can be significant [LK08]. On the contrary, HTM systems present better performance than STM systems but they have several limitations imposed by hardware. In this context, it emerges the Hybrid Transactional Memory (HyTM), which intends to tackle these issues.

The primary source of overhead for an STM system is the maintenance and validation of read sets. In few words, a transaction T can commit (or continue to execute) successfully if it meets two conditions: (i) no other concurrently executing transaction has modified some data that has been read by T and (ii) transaction

T is not modifying some data that another transaction is also modifying. To do so, the STM system tracks the data that has been read/written inside transactions and validates it at commit-time. This operations may have a high cost when many transactions modify a large amount of data.

In order to address the limitation of hardware resources (*e.g.*, cache capacity), a transaction can start in the HTM mode using hardware mechanisms for conflict detection and version management. If HTM resources are exceeded, the transaction is rolled back and restarted in STM mode with additional instrumentation. However, the main challenge in such hybrid systems is to detect conflicts between transactions started in HTM mode and transactions started in STM mode.

In [Kum+06], the authors describe a HyTM solution that uses a hardware mechanism as long as transactions do not exceed resource limits and falls back to a software mechanism when those limits are exceeded. This approach combines the performance benefits of a pure hardware scheme with the flexibility of a pure software scheme. The hardware mechanism tracks transactionally accessed data at the cache line granularity, while the software scheme tracks it at the object granularity. It uses a simple strategy to choose between HTM and STM: if the transaction fails to commit successfully within three attempts in HTM mode, it falls back into STM mode and retries until it succeeds.