N° d'ordre NNT : 2023ISAL0046

### THÈSE DE DOCTORAT DE L'INSA LYON Membre de l'Université de Lyon

École Doctorale 512 Informatique et Mathématiques

Spécialité / Discipline de doctorat : Informatique

Soutenue publiquement le 29/06/2023, par : Luc Forget

# Description and compilation of ad-hoc arithmetic operators in the context of High-Level Synthesis.

Devant le jury composé de :

| RASTELLO Fabrice                                                            | Directeur de recherches                                                                                        | INRIA Grenoble                                                             | Président                                                |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------|

| DERRIEN Steven<br>FERRANDI Fabrizio<br>CHOTIN Roselyne<br>VOLKOVA Anastasia | Professeur des Universités<br>Professeur des Universités<br>Maître de Conférences HDR<br>Maître de Conférences | Université de Rennes<br>Politecnico Milano<br>LIP6<br>Université de Nantes | Rapporteur<br>Rapporteur<br>Examinatrice<br>Examinatrice |

| DE DINECHIN Florent                                                         | Professeur des Universités                                                                                     | INSA de Lyon                                                               | Directeur de thèse                                       |

# Département FEDORA – INSA Lyon – Écoles Doctorales

| Sigle     | École doctorale                                                             | Nom et coordonnées du responsable                         |

|-----------|-----------------------------------------------------------------------------|-----------------------------------------------------------|

| oigie     |                                                                             | *                                                         |

|           | Chimie de Lyon                                                              | M. Stéphane DANIELE                                       |

|           | https://www.edchimie-lyon.fr                                                | C2P2-CPE LYON-UMR 5265                                    |

| CHIMIE    | Sec: Renée El Melhem                                                        | Bâtiment F308 bP 2077<br>42 Roulevard du 11 novembre 1018 |

|           | <i>Bât:</i> Blaise Pascal, 3ème étage                                       | 43 Boulevard du 11 novembre 1918<br>69616 Villeurbanne    |

|           | Tél: 04 72 43 80 46                                                         | <i>Tél:</i> 04 72 44 53 60                                |

|           | secretariat@edchimie-lyon.fr                                                | directeur@edchimie-lyon.fr                                |

|           | Électronique, Électrotechnique, Automatique                                 | M. Philippe Delachartre                                   |

|           | https://edeea.universite-lyon.fr                                            | Laboratoire Creatis                                       |

|           | Sec: Stéphanie Cauvin                                                       | Bâtiment Blaise Pascal                                    |

| E.E.A.    | <i>Bât:</i> Direction INSA Lyon                                             | 7 avenue Jean Capelle                                     |

|           |                                                                             | 69621 Villeurbanne CEDEX                                  |

|           | <i>Tél:</i> 04 72 43 71 70                                                  | <i>Tél:</i> 04 72 43 88 63                                |

|           | secretariat.edeea@insa-lyon.fr                                              | philippe.delachartre@insa-lyon.fr                         |

|           | Évolution, Écosystème, Microbiologie,<br>Modélisation                       | Mme Sandrine Charles                                      |

|           |                                                                             | Université Claude Pernard I von 1                         |

| E2M2      | http://e2m2.universite-lyon.fr<br><i>Sec:</i> Bénédicte Lanza               | Université Claude Bernard Lyon 1<br>UFR Biosciences       |

|           | Bât: Atrium, UCB Lyon 1                                                     | 43 boulevard du 11 Novembre 1918                          |

|           | ,)                                                                          | 69622 Villeurbanne CEDEX                                  |

|           | <i>Tél:</i> 04 72 44 83 62                                                  | Tél:                                                      |

|           | <pre>secretariat.e2m2@univ-lyon1.fr</pre>                                   | <pre>sandrine.charles@univ-lyon1.fr</pre>                 |

|           | Interdisciplinaire Sciences-Santé                                           | Mme Sylvie Ricard-Blum                                    |

|           | http://ediss.universite-lyon.fr                                             | ICBMS - UMR 5246 CNRS - Université Lyon 1                 |

| EDISS     | Sec: Bénédicte Lanza                                                        | Bâtiment Raulin - 2ème étage Nord                         |

| LDI33     | <i>Bât:</i> Atrium, UCB Lyon 1                                              | 43 boulevard du 11 Novembre 1918                          |

|           |                                                                             | 69622 Villeurbanne CEDEX                                  |

|           | <i>Tél:</i> 04 72 44 83 62                                                  | Tél: 04 72 44 82 32                                       |

|           | secretariat.ediss@univ-lyon1.fr                                             | sylvie.ricard-blum@univ-lyon1.fr                          |

|           | Informatique et Mathématiques                                               | M. Hamamache Kheddouci                                    |

|           | http://edinfomaths.universite-lyon.fr                                       | Université Claude Bernard Lyon 1                          |

| INFOMATHS | <i>Sec:</i> Renée El Melhem<br><i>Bât:</i> Bâtiment Blaise Pascal, 3e étage | Bâtiment Nautibus<br>43 boulevard du 11 Novembre 1918     |

|           | Dut. Datiment Diaise i ascai, se etage                                      | 69622 Villeurbanne CEDEX                                  |

|           | <i>Tél:</i> 04 72 43 80 46                                                  | <i>Tél:</i> 04 72 44 83 69                                |

|           | infomaths@univ-lyon1.fr                                                     | hamamache.kheddouci@univ-lyon1.fr                         |

|           | Matériaux de Lyon                                                           | M. Stéphane Benayoun                                      |

|           | http://edinfomaths.universite-lyon.fr                                       | École Centrale de Lyon                                    |

| Matériaux | Sec: Yann De Ordenana                                                       | Laboratoire LTDS                                          |

| Materiaux | Bât:                                                                        | 36 avenue Guy de Collongue                                |

|           |                                                                             | 69134 Ecully CEDEX                                        |

|           | <i>Tél:</i> 04 72 18 62 44                                                  | <i>Tél:</i> 04 72 18 64 37                                |

|           | yann.de-ordenana@ec-lyon.fr                                                 | stephane.benayoun@ec-lyon.fr                              |

|           | Mécanique, Énergétique, Génie Civil, Acoustique                             | M. Jocelyn Bonjour                                        |

|           | http://edmega.universite-lyon.fr                                            | INSA Lyon                                                 |

| MEGA      | Sec: Stéphanie Cauvin                                                       | Laboratoire CETHIL – Bâtiment Sadi-Carnot                 |

|           | <i>Bât:</i> Direction INSA Lyon                                             | 9 rue de la Physique<br>69621 Villeurbanne CEDEX          |

|           | <i>Tél:</i> 04 72 43 71 70                                                  | Tél: /                                                    |

|           | mega@insa-lyon.fr                                                           | jocelyn.bonjour@insa-lyon.fr                              |

|           | Sciences Sociales: Histoire, Géo., Aménagement,                             |                                                           |

|           | Urbanisme, Archéo., Science po., Socio., Anthropo.                          | M. Bruno Milly                                            |

| ScSo      | https://edsciencessociales.universite-lyon.fr                               | Université Lumière Lyon 2                                 |

| 0000      | Sec: Mélina Faveton & J.Y. Toussaint (INSA)                                 |                                                           |

|           | Bât:                                                                        | 86 Rue Pasteur                                            |

|           | Tél: 04 78 69 72 79                                                         | 69365 Lyon CEDEX 07<br><i>Tél:</i>                        |

|           | 121:04 78 69 72 79<br>melina.faveton@univ-lyon2.fr                          | <i>let:</i><br>christian.montes@univ-lyon2.fr             |

|           | mering.raveroneuniv-tyon2.11                                                | CHIISTIAH.HOHLESWUHIV-IYOHZ.II                            |

# Résumé

Les techniques de synthèse de haut niveau permettent aux programmeurs non spécialistes de générer des descriptions de circuits numériques en utilisant des langages de programmation généralistes. Cependant, les outils existants ne supportent qu'un petit nombre de formats numériques et un petit nombre d'opérateurs standards. Cette thèse présente plusieurs techniques pour rajouter le support de nouveaux formats et de nouveaux opérateurs. Dans un premier temps, l'étude se focalise sur ce qui est réalisable en se restreignant aux fonctionnalités de métaprogrammation du standard C++ supporté par les outils HLS. Une bibliothèque d'opérateurs élémentaires pour les formats IEEE-754 et posit de taille arbitraire est proposée. Elle sert de base à une étude de cas comparant le coût matériel de l'implémentation de ces deux formats. L'implémentation d'évaluateurs de fonctions mathématiques arbitraires se heurte aux limites de la première approche. Dans un second temps, l'étude se porte sur les possibilités offertes par la modification du flot de compilation HLS, avec comme objectif de supporter cette fonctionnalité. Une bibliothèque permettant au développeur de spécifier des opérateurs pour approximer des fonctions arbitraires en précision arbitraire est présentée. Deux approches pour l'interfaçage de cette bibliothèque avec les outils de HLS sont proposées, selon que l'on a ou pas accès aux sources des compilateurs HLS.

## Abstract

High-level synthesis allows non-specialist software developers to generate digital circuit descriptions using high-level programming languages. However, existing tools support only few numerical formats and standard arithmetic operators. This thesis introduces many technics to support new formats and new operators. First, the study focuses on what is doable using only the C++ meta-programming constructs supported by main HLS tools. A library of elementary operations for IEEE-754 and posit formats of arbitrary sizes is introduced. It is used as a support to compare the hardware cost of implementing these formats. The implementation of evaluators of arbitrary mathematical functions reaches the limit of the meta-programming approach. A second step is then to study the possibility that are brought by modifying the HLS compile flow. Implementing arbitrary function evaluator is the objective of this study. A library allowing developers to specify operators that approximate arbitrary functions at arbitrary precision is introduced. Two methods are developed to interface this library with the HLS tools, depending on whether the HLS compiler sources can be modified.

### Acknowledgement

It has been a real pleasure to work on this thesis. While there have been many ups and downs along the way<sup>1</sup>, it has been an interesting journey, and many people have contributed making the interesting part of it more interesting, and the least enjoyable parts, well, less less enjoyable.

Among these people I would like to thank my supervisor, Florent de Dinechin, for the many insightful discussions and the support I could get from him, starting from my first internship on FloPoCo up to the end of the thesis defense.

I am also grateful to Ronan and Gauthier, who I enjoyed working with at Xilinx/AMD. In addition to providing interesting points of view on software development, they have been of great help for the development of the different backends for MArTo arbitrary function support.

I am not sure if I need to be grateful to SARS-CoV-2 without which I would probably not have met them.

I am also thankful to 小泉さん, my former supervisor at NTT Multimedia Intelligence Laboratory, for his advice about perseverance and failure relativization, which proved very valuable these last few years.

Working on this thesis wouldn't have been half as nice without the good mood of the office. So thank you to Agathe, Benoît, Diane, Lélio, Marie, Matthias, Orégane, and Pierre for being such nice colleagues!

While I am of course grateful to all my family, a special mention goes to my brother and sister for their continuous support. Another one for the logistic support I received from my parents and my family in Lyon.

He (probably) did not do it on purpose, but Mochi has also been of a great help. Indeed, real-life cats are clearly underrated compared to rubber ducks for debugging purposes.

Finally, despite their constant efforts to give me more time to work on the manuscript, I do *not* thank the SNCF.

<sup>&</sup>lt;sup>1</sup>The interested reader can discover the (terrible ((Ph.D. student) universe)) in the abundant related literature on the web.

## Contents

| In | trod | uction |                                                          | 1  |

|----|------|--------|----------------------------------------------------------|----|

| 1  | Con  | text   |                                                          | 5  |

|    | 1.1  | Logic  | signals, logic vectors                                   | 5  |

|    | 1.2  |        | erical formats                                           | 6  |

|    |      | 1.2.1  | Fixed-point                                              | 8  |

|    |      | 1.2.2  | Floating point                                           | 14 |

|    |      | 1.2.3  | Logarithmic Number System                                | 26 |

|    | 1.3  | Hardy  | ware arithmetic operators                                | 27 |

|    | 1.4  | Field- | Programmable Gate Arrays                                 | 28 |

|    |      | 1.4.1  | FPGA architecture                                        | 28 |

|    |      | 1.4.2  | Computing with FPGAs                                     | 32 |

|    |      | 1.4.3  | From computation graph to FPGA configuration             | 33 |

|    |      | 1.4.4  | Computation graph descriptions                           | 34 |

|    | 1.5  | High-  | Level Synthesis arithmetic support                       | 39 |

|    |      | 1.5.1  | HDL arithmetic core generators                           | 40 |

|    |      | 1.5.2  | Toward on-demand HLS arithmetic operator implemen-       |    |

|    |      |        | tation?                                                  | 40 |

| 2  | A p  | ortabl | e HLS-enabled library for custom numerical formats       | 43 |

|    | 2.1  | Hint,  | a portable abstraction layer for arbitrary width integer |    |

|    |      | arithr | netic                                                    | 43 |

|    |      | 2.1.1  | Integers and HLS                                         | 43 |

|    |      | 2.1.2  | Core arithmetic primitives for floating-point operators  | 46 |

|    |      | 2.1.3  | Type safety for arbitrary-precision integers in HLS      | 48 |

|    |      | 2.1.4  | Others operations                                        | 50 |

|    |      | 2.1.5  | Software design of backend common interface              | 51 |

|    |       | 2.1.6   | Evaluation                                                 | 53  |

|----|-------|---------|------------------------------------------------------------|-----|

|    | 2.2   | Custo   | m floating-point format library                            | 57  |

|    |       | 2.2.1   | Elementary operation support                               | 57  |

|    |       | 2.2.2   | Exact fixed-point accumulation of floating-points products | 58  |

|    |       | 2.2.3   | Operator implementations in MArTo                          | 60  |

|    | 2.3   | IEEE-   | 754 vs posit hardware cost comparison                      | 73  |

|    |       | 2.3.1   | Comparison of operator area and latency                    | 74  |

|    |       | 2.3.2   | Quire versus standard operations                           | 81  |

|    |       | 2.3.3   | Case study conclusion                                      | 82  |

|    | 2.4   | Limits  | s and future work                                          | 83  |

| 3  | HLS   | librai  | ry for arbitrary fixed-point function approximations       | 85  |

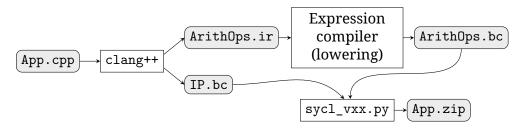

|    | 3.1   |         | m C++ HLS compiler supporting C++20                        | 86  |

|    | 3.2   |         | ary to specify arithmetic operators                        | 87  |

|    |       |         | C++ types for fixed-point number                           | 88  |

|    |       | 3.2.2   | Classical arithmetic computations                          | 89  |

|    |       | 3.2.3   | Arbitrary mathematical function specification via its ex-  |     |

|    |       |         | pression graph                                             | 90  |

|    | 3.3   | Fixed   | -point function approximation architectures                | 92  |

|    |       | 3.3.1   | Table-based hardware arithmetic operators                  | 92  |

|    |       | 3.3.2   | Polynomial approximation methods                           | 93  |

|    | 3.4   | Comp    | iler agnostic specialization generator method              | 93  |

|    |       | 3.4.1   | C++ types for arithmetic operator evaluation               | 94  |

|    |       | 3.4.2   | Application example                                        | 97  |

|    |       | 3.4.3   | Limits of the approach by specialization generation        | 101 |

|    | 3.5   | Comp    | iler support for fixed-point functions in HLS              | 103 |

|    |       | 3.5.1   | Fixed-point function compilation architecture              | 103 |

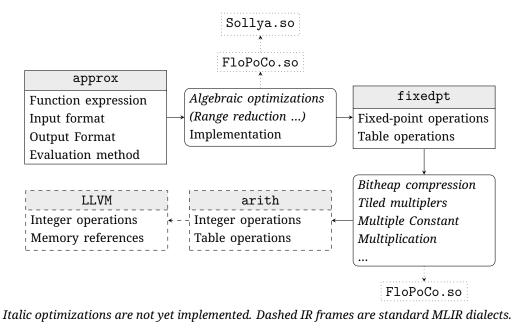

|    |       | 3.5.2   | Intermediate representations for fixed-point functions     | 104 |

|    |       | 3.5.3   | Current state of the expression compiler prototype         | 107 |

| Co | onclu | sion a  | nd perspectives                                            | 109 |

| A  | Sou   | rce co  | de for floating-point adders                               | 113 |

|    | A.1   | IEEE-'  | 754 Adder                                                  | 113 |

|    | A.2   | Posit a | adder                                                      | 120 |

# List of Figures

| 1.1  | Representable values and rounding function illustration for ex-           |    |

|------|---------------------------------------------------------------------------|----|

|      | ample format of table 1.1                                                 | 7  |

| 1.2  | Binary positional notation of 42.75                                       | 8  |

| 1.3  | Superposition of two fixed-point representation windows with              |    |

|      | the infinite positional representation                                    | 9  |

| 1.4  | Visualization of representable values for two 5-bits unsigned             |    |

|      | fixed-point formats                                                       | 10 |

| 1.5  | Decomposition of a signed fixed-point format with $m = 5$ and $l = -4$    | 10 |

| 1.6  | Visualization of representable for the two signed fixed-point             |    |

|      | schemes with $m = 1$ and $l = -3$ . Scheme-specific representable         |    |

|      | values are circled in red                                                 | 12 |

| 1.7  | Binary and binary-coded octal positional notation of 42.75                | 13 |

| 1.8  | Binary-coded decimal positional notation of 42.75                         | 13 |

| 1.9  | Basic floating-point representation of 42.75 as 0.333984375 $\times2^7$ . | 15 |

| 1.10 | Unique IEEE-754 binary16 representation of 42.75                          | 17 |

| 1.11 | Subtraction of two floating-point values of minimal normal ex-            |    |

|      | ponent $E_{\min}$                                                         | 20 |

| 1.12 | Bound on relative-error magnitude for IEEE-754 binary16 rep-              |    |

|      | resentable range.                                                         | 22 |

| 1.13 | Representable values for mainstream 16bit IEEE-like formats on            |    |

|      | $[1, 1 + 2^{-5}]$                                                         | 23 |

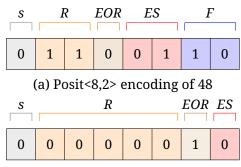

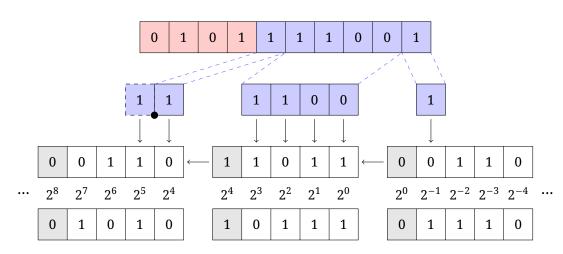

| 1.14 | Posit<8,2> representations decomposition                                  | 24 |

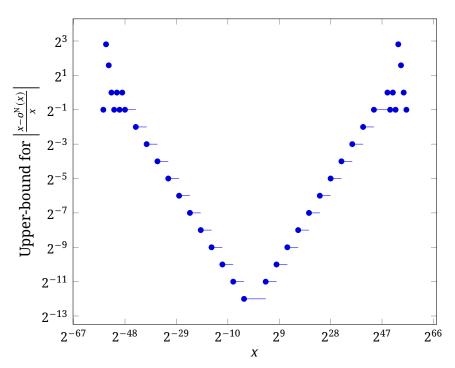

| 1.15 | Bound on relative-error magnitude for posit<16,2> repre-                  |    |

|      | sentable range                                                            | 25 |

| 1.16 | Representable positive values of an LNS system with represen-             |    |

|      | tation of the exponent being a sfix $(2, -3)$ .                           | 26 |

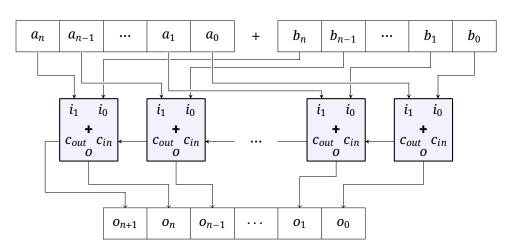

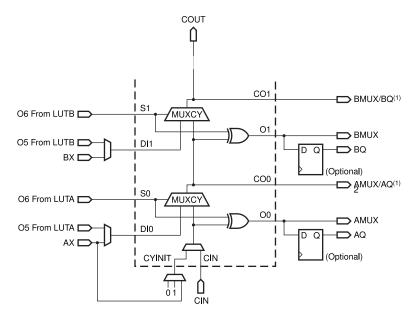

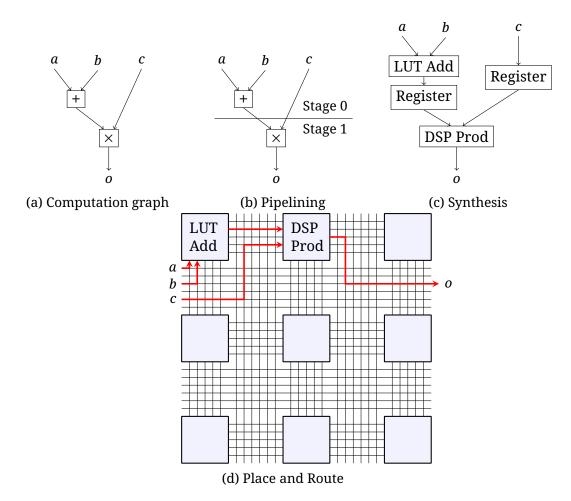

| 1.18 | Part of the schematic of the UltraScale fast carry chain Schematic representation of the compilation stages from com- | 31<br>32<br>34 |

|------|-----------------------------------------------------------------------------------------------------------------------|----------------|

|      | putation graph to logical FPGA primitive netlist                                                                      | 34             |

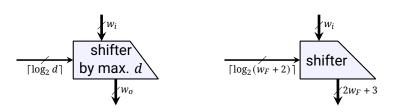

| 2.1  | A generic shifter (left) instantiated (right) in a floating-point                                                     |                |

|      | 1                                                                                                                     | 47             |

| 2.2  | 0                                                                                                                     | 47             |

| 2.3  | Example of product accumulation on the carry-save banks of a                                                          |                |

|      | Kulisch-like accumulator.                                                                                             | 59             |

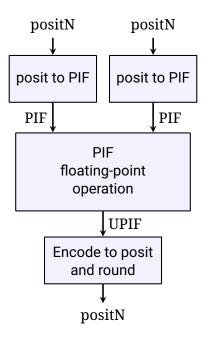

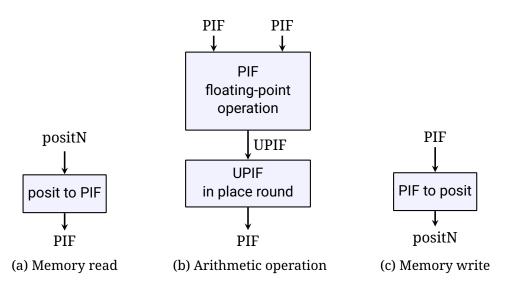

| 2.4  | Architecture of a posit operator in a Posit Arithmetic Unit that                                                      |                |

|      | uses posit registers and posit-to-posit operators                                                                     | 62             |

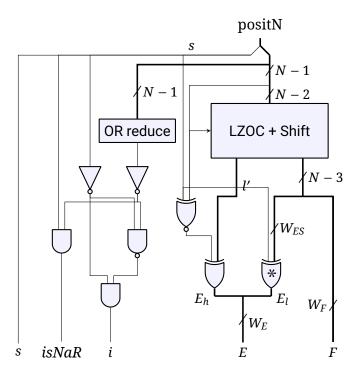

| 2.5  | Architecture of a posit to PIF decoder                                                                                | 65             |

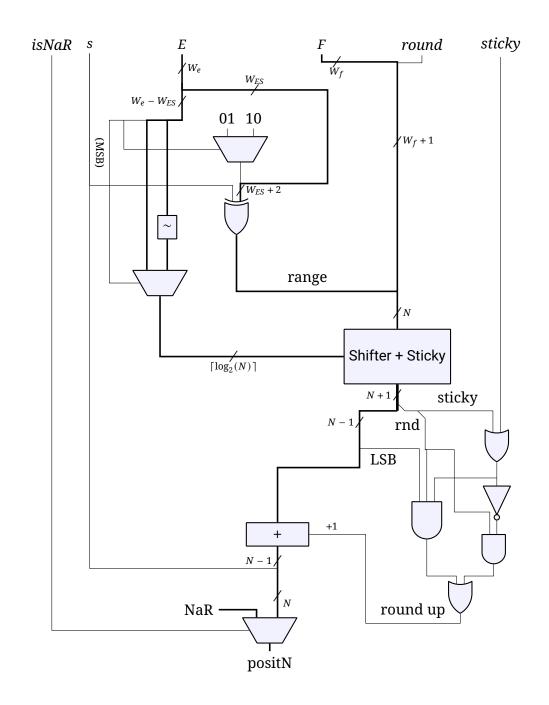

| 2.6  | Architecture of a UPIF to posit encoder. The PIF to posit encoder                                                     |                |

|      | is similar, with the round and sticky logic (including the final                                                      |                |

|      | adder) removed                                                                                                        | 67             |

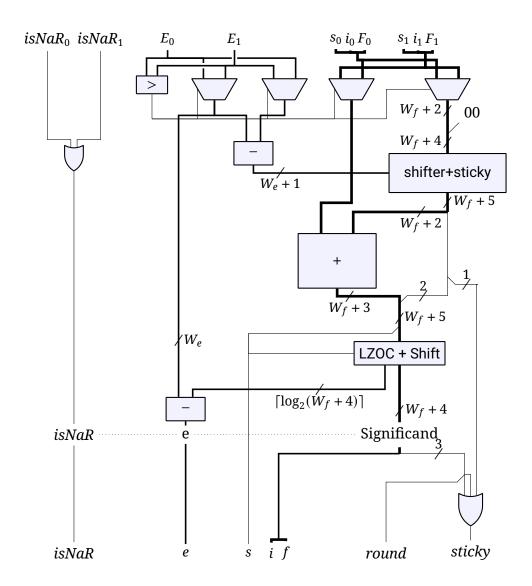

| 2.7  | Architecture of a PIF adder. Exponent comparison block de-                                                            |                |

|      | noted with ">" also takes the operand <i>i</i> and <i>s</i> bits to detect zero                                       |                |

|      | values, but wires have been omitted here for clarity.                                                                 | 68             |

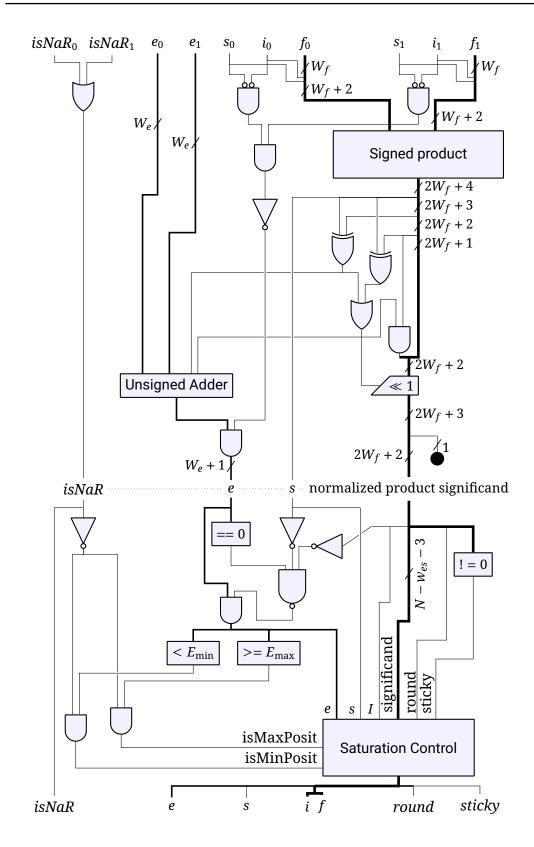

| 2.8  | Architecture of a PIF multiplier.                                                                                     | 69             |

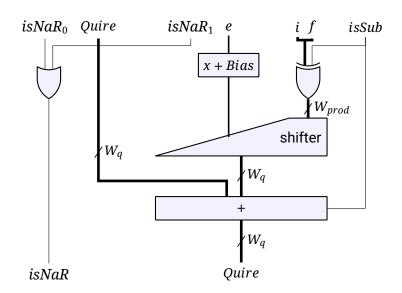

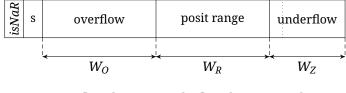

| 2.9  |                                                                                                                       | 71             |

|      | The bits of a standard quire                                                                                          | 72             |

| 2.11 | Architecture of a PAU using posits as a memory-only encoding,                                                         |                |

|      | with PIF registers and PIF-to-PIF operators                                                                           | 74             |

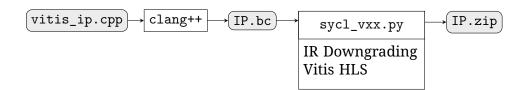

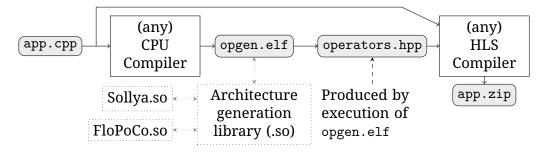

| 3.1  | Custom C++ HLS compiler stages                                                                                        | 87             |

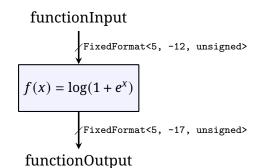

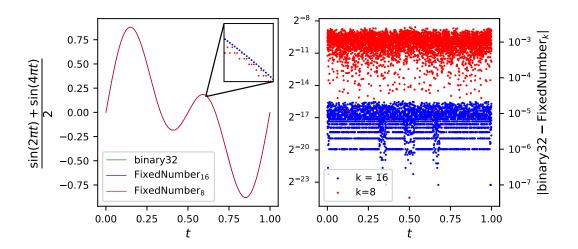

| 3.2  | Example of function evaluator (here corresponding to listing 3.3).                                                    |                |

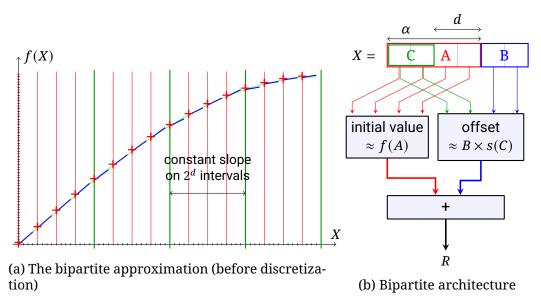

| 3.3  | Example bipartite approximation architecture, here replacing a                                                        |                |

|      |                                                                                                                       | 93             |

| 3.4  | Architecture of the generator of template specializations                                                             |                |

| 3.5  | Output of an additive synthesis with two frequencies of equal                                                         |                |

|      | amplitudes and the computational error (as absolute difference                                                        |                |

|      |                                                                                                                       | 99             |

| 3.6  | Architecture diagram of fixed-point function extracting compiler.1                                                    | .03            |

| 3.7  | IR and optimization used in the process of lowering high-level                                                        |                |

|      | operator specifications to implementation details 1                                                                   | .04            |

|      |                                                                                                                       |                |

# List of Tables

| 1.1  | Example of an arbitrary numerical format on 2-bits vectors         | 6  |

|------|--------------------------------------------------------------------|----|

| 1.2  | Field widths for IEEE-754 standard formats                         | 16 |

| 1.3  | Interpretation of IEEE-754 binary16 encoding                       | 19 |

| 1.4  | Precision - dynamic - special-value representation trade-off for   |    |

|      | mainstream 16 -bit IEEE-like floating-point formats                | 23 |

| 1.5  | LUT content for evaluating a 4:1 multiplexer                       | 29 |

| 1.6  | Full-adder truth table.                                            | 31 |

| 2.1  | Synthesis of LZC Arria 10 (achieved clock target of 240MHz)        | 54 |

| 2.2  | Synthesis of LZC and shifters on Kintex 7 (achieved target delay   |    |

|      | of 3ns). The number are obtained with Vitis 2022.2                 | 54 |

| 2.3  | Synthesis of shifters+sticky on Arria 10 (achieved clock target of |    |

|      | 240MHz)                                                            | 55 |

| 2.4  | Synthesis of shifters+sticky on Kintex 7 (achieved target of 3ns)  | 55 |

| 2.5  | Synthesis of normalizers Arria 10 (achieved clock target of        |    |

|      | 240MHz)                                                            | 56 |

| 2.6  | Synthesis of normalizers on Kintex 7 (achieved target delay of     |    |

|      | 3ns)                                                               | 56 |

| 2.7  | Parameters of standard posit formats.                              | 61 |

| 2.8  | Quire bit-width parameters for standard 3.2 posit formats          | 70 |

| 2.9  | Comparison with [34] for standard posit addition and product .     | 76 |

| 2.10 | Comparison with [33] on standard posit addition and product .      | 76 |

| 2.11 | Comparison with [35] on posit<32,6> addition and product           | 77 |

| 2.12 | Comparison with [50] for standard posit addition and product .     | 77 |

| 2.13 | Synthesis results of combinatorial operators                       | 79 |

| 2.14 | Synthesis results of pipelined operators                           | 80 |

| 2.15 | Synthesis results for a sum of 1000 products (U: Unsegmented,                                                                                                                                                                                       |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | S32 and S64: Segment sizes of 32 and 64 bits)                                                                                                                                                                                                       | 81  |

| 2.16 | Detailed synthesis results of hardware posit quire                                                                                                                                                                                                  | 83  |

| 3.1  | Area and timing metrics comparison between float and various FixedNumber for an additive synthesizer of 256 oscillators. II stands for Initiation Interval, the number of clock cycles that pass before the pipeline is ready to be fed a new input | 100 |

# List of Listings

| 1.1 | Verilog description of a circuit computing $(a + b) \cdot c$ for 12-bits                                                                        |          |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|     | inputs                                                                                                                                          | 35       |

| 1.2 | Chisel description of a circuit computing $(a+b) \cdot c$ for 12-bits inputs.                                                                   | 36       |

| 1.3 | HLS C++ description of a circuit computing $(a + b) \cdot c$ .                                                                                  | 37       |

| 1.4 | Simultaneous definition and call of an FPGA kernel computing                                                                                    |          |

|     | $(a+b) \cdot c. \ldots $ | 38       |

| 1.5 | HLS C++ description of a circuit computing $(a+b) \cdot c$ with 12-bits                                                                         |          |

|     | inputs                                                                                                                                          | 39       |

| 1.6 | Flopoco command line to produce an IEEE-754 binary32 Fused                                                                                      |          |

|     | Multiply Add operator for Kintex 7 architecture                                                                                                 | 40       |

| 2.1 | Example of a counter-intuitive C intermediate result type                                                                                       | 45       |

| 2.1 | Undefined behavior on shifts.                                                                                                                   | 45<br>46 |

| 2.2 | Example of hint code computing the leading-zero count of the                                                                                    | 10       |

| 2.0 | sum of two 6-bits integers provided concatenated in a 12-bits                                                                                   |          |

|     | vector.                                                                                                                                         | 48       |

| 2.4 | Pure function wrapping call to the slice template method                                                                                        | 52       |

| 2.5 | Pure function wrapping call to the slice template method with                                                                                   |          |

|     | cleaner interface using C++20 concepts.                                                                                                         | 52       |

| 2.6 | Rewriting of example from listing 2.3 with proposed interface                                                                                   |          |

|     | improvement.                                                                                                                                    | 53       |

| 2.7 | MArTo code example                                                                                                                              | 57       |

| 2.8 | MArTo code example                                                                                                                              | 58       |

|     |                                                                                                                                                 | ~ ~      |

| 3.1 | Construction of a FixedNumber from its representation                                                                                           | 88       |

| 3.2 | Format inference in the fixed-point library.                                                                                                    | 89       |

| 3.3  | Construction of the expression tree corresponding to $f(x) =$                      |

|------|------------------------------------------------------------------------------------|

|      | $log(1 + e^x)$ (lines 4-6), and construction of an operator for this               |

|      | function (line 7)                                                                  |

| 3.4  | Simple example of template specialization and dispatching 96                       |

| 3.5  | Outline of the generic ArithOp template class                                      |

| 3.6  | Simplified example of generated ArithOp specialization for                         |

|      | $log(1 + e^x)$ with output format ufix(5, -17)                                     |

| 3.7  | A simplified LNS adder                                                             |

| 3.8  | Example of expression sharing the same type but representing                       |

|      | distinct expression tree due to the lack of variable instance type                 |

|      | identifying mechanism                                                              |

| 3.9  | C++ specification of an operator approximating $x \mapsto \sin(0.5 * x * \pi).105$ |

| 3.10 | High level representation of operator of listing 3.9 using the                     |

|      | approx dialect                                                                     |

| 3.11 | Implementation of listing 3.9 operator in terms of fixed-point                     |

|      | operations described in fixedpt dialect 105                                        |

| 3.12 | LLVM IR corresponding to the implementation of listing 3.9 106                     |

| A.1  | MArTo code for the IEEENumber class                                                |

| A.2  | MArTo code for an IEEE-754 adder                                                   |

| A.3  | MArTo code for the posit to pif decoder                                            |

| A.4  | MArTo code for the PIF to posit encoder                                            |

| A.5  | MArTo code for a posit adder 124                                                   |

### Introduction

Transistor density on integrated circuits has stopped to follow Moore's law predictions around year 2010. This is around the same time that clock rate ceased to be improved by new generations of central processing units (CPU). As a result, the main selling point of new generations of desktop and server CPUs has shifted towards more parallelism and more hardwaresupported operations. Compute-intensive applications benefit from these two improvements. Indeed, hardware-accelerated mathematical functions and fine-grained parallelism (such as Single Instruction Multiple Data (SIMD) operations or dynamic reordering of instructions for superscalar execution) reduce the runtime of one kernel iteration, while coarse-grain parallelism (through multiple cores or simultaneous multithreading) allows running multiple independent kernel invocations simultaneously, hence reducing the total execution time.

However, the set of numerical formats and operations supported by CPUs does not necessarily fit tightly the application needs. Moreover, computation kernels might expose some parallelism at a degree that cannot be handled properly via CPUs.

In order to further accelerate applications suffering from this kind of CPU limitations, application-specific integrated circuits (ASIC) can be developed. Two main barriers limit this development. The first one consists in the fixed costs associated with custom integrated circuit production. This barrier can be lowered by using Field-Programmable Gate Arrays (FPGAs) instead of ASICs, at the price of some performance loss. The second barrier, common to ASIC and FPGAs, is the required expertise needed to design those circuits.

Lowering the requested experience to develop this kind of hardware is one of the objectives of High-Level synthesis tools. These tools allow building a circuit from a high-level behavioral description written in a classical programming language, such as C++. This thesis focuses on these tools.

While HLS tools allow software developers to write circuits easily, their support for numerical formats and mathematical functions is limited to those provided by the source language. For instance, the only floating-point formats supported by C++-based HLS tools are the 32-bits and 64-bits IEEE-754 formats float and double. Yet, using application-specific numerical formats and operators is a way to improve the quality of results (QoR, which regroups design latency and surface) of circuit designs. For instance, as elementary operations on narrower formats operate on smaller bit vectors, their latency is reduced compared to the same operation on wider a format. Besides, they also occupy less chip area, which leaves more space for packing more operators on the chip. This eventually allows running more operations in parallel. Using for each computation the narrowest format that still allows to verify the overall application accuracy constraint is then a good way to optimize this application.

The work presented in this thesis aims at providing support for custom numerical formats and operators in an HLS context. This support takes the form of a portable library, MArTo, that a developer can exploit to define and use custom numerical types in HLS code. This library supports both IEEE-754 and posit numerical formats, which are presented along with other numerical formats, arithmetic operator formalization and FPGA architecture in chapter 1. Using the MArTo allows fast evaluation of the performance/accuracy trade-off entailed by the usage of a given numerical for a given application. MArTo is built on top of a second library, hint, that abstract operations on arbitrary size integers. Both of these libraries use C++ meta-programming constructs that are supported by HLS tools to implement the basic arithmetic operations of the supported formats. This design and the usage of the two libraries is further detailed in chapter 2, which also present a case study comparing the implementation cost of the two supported floating-point formats, IEEE-754 and posit.

A second optimization opportunities with regard to computation is the evaluation of mathematical functions. When only a limited set of mathematical functions is provided to the user (as it is the case with the C libm library), evaluating a composed function such as  $x \mapsto \cos(\sin(x))$  requires composing evaluation of library-supported functions (computing  $\sin(x)$  first, before evaluating cos on the result for the example function). However, ad-hoc function evaluators can be implemented to evaluate directly arbitrary expressions, allowing reduced latency and better control on precision compared to the composition approach. While generating such evaluators is a well studied problem, especially when both input and output format of the evaluator is fixed-

point, this functionality is not supported by HLS tools.

The architecture of such evaluators require pre-computed values, such as coefficients of a polynomial approximating the function to evaluate. Obtaining these values is non-trivial, which prevent computing them in a pure metaprogrammatic fashion. Instead, it is more desirable to use existing tools that can provide state-of-the-art evaluation plans for arbitrary functions. However, evaluation plan has to be determined before performing the HLS compilation step.

Two methods to modify the HLS compilation flow are described in chapter 3. The first approach does not require direct modification of the HLS compiler. This makes it quite portable, but it requires that extra compilation steps are performed by the user, and it suffers from some fundamental limitations. The second approach consists in adding built-in support for arbitrary expression evaluation directly in the compiler. This method solves the issues of the first approach, but is not portable anymore. This disadvantage is attenuated by using a compiler-independent expression compiler that can be used by multiple HLS compilers.

Evaluation of arbitrary function is only one of the many possible optimized high-level primitives that could be made available to HLS developers, while providing automatic optimized implementation generation. Some perspective on building such "Real High-Level Synthesis" systems are discussed in the conclusion of this thesis.

### Context

The central goal of the work presented in this thesis is to enable the development and the integration with software tools of high quality application specific arithmetic hardware operators. Here, hardware refers to implementation as digital circuits. This work focuses on digital circuits at the logic level. At this abstraction level, digital circuits consist in collections of logic signals combined to produce something useful. How exactly these signals are combined, and how to produce these combinations is detailed in section 1.4. The "something useful" that results from this combination depends on the application. In the case of this work, it consists in computing the result of some computation. This requires to have some way to interpret the logic signals of a digital circuit as a numerical value. This is the aim of numerical formats, which are presented in section 1.2. Having a representation for numbers allows to perform computation on them. This is the purpose of hardware arithmetic operators, presented in section 1.3. Finally, in the context of this thesis, hardware operators are implemented on Field-Programmable Gate Arrays (FPGAs), the architecture and programming model of which are presented in section 1.4. Before delving into these details, section 1.1 briefly presents the core concepts of logic signal and logic vector, and introduces the notations that are used in the rest of this work.

### **1.1** Logic signals, logic vectors

At the logic level, a logic signal is the core element that digital circuits handle. A logic signal is at anytime in one of two states, called either high and low, true or false, set and unset, or '1' and '0'. In this work, logic signals are modeled as variables from  $\mathbb{B} = \{0, 1\}$  and are named with lowercase letters.

It is sometime convenient to reason on a whole group of signal as one en-

tity. These signals can be concatenated to form logic vectors. In this work, logic vector names start with a capital letter.

Vector component access is denoted using squared bracket notation. For instance, V[2] is the third component of the vector V. The width of a logic vector is its number of elements, and is expressed in bits.

In this work, vectors will often be represented as bit string. With this representation, the vector first element is the rightmost one. That is, if V = 01, then V[0] = 1 and V[1] = 0.

### **1.2 Numerical formats**

Performing computation with digital circuits involves to manipulate numbers with them. As these circuits only manipulates logic vectors, it is necessary to be able to use them to represent numbers. This is the role of numerical formats, which define decoding schemes to interpret a logic vector, the *representation* as a *value*. Table 1.1 gives an example of an arbitrary numerical format for 2-bits vectors. A value is associated to each representation.

| Representation | Associated value |

|----------------|------------------|

| 00             | $-\frac{2}{3}$   |

| 01             | 2                |

| 10             | -8               |

| 11             | 12               |

|                |                  |

Table 1.1: Example of an arbitrary numerical format on 2-bits vectors.

All encoded values of table 1.1 example are real numbers. This is the canonical case, but some formats might also encode non-real special values, such as infinities.

Formally, a format  $\mathcal{F}$  is defined by

- its representation width  $n_{\mathcal{F}}$  (the size of its representations) (2 in case of the example of table 1.1),

- its (possibly empty) special value set S<sub>F</sub>. This is the set that contains the nonreal values that should be representable by the format such as infinities. The format domain is then

$$\mathbb{D}_{\mathcal{F}} = \mathbb{R} \cup \mathbb{S}_{\mathcal{F}}$$

This set is empty in the example.

• Its decoding function  $d_{\mathcal{F}} : \mathbb{B}^{n_{\mathcal{F}}} \to \mathbb{D}_{\mathcal{F}}$  that maps a representation to the represented value. In the case of the example, it corresponds to reading the value associated to the representation from the table.

6

• The set of representable domain values  $\mathbb{F}_{\mathcal{F}}$  (the image of the representation domain through the application of the decoding function). This corresponds to the set of values appearing in the second column of table 1.1.

Due to the finite number of representations,  $\mathcal{F}$  cannot represent exactly all real values. Rounding functions are used to map a representable value to any real value. Two basic directed rounding functions can be defined:

• Round towards  $+\infty$  (or rounding up):

$$\begin{split} o_{\mathcal{F}}^{\uparrow} : \mathbb{D}_{\mathcal{F}} \to \mathbb{F}_{\mathcal{F}} \\ v \mapsto \begin{cases} \min i \in \mathbb{F}_{\mathcal{F}} \mid i \geq v, & \text{if } v \in \mathbb{R} \\ v & \text{otherwise} \end{cases} \end{split}$$

• Round towards  $-\infty$  (or rounding down):

$$\begin{split} o_{\mathcal{F}}^{\downarrow} : & \mathbb{D}_{\mathcal{F}} \to \mathbb{F}_{\mathcal{F}} \\ & \nu \mapsto \begin{cases} \max i \in \mathbb{F}_{\mathcal{F}} \mid i \leq \nu, & \text{if } \nu \in \mathbb{R} \\ \nu & \text{otherwise} \end{cases} \end{split}$$

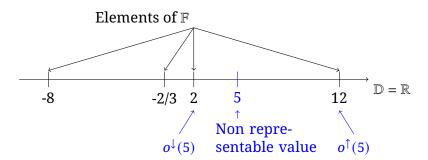

Figure 1.1 shows the representable elements of the format defined by table 1.1, and illustrates the value returned by the two directed rounding function on this format.

The  $\mathcal{F}$ -representable neighborhood of a real value v is defined as:

$$\operatorname{rnb}_{\mathcal{F}}(v) = \left\{ o_{\mathcal{F}}^{\downarrow}(v), o_{\mathcal{F}}^{\uparrow}(v) \right\}$$

When *v* has a representation in  $\mathcal{F}$ , this set only contains *v*. As figure 1.1 shows, for the example format, rnb(5) = {2, 12}.

This neighborhood is used to define two rounding modes that this work focus on. Rounding to nearest, as its name suggests returns the element of the neighborhood with the smallest distance to the exact value.

$$o_{\mathcal{F}}^{\mathrm{N}}(v) = \underset{x \in \mathrm{rnb}_{\mathcal{F}}(v)}{\operatorname{argmin}} |x - v|$$

In case of the illustration example,  $o^{N}(5) = 2$  as the distance from 5 to 2 is smaller than the distance from 5 to 12.

A tie-breaking rule determines which of the neighbor should be returned when the real value is a midpoint, i.e. when the value is equidistant to the two neighbors.

The second rounding mode is faithful rounding. It only requires that one of the neighbors is returned.

Numerical formats with arbitrary mapping such as the example of table are difficult to reason with and to use when the representation size grows. For larger formats, it is thus desirable to get some hardware-exploitable regularity in the representation-value mapping. Commonly used regular formats are fixed-point and floating-point. These specific formats are detailed in the following sections.

### 1.2.1 Fixed-point

#### **Unsigned fixed-point formats**

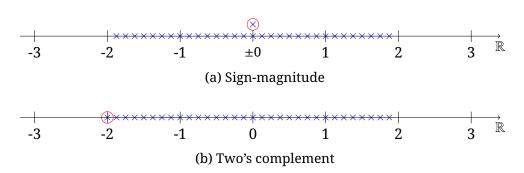

Unsigned fixed-point formats values are represented using binary positional notation. Binary positional notation is very similar to the usual decimal notation: the only difference is the radix. A number written in this system is expressed as a sum of powers of two. The fractional point in this system is used to determine which power of to corresponds to which bit. The bit immediately on its left is associated to  $2^0$  and the associated weight doubles each step leftward. Reciprocally, it is halved each step rightward. A bit's position p is its distance with the  $2^0$  weighted bit, with a positive increase in the left direction. The weight associated to such a bit is simply  $2^p$ .

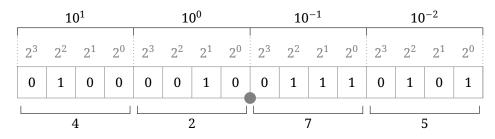

Figure 1.2: Binary positional notation of 42.75

Figure 1.2 illustrates this notation. The position of the bit is reported on

the axis below the representation, and their weight is written above them. For instance, the greyed bit is at position -1 and its weight is  $2^{-1}$ . All non-written bits are implicit zeros, so for instance bits with position above 6 are all zeros. The represented value is the weighted sum of its bits so here

$$v = 2^5 + 2^3 + 2^1 + 2^{-1} + 2^{-2} = 42.75$$

The value v of a number written in binary positional notation with bits  $b_i$  at position i is

$$v = \sum_{i=-\infty}^{+\infty} b_i \cdot 2^i$$

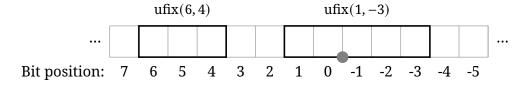

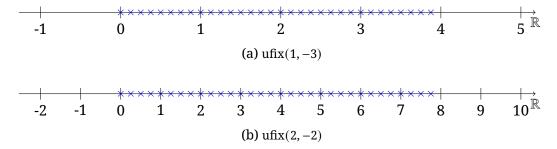

However, having an infinity of representation bits is not physically possible. Practical unsigned fixed-point numeric formats are defined by their high and low bit positions, respectively m and l, such that  $m \ge l$ . Such a format is denoted ufix(m, l), and has a representation width of  $n_{ufix}(m, l) = m - l + 1$ . Its representation is a "chunk" of the infinite positional notation, which is illustrated by figure 1.3. The decoding function is hence a restriction on the available representation bits of the previous equation, and the value v is obtained with

$$v = \sum_{i=l}^{m} 2^{i} R[i-l]$$

The weight of the rightmost bit of the representation is called the unit in the last place (ulp) of the format. This is the smallest difference that exists between two distinct representable values. Formats of the type ufix(m, 0) form a notable group : they allow to represent all positive integers up to  $2^{m+1} - 1$ . By extension, a value v from ufix(m, l) can be thought as a scaled integer

$$v = i \cdot 2^l$$

with *i* an integer representable on ufix(m - l, 0). The plots of representable values of two 5-bits fixed-point formats of Figure 1.4 illustrates this. The rep-

resentable value set of one format is a scaled version of the second format representable value set.

Figure 1.4: Visualization of representable values for two 5-bits unsigned fixed-point formats.

Alternative equivalent parametrizations exist for fixed-point formats. One frequently used parametrization, the *Qi.f* notation, describes these formats with two integers *i* and *f* which are respectively the number of integer and fraction bits. For instance ufix(4, -2) would be denoted *Q*5.2. While this notation is good when the decimal point is included in the described formats, it becomes quite unintuitive when it is not. For instance, the format ufix(-3, -7) is named Q - 2, 5 in this formalism, the -2 integer bits conveying the fact that in addition to not having integer bits, the format also "lacks" the two leftmost fractional bits. For this reason, this work uses the ufix(*m*, *l*) notation.

Next section present extensions to this system that allow handling negative values.

#### Signed fixed-point formats

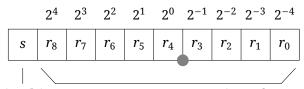

Two main systems coexist to add support of negative values to fixed-point formats. These two systems have the same parameters m and l as unsigned fixed-point. In these two systems, the leftmost bit is the sign bit s. The remaining low bits consist in a representation in ufix(m - 1, l). In the following,  $R_L$  denotes these bits and  $v_L$  the value that they represent. The decomposition of a signed fixed-point value is detailed on figure 1.5.

Sign bit  $r_L$ , ufix(4, -4) representation of  $v_L$

Figure 1.5: Decomposition of a signed fixed-point format with m = 5 and l = -4

The two systems differs in how the sign bit is interpreted in the decoding function. In the most natural one, the sign-magnitude encoding, it is used to determined if the encoded value is  $v_L$  (when the sign bit is '0') or its opposite  $-v_L$  (when the sign bit is '1'). Formally, the represented value  $v_{sm}$  is given by the relation

$$v_{\rm sm} = (-1)^s \cdot v_L$$

It is straightforward to see that the opposite of each representable value is also a representable value.

While it is quite intuitive, this encoding system has two main disadvantages. First, the algorithm to get the representation of the successor is quite complicated, as it depends on the sign bit. Indeed, in the general case (when both the value and its successor have the same sign),  $r_L$  should be replaced by the representation of its successor when *s* is unset, and by the representation of its predecessor when *s* is set. And a few additional corner cases have to be handled. One of them is directly related to the second disadvantage, which is that these formats have two signed representations for 0.

The second system, two's complement, keeps the weighted-sum principle of unsigned fixed-point format. It only differs with this format by the weight of the leftmost (sign) bit, which is  $-2^m$  instead of  $2^m$ . The represented value  $v_{2c}$  is then

$$v_{2c} = -2^m + v_l$$

With two's complement, the successor computation is greatly simplified and there is no redundant representation for one given value. Due to that and to the fact zero is still representable in the format, opposite of representable values is not always representable itself. This asymmetry is visible on Figure 1.6b which shows the representable value for a two's complement signed fixed-point format defined with m = 1 and l = -3. Value -2 is representable, while 2 is not. By contrast, representable values of sign-magnitude fixed-point with same parameters (represented on figure 1.6a) cannot represent -2 either and replace this by a second representation for 0. In the following, sfix(m, l)will denote 2's complement fixed-point format of parameters m and l.

Similarly to the unsigned case, sfix(m, 0) defines a notable group of formats able to represent all integers *i* such that

$$-2^m \le i < 2^m$$

Figure 1.6: Visualization of representable for the two signed fixed-point schemes with m = 1 and l = -3. Scheme-specific representable values are circled in red.

Values v of sfix(m, l) can also be seen as scaled integer:

$$v = i \cdot 2^l$$

with *i* representable on sfix(m - l, 0).

#### **Biased fixed-point formats**

It is possible to add an "implicit" constant offset (i.e. independent of the representation) to the summation performed to decode a fixed-point representation. This shifts the representable values by the added amount. One example of such biased fixed-point representations is the Half-Unit Biased (HUB) encoding families [1]. A HUB representation is defined similarly to fixed-point formats by its high and low bit positions m and l. The Unit in the format name refers to the scaled integer vision of the fixed-point the represented number: HUB decoding function adds a constant offset of half of a scaled unit in the decoding process. The bias value is then  $2^{l-1}$ .

It has the advantage that rounding a value to the nearest HUB representation only consists in truncated all bits of position lower than *l*.

Another application of biased fixed-point is presented along IEEE-754 encoding scheme.

#### Arbitrary radix fixed-point

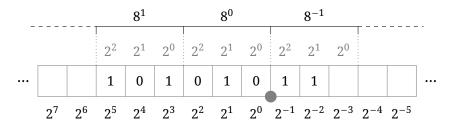

Using binary positional notation on digital circuits that manipulate binary signal seems natural. It is however possible to represent number using different radixes.

Radix  $\beta$  notation decomposes a value v as a sum of weighted  $\beta$ -digits, each

weight being a power of  $\beta$  depending on the position *i* of the  $\beta$ -digit  $k_i$ .

$$v = \sum_i k_i \beta^i$$

Similarly to binary fixed-point, the representation in  $\beta$  radix fixed-point stores a sequence of  $\beta$ -digits. As the circuit can only handle logic signal, these  $\beta$ -digits are themselves encoded in binary.

When  $\beta = 2^p$ , the representation does not differ from radix 2 representation, only the interpreted meaning of representation bits differs. Indeed, in this case the contribution of each  $\beta$ -digit can be seen as an integer scaled by a power of two, and none of these contributions overlap. Figure 1.7 illustrates this by showing two possible interpretation of the binary-coded representation of 42.75.

Figure 1.7: Binary and binary-coded octal positional notation of 42.75

When  $\beta$  is not a power of two, the binary encoding of the  $\beta$ -digit is wasteful. Indeed,  $w = \lceil \log_2(\beta) \rceil$  bits are required to store one  $\beta$ -digit, but only  $\beta$  out of the 2<sup>w</sup> possible combination of those bits are effectively used. This is illustrated with figure 1.8 that gives the binary-coded radix-10 representation of the value 42.75. This representation requires 15 bits, where the binary representation only requires 8 bits.

Figure 1.8: Binary-coded decimal positional notation of 42.75

So in one case the representation does not change, and in the other the representation is wasteful, so why using such a system ? If l = 0, there is definitely no interest to use a radix that is not a power of two, as integers are

all representable using radix 2. With l < 0 however, the set of exactly representable values changes. For instance 49.3 is not exactly representable in binary, but is representable in radix 10. So financial application for instance might be interested not to have representation rounding errors when they perform computation over amount of money which are expressed in decimal notation.

One way to limit the waste of representation bits is to use a radix that is very near to the power of two immediately superior to it. For instance, it might be more interesting to use radix 1000 (10<sup>3</sup>) than radix 10[2]. Indeed, with radix 1000, 1000 out of the 1024 possible combination of the 10 bits required to store a 1000-digit effectively used. In the other hand, only 10 out of the 16 possible combination of the 4 bits required to store a radix-10 digit are used.

### **1.2.2 Floating point**

Fixed-point formats lack dynamics: representing both high magnitude and very small numbers is not possible without using very wide (and impractical) formats. Floating-point formats solve this issue by using a representation similar to the so-called scientific notation. A value v is represented as a significand M scaled by some power E of a given radix  $\beta$ .

$$v = M \cdot \beta^E$$

The discussion about radix value is analog to the fixed-point case. In the present work, only binary ( $\beta = 2$ ) floating-point formats are considered.

A basic floating-point encoding could be defined by a pair of signed fixedpoint formats ( $\mathcal{F}_E, \mathcal{F}_M$ ), respectively the exponent and significand format. The representation is the concatenation of a representation  $r_E$  and  $r_M$  from each of the formats. The represented value v is obtained from the two fixed-point values:

$$v = d_{\mathcal{F}_M}(r_6) \cdot 2^{d_{\mathcal{F}_E}(r_E)}$$

The representation width of  $\mathcal{F}_M$  specifies with how many "significant digits" the format can represent a number. This is called the precision of the floating-point format. In the other hand, the representation width of  $\mathcal{F}_E$  is related to the dynamic range of the format. For two floating-point formats with identical precision, the one with higher dynamic range will be able to represent higher and lower magnitude values.

Figure 1.9 gives a possible representation for the value 42.75 in such a

14

Figure 1.9: Basic floating-point representation of 42.75 as  $0.333984375 \times 2^7$

format. However, this format has redundancy. Indeed, if the significand representation does not start and end with a 1, it is possible to shift it and reduce or increase the exponent to keep the same value. For instance, 42.75 can also be represented as 010000010101011 in the format from figure 1.9. Most of the time this redundancy is undesirable, as it is "wasting" codes that could be used to represent other values. Following sections describes well-defined floating-point encoding schemes that avoid this waste.

### **IEEE-754 encoding scheme**

Compared to fixed-point where possibility of variation is quite limited, floating-point offers a lot of freedom in their conception. In the early days of computing, this lead to each CPU manufacturer having its own specific format. This is reflected in the first version of ANSI C (C89) standard. In this version the definition of floating-point types in C is very scarce. It is only specified that C has three floating point type (float, double and long double), verifying the property

$\mathbb{F}_{\texttt{float}} \subseteq \mathbb{F}_{\texttt{double}} \subseteq \mathbb{F}_{\texttt{long double}}$

Outside from this, "the representations of floating-point types are unspecified". In addition to have different representation, the semantic of operations was also not consistent between floating-point implementations. As a result, standard compliant code could produce completely different outputs when executed on different machines.

IEEE-754 [3] is the standard that resulted from the industry effort to eliminate this heterogeneity. Its first edition was issued in 1985 and defines two fully specified binary floating-point formats (which C99 later adopted as representation for the C float and double types), and the 'extended" format family. It also defines the base operations that should be provided by compliant implementations. The 2008 revision introduced the concept of interchange formats, that are intended solely for the purpose of sharing a value, but not for performing computation. It also specified three decimal floating-point formats. An IEEE-754 binary format representation is composed of three fields:

- The sign bit *s* on 1 bit,

- the biased exponent *E* on *w<sub>E</sub>* bits,

- the fraction part *F* on *w<sub>F</sub>* bits.

| Format    |       |       |

|-----------|-------|-------|

| Format    | $w_E$ | $W_F$ |

| binary16  | 5     | 10    |

| binary32  | 8     | 23    |

| binary64  | 11    | 52    |

| binary128 | 15    | 112   |

| binary256 | 19    | 236   |

Table 1.2: Field widths for IEEE-754 standard formats.

Field sizes for fully specified formats are given on table 1.2. The special value set of IEEE-754 binary encoding schemes contains four values. The first two, positive and negative infinities are the overflow markers. These are the values that are returned when an operation has a result which is bigger (resp. smaller) than the biggest (resp. smallest) representable values. The third and fourth ones are quiet and signalling Not-a-Number (NaN). They arise as a result of invalid operation, such as taking the logarithm of a negative number. The difference between signaling and quiet NaNs concerns the environment surrounding the computation, so for the rest of this work they will be considered as a unique value.

The special values are all encoded with all the exponent field bits set to one. When the fraction bits are set to zero, the represented value is infinity (with signedness depending on the sign bit). For instance, in binary16 the representation for  $-\infty$  is 111110000000000. As soon as one bit of the fraction field differs from zero, the represented value is NaN. Since the 2008 standard revision, the leftmost bit of NaN representation indicates whether it is a quiet NaN. In binary16, quiet NaN are then represented as s111111xxxxxxxx The remaining bits (marked with x in the previous example) are called the NaN payload and can be used to store application-defined data. This usage is simplified with the new operations setpayload and getPayload introduced in the 2019 standard revision.

When at least one bit of *E* is set to 0, the represented value is a numerical value. The decoding process is very similar to what has been introduced in the previous section. A first difference is that it is using sign-magnitude encoding. The second important difference is that the fraction is normalized in order to avoid redundant value representations. That is, an implicit bit *i* at position 0

is prepended to the fraction, the complete explicit significand is  $S_e = i.F$ . In the general case, the value of *i* is 1.

Finally, the third main difference is that a biased exponent is stored in the representation. For a binary format of exponent width  $w_E$ , the bias value is

$$b = 2^{w_E - 1} - 1$$

The actual exponent is E - b. Having a biased exponent ensure that the representation ordering is the same as if they were interpreted as sign-magnitude representation of integers. Indeed, the biased exponent is an unsigned integer to which is concatenated the fraction that is also an unsigned integer. For the same exponent, the representation with the biggest fraction represent the biggest value, and when the exponent differs, the representation with the biggest exponent encodes the biggest value. When the sign differs only the sign is relevant.

This property allows efficient comparison of IEEE-754 values by using integer comparison on the representation. This also helps to compute rounding, as a rounding neighborhood is constituted by values having successive representations.

The represented value is then

$$v = (-1)^s \cdot 1.F \cdot 2^{E-b}$$

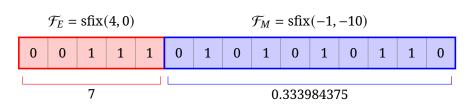

Figure 1.10: Unique IEEE-754 binary16 representation of 42.75.

Figure 1.10 gives the encoding in binary16 of the value 42.75. The value stored in the exponent is 20. As the exponent field has a width of 5, the bias value is 15, so the unbiased exponent is 5. Stored fraction is 0101011000, so the significand is 1.0101011000 (1.3359375 in decimal). The represented value is then  $1.3359375 \cdot 2^5 = 42.75$ .

Having always the implicit bit set to one does not allow representing 0. This is solved by adding a special case for numeric values called the subnormal range of the format. When all bits of *E* are set to 0, the implicit bit becomes 0. To avoid a gap between subnormal and normalized values, the exponent that corresponds to subnormal significand is the same as the minimal normal exponent. So the real value decoding process involves computing the actual

significand

M = i.F

and the unbiased exponent

$$E_u = E - b + (1 - i)$$

with

$$i = \begin{cases} 0 & \text{if } E = 0\\ 1 & \text{otherwise} \end{cases}$$

to get the encoded value

$$\nu = (-1)^s \cdot 2^{E_u} \cdot M$$

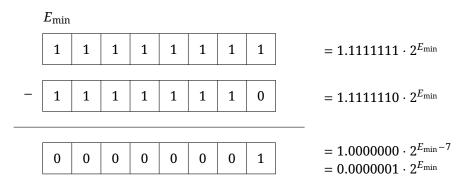

In addition to allowing the representation of zero, the subnormal mechanism also brings interesting properties to the format. One of which is the following equivalence:

**Property 1** *Given f an IEEE-754 binary numerical format, and o a valid IEEE-754 rounding mode*

$$\forall (x, y) \in \mathbb{F}_f^2, \ o(x - y) = 0 \Leftrightarrow x = y$$

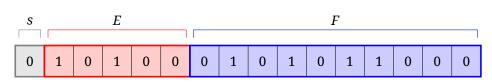

Property 1 means that the difference between two representable values cannot round to zero unless the two values are equal. This property can be exploited to optimize code (for instance replacing left member of equivalence by right member, which replaces computing one subtraction and one comparison by only one comparison). Figure 1.11 gives an illustration of why subnormal mechanism is required to get this property to work. Difference between two very near number that have exponent near to the minimal exponent can result in a value that is smaller than  $2^{E_{min}}$ , with  $E_{min}$  the minimal normal exponent. Without subnormal mechanism, these values are not exactly representable, so depending on the rounding mode, the result could be zero even if the two values are not equal.

Table 1.3 summarizes the different decoding ranges for IEEE-754 binary16 format.

#### Operations

The IEEE-754 standard defines five rounding modes for elementary operations. The directed rounding modes towards  $+\infty$  and  $-\infty$  corresponds to the

|             | Repres                  | entation                     | Value                    | Denomination                   |

|-------------|-------------------------|------------------------------|--------------------------|--------------------------------|

| 1<br>1<br>1 | 11111<br>11111<br>11111 | 111111111<br><br>1000000000  | Quiet NaN                |                                |

| 1<br>1<br>1 | 11111<br>11111<br>11111 | 011111111<br><br>0000000001  | Signaling NaN            | Special values                 |

| 1           | 11111                   | 0000000000                   | $-\infty$                |                                |

| 1<br>1<br>1 | 11110<br><br>00001      | 111111111<br><br>0000000000  | $-1.F \cdot 2^{E-b}$     | Negative<br>normal range       |

| 1<br>1<br>1 | 00000<br>00000<br>00000 | 111111111<br><br>0000000001  | $-0.F\cdot 2^{E_{\min}}$ | Negative<br>subnormal          |

| 1           | 00000                   | 0000000000                   | -0                       | range                          |

| 0           | 00000                   | 0000000000                   | +0                       |                                |

| 0<br>0<br>0 | 00000<br>00000<br>00000 | 0000000001<br><br>1111111111 | $0.F\cdot2^{E_{\min}}$   | Positive<br>subnormal<br>range |

| 0<br>0<br>0 | 00001<br><br>11110      | 0000000000<br><br>1111111111 | $1.F \cdot 2^{E-b}$      | Positive<br>normal range       |

| 0           | 11111                   | 0000000000                   | +∞                       |                                |

| 0<br>0<br>0 | 11111<br>11111<br>11111 | 0000000001<br><br>011111111  | Signaling NaN            | Special values                 |

| 0<br>0<br>0 | 11111<br>11111<br>11111 | 100000000<br><br>1111111111  | Quiet NaN                |                                |

Table 1.3: Interpretation of IEEE-754 binary16 encoding.

Figure 1.11: Subtraction of two floating-point values of minimal normal exponent  $E_{min}$ .

one defined in section 1.3, with the notable exception that values above the maximal representable numerical value are rounded to  $+\infty$  (resp.  $-\infty$ ). A third rounding mode, towards 0, is defined as follows:

$$o_f^0(v) = \begin{cases} o_f^{\uparrow}(v) & \text{if } v < 0\\ o_f^{\downarrow}(v) & \text{otherwise} \end{cases}$$

Round-to-nearest is also supported with two tie-breaking rules:

- Ties-to-even rule specifies that the neighbor with representation ending with a 0 bit should be returned. This allows an unbiased rounding error, as there are as many midpoints above their "nearest even" than midpoints below.

- Ties-to-away returns the neighbor with higher magnitude. This rule has "polarized" rounding error: negative midpoints are always rounded to lower values, where positive midpoint are always rounded to higher values. It is however a bit less expensive to compute, as only one extra bit after the last fraction bit of the result has to be known. In comparison, computing correct ties-to-even also requires knowing if the value is exactly a midpoint or not.

Compared to the fixed-point case, the distance between two successive representable values is not constant. Reasoning in terms of absolute error with floating-point is then quite complicated, so it makes more sense to use relative error. For a real value v, and a rounding function o, the relative error is

$$\epsilon = \frac{o(v) - v}{|v|}$$

Inside a *binade*, the set of all representable normal values that share the same exponent, the distance between successive values is constant. For round-to-nearest, the biggest absolute error is obtained for midpoints. On a binade of exponent E in the normalized range, distance between representable values and midpoints is

$$\delta_N = 2^{w_F - 1} \cdot 2^E$$

The minimal representable value inside the binade is  $m = 2^{E}$ . The relative error committed on the binade is then bounded by

$$\begin{aligned} |\epsilon_{\max}| &= \frac{m + \delta_N - m}{m + \delta_N} \\ &= \frac{2^{E - w_F - 1)}}{2^E + 2^{E - (w_F + 1)}} \\ &< \frac{2^{E - (w_F + 1)}}{2^E} = 2^{-w_F - 1} \end{aligned}$$

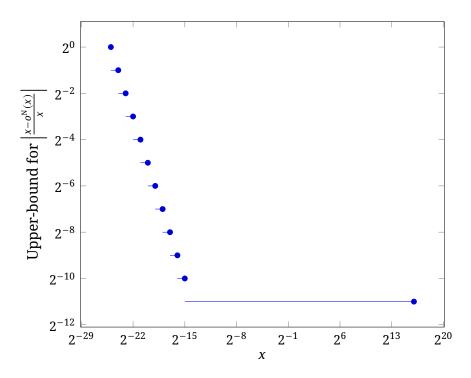

This maximal relative error does not depend on the binade. For directed rounding, the maximum absolute error inside a binade is twice the maximum absolute error of round-to-nearest, so the bound on relative error is also doubled. The same reasoning applies to each subnormal binade, but considering the effective fraction width of the binade (which takes into account the leading zero bits in the denormalized fraction). Figure 1.12 shows the relative error bound per binade when rounding to nearest IEEE-754 binary16 representation. The relative error is important for very small values (reaching 1 for values that are rounded to zero), and decreases until the normal range is reached, on which the error relative error bound is binade-independent.

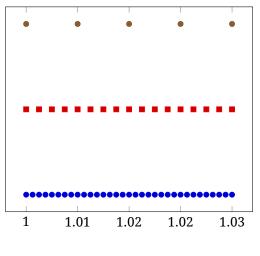

IEEE-754 binary32 and binary64 fulfill the role of the all-purpose numeric formats that are used when dealing with non-integral values of unknown scales. Even the high number of redundant representation for NaN has found usage, such as compact type information and value packing in dynamically typed language interpreter, with the technique known as NaN-boxing [4]. However, this redundancy is more annoying with narrower formats, where having more representable values would be preferable. Machine-learning is an example of application class that does not need an important precision but still requires values with an important dynamic range. Multiple encoding scheme have been developed recently to meet the requirement of efficient narrow floating-point representation.

DLFloat[5] is such a format. Its 16-bits representations regular decoding process is those of an IEEE-754 format with  $w_F = 9$  and  $w_E = 6$ . To reduce the overhead of special values, NaN and infinities are fused so the special value set of DLFloat only contains one element, NaN-or-Infinity. This element has

Figure 1.12: Bound on relative-error magnitude for IEEE-754 binary16 representable range.