# Location of Oxide Breakdown Events under Off-state TDDB in 28nm N-MOSFETs dedicated to RF applications

Tidjani Garba-Seybou, Xavier Federspiel, Frederic Monsieur, Mathieu Sicre, Florian Cacho, Joycelyn Hai, Alain Bravaix

#### ▶ To cite this version:

Tidjani Garba-Seybou, Xavier Federspiel, Frederic Monsieur, Mathieu Sicre, Florian Cacho, et al.. Location of Oxide Breakdown Events under Off-state TDDB in 28nm N-MOSFETs dedicated to RF applications. 2023 IEEE International Reliability Physics Symposium (IRPS 2023), Mar 2023, Monterey, CA, United States. 10.1109/IRPS48203.2023.10117725 . hal-04604661

### HAL Id: hal-04604661 https://hal.science/hal-04604661v1

Submitted on 7 Jun 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Location of Oxide Breakdown Events under Off-state TDDB in 28nm N-MOSFETs dedicated to RF applications

Tidjani Garba-Seybou<sup>1,2</sup>, Xavier Federspiel<sup>1</sup>, Frederic Monsieur<sup>1</sup>, Mathieu Sicre<sup>1</sup>, Florian Cacho<sup>1</sup>, Joycelyn Hai<sup>1</sup>, (1) STMicroelectronics, 850 Rue Jean Monnet, 38920 Crolles, France,

Phone: +33438927148; E-mail: mahamadoutidjani.garbaseybou@st.com

Alain Bravaix<sup>2</sup>,

(2) ISEN Méditerranée, REER-IM2NP UMR CNRS 7334, Maison des technologies, Place G. Pompidou, 83000 Toulon, France

Abstract—A detailed analysis of Off-state gate-oxide breakdown (BD) mode and its location under non-uniform electric field is performed in 28nm FDSOI N-MOSFET devices. We show that hard breakdown (HBD) occurs exclusively from the middle of the channel to the drain overlap extension for Off-state TDDB. HBD is characterized under DC stress with different gate-length  $L_{\rm G}$  as a function of drain voltage  $V_{\rm DS}$  and temperature. We check that the leakage current is the better monitor for TDDB dependence precursor to HBD under Off-mode stress by using the proper modeling and discussing the different possible origin of the higher form factor  $\beta$  value under Off mode stressing.

Index Terms--CMOS, charge trapping, hard breakdown, interface traps, Off-state damage, soft breakdown.

#### I. INTRODUCTION

TDDB remains a key reliability concern in ultra-short channel CMOS nodes with the guaranty of speed performance and low consumption requirements. Even if Off-state stress generally degrades device at a smaller rate than On-state stress, it can become a limiting factor with HBD under RF operation in the millimeter wave domain (5G) [1-3], where supply voltage V<sub>DD</sub> may be usually doubled with respect to the one used for logic application. Thus, device parameter drifts might become significant in correlation to soft breakdown that may trigger hard breakdown into the gate-drain region once a critical density of localized defects is generated. Many papers discuss from lateral profiling of interface damage during Offstate stress that the peak degradation occurs outside of the gate-edge. Breakdown spot is then estimated to occur in the spacer region, collocated with peak interface damage [4-5]. Although a reasonable consensus has been reached on Offstate breakdown mechanism, drain and gate leakage currents after BD were found to coincide, confirming that percolation path in dielectric stack was created at drain edge [6-8].

Recently Off-state hot-carrier degradation (HCD) has been associated to broken  $\equiv$ Si $\rightarrow$ O bonds at the interface [4] with a bond dispersion model showing higher time exponent (n=0.7 – 0.8), extending the findings to a universal modeling to Onstate degradation [5]. Classical HCD On-state has been historically associated with broken  $\equiv$ Si $\rightarrow$ H bonds at Si/SiO<sub>2</sub> interface. However, recent reports deal with interaction

between On and Off modes [9-11] and show that gate-oxide degradation can indeed occur during HCD On-state [12-13]. The  $V_{GS}$  dependence between Off-mode and  $V_{Gmax}$  was studied revealing HC injection efficiency that enables new sensitive criteria to prevent from HBD events. Degradation in short-channel transistors can occur in Off mode and under subthreshold conditions due to impact-ionization (II) and non-conducting HC where this latter is related to different leakage current components as surface band-to-band tunneling (BTBT) and gate-induced drain leakage (GIDL).

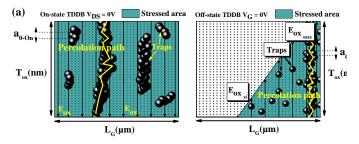

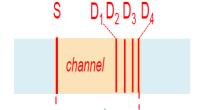

Usually, BD under Off mode is modeled by TDDB in accumulation in the overlap region due to creation of excessive damage to oxide integrity. This is indeed a relevant failure mode that enables to stress device symmetrically using both source and drain overlap or using voltage splitting technique [14-15]. However, in this paper the competing Offstate TDDB is induced by HC mainly for ultra-short channel transistors, depending highly on channel-length L<sub>G</sub> and I<sub>DS</sub> current. This becomes subsequently challenging for middleof-the-line (MOL) dielectrics reliability. Not only poly to contact BD can reduce the intrinsic reliability margin, but it can also be the origin of extrinsic failures due to slight control of poly to contact space. Therefore, it's important to build accurate model to optimize design rules of high voltage applications at which spacer dielectrics are submitted. A dedicated Off-state HBD model and location analysis is presented for first time. It is critical to determine the sensitivity to Off-state TDDB and deeply understand the wear out mechanisms at device level, as the dielectric HBD strongly depends on spot position that we determined along the channel-length direction. Figs.1a,b summarize the observation about BD path location from On and Off modes analyzed from literature and our previous experiments [6]. Therefore, several BD scenarios have been considered to occur inside oxide (at center or edge), between drain and bulk junction or finally in the spacer region between gate and drain.

After the description of experimental setup and devices used in this work in Section II, we present a dedicated gate-oxide breakdown study under Off-state TDDB in Section III, in comparison to On-state and MOL BD. Then, we propose in Section IV a TDDB modelling under Off mode stressing based on measurement of the initial leakage currents.

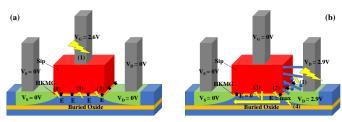

**Figure 1.** Schematic device representations under TDDB stress without serial protection resistances showing main location of breakdown regions. Gate and drain contacts failure are due to significant power dissipation. (a) On-state BD occurs simultaneously in gate contact (1) and different regions of gate-dielectric (2- nearby drain, 3- in channel or 4- nearby source). (b) Under Off-state, BD occurs simultaneously in drain contact (1), in dielectric (2- drain side or 3- middle of channel) or between drain and BOX insulator due to high impact-ionization.

#### II. EXPERIMENTAL DESCRIPTION

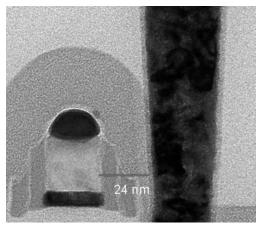

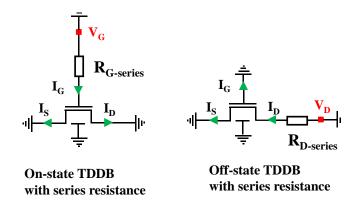

TDDB is evaluated in 28nm FDSOI N-FET devices fabricated with HKMG (EOT = 1.5nm) and different gate channel length L<sub>G</sub> (30nm, 34nm, 40nm, 46nm) issued from STMicroelectronics CMOS SOI technologies. Samples are submitted to Constant Voltage Stress (CVS) applied either on drain-side for Off-state and gate-side for On-state and MOL, between 125°C and 25°C while other terminals were grounded. Poly to contact BD is measured on structures landing on STI Fig.2 rather than CMOS structure for which gate dielectric BD would occur before spacer BD [16]. For the purpose of this paper, TDDB was performed on all devices with  $V_{DS} = 2.9V$  for Off-state,  $V_{GS} = 2.6V$  for On-state, and very high voltage for MOL BD (up to 20V). An  $1k\Omega$  external series resistance was connected to devices in Fig.3 to limit power dissipation in drain/gate contact and to guarantee a stable and reproductible post-breakdown I-V characteristics. The voltage drop over serial protection resistance was corrected for all devices with (1a) and (1b) in order to mimic TDDB stress condition without any external resistance. The experiment methodology consists in the following successive steps: 1) initial current-voltage I-V characterization to obtain fresh device current and eliminate early failures probability (Fig.4), 2) TDDB stress with or without external series resistance as shown respectively in Figs. 5,6 and 3) final post TDDB stress I-V characterization (Figs.7 and 8) for BD path location and resistance estimation. The experimental results will be discussed in Sections III and IV.

Figure 2. Transmission Electron Microscopy (TEM) cross section of poly to contact test structure on STI used for spacer breakdown.

$$V_{DR_{D-series}} = V_D - R_{D-series} \cdot I_D \tag{1a}$$

$$V_{GR_{G-series}} = V_G - R_{G-series} \cdot I_G \tag{1b}$$

**Figure 3.** Measurement set-up of TDDB stress illustration with external protection series resistors. The voltage drop due to resistances has to be compensated with respect to drain (1a), and gate currents (1b).

This paper is organized as follows, first, MOL and dielectric BD mode and location were investigated on more than 700 transistors, using current-ratio technique [17-18] and comparing voltage acceleration factor (VAF). Then, Off-state TDDB dependence is analyzed under DC stress with variation of  $V_{\rm DS},\,L_{\rm G}$  and temperature on several dies and plotted as min and max HBD time values  $(T_{\rm BD}).$  Finally, the dielectric BD is modeled as a function of non-uniform vertical electrical field component  $E_{\rm max}$  and the leakage currents induced by the accelerating stressing drain bias  $(V_{\rm DS}).$

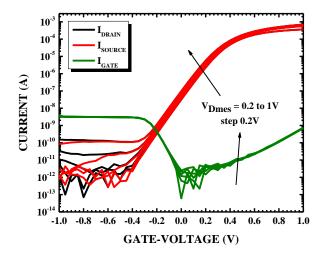

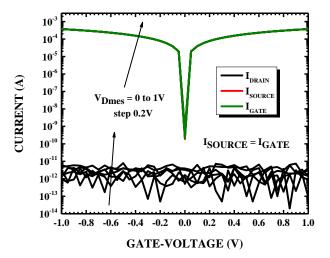

**Figure 4.** Fresh I-V characteristics obtained in three terminals transistor (28nm FDSOI N-FETs with  $W_G = 1 \mu m$  and  $L_G = 30 nm$ ). Drain (black lines) and source (red lines) currents are similar and overlapping before dielectric breakdown. Gate saturating current in Off-mode results from dielectric leakage and mostly from MOS protection diode.

#### III. BREAKDOWN POSITION DETERMINATION

#### A. Device characterization before and after BD

CVS are commonly used to monitor  $T_{BD}$  dependencies and to build up the complete TDDB distribution functions by using different stress voltages and device areas. For this purpose, the recent investigations on Off-state BD mode [6] are further extended to determine the location of HBD under CVS in thin gate-oxide (GO1) FDSOI N-FET with  $L_G$  defined from 30 to 46 nm.

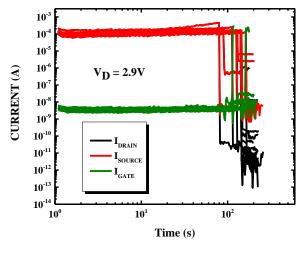

**Figure 5.** Off-state leakage currents until HBD in FDSOI N-FET  $W_G/L_G = 1 \mu m/30 nm$  as function of cumulative stress time in configuration without external series resistance. This generates an open circuit. Source (red lines) and drain (black lines) currents are overlapping.

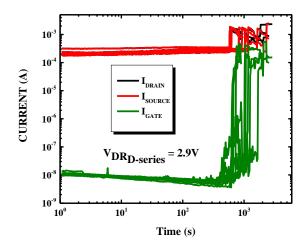

**Figure 6.** Off TDDB leakage currents until BD with connected series protection resistor. Voltage drop has been compensated to reproduce the same stress condition as **Fig.5**. Drain (black lines) and source (red lines) currents are overlapping.

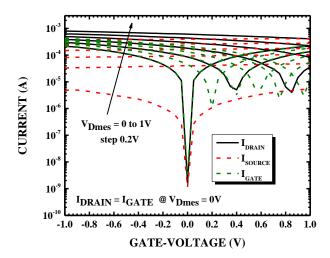

**Fig.4** shows dielectric integrity test by measuring gate, drain and source currents on fresh device without any series resistance in the range  $V_{GS} = -1V$  to 1V and  $V_{DS} = 0.2V$  up to 1V. TDDB without external series resistance causes an open circuit and a dysfunctional device since it exhibits an abrupt downwards jump of currents as observed under Off-state stress on current versus time curves in **Fig.5** on drain and source side. After BD the series resistance was removed, gate, drain and source currents were measured in the range  $V_{GS} = -1V$  to 1V and  $V_{DS} = 0V$  to 1V (**Figs.7-8**). The post-breakdown behavior of an open circuit on drain side is shown in **Fig.7** with very low noisy drain current due to the melting of drain contact. By adding a protection series resistance, the devices remain functional despite dielectric BD (**Figs.6** and **8**).

**Figure 7.** Three terminals transistor I-V characteristics after Off-state TDDB without protection resistor in **Fig.5**. A very low noisy current is measured on drain terminal. Gate (green lines) and source (red lines) currents are overlapping.

Figure 8. I-V characteristics after Off-state TDDB with external series resistance in Fig.6. Devices are still functional after BD.

#### B. Location of breakdown spot

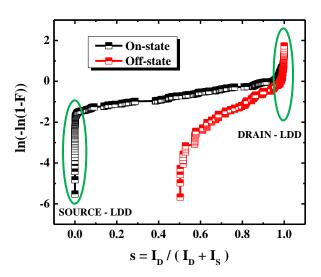

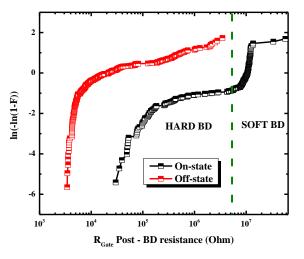

HBD nature quantification methodology consists in the measurement of post-breakdown gate resistance  $R_{Gate}$  for positive gate voltage  $V_G = 1V$  (2). HBD spot position can be precisely obtained with ratio s (3) (Figs.9-10) at negative gate bias  $V_G = -1V$  [17-21]. Under these conditions, electrons are

**Figure 9.** Weibit distribution plots for sorted ratio *s* showing multi-modal behavior of BD in LDD diffusion (vertical) and channel (central) region.

$$R_{Gate} = \frac{V_G}{I_G} \tag{2}$$

$$s = \frac{I_D}{I_D + I_S} = \frac{x_{BD}}{L_G} \tag{3}$$

injected from the gate through the BD path and collected to the source when ratio s is close to 0, otherwise to the drain when ratio s is close to 1. s values obtained in On-mode (black plot in **Fig.9**) which are relating a linear BD spot position in

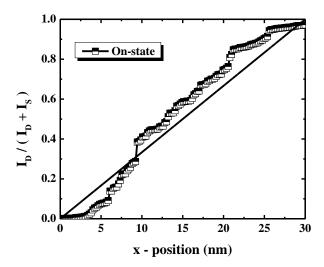

the channel, outside of the lightly doped-drain (LDD) regions, are approximatively equidistant and equiprobable (**Fig.10**).

**Figure 10.** On-state gate-oxide BD spot position sorted according to ratio  $\mathbf{s}$  showing a linear relationship between  $\mathbf{s}$  and BD location distributed equidistantly.

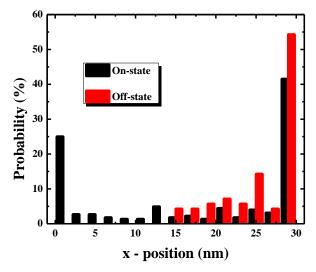

**Figure 11.** BD spot positions classified by regions of BD occurrence in the 30nm gate-length transistor. Higher BD probability is obtained for LDD regions.

Therefore, the current partitioning method can also be applicable to Off-mode BD. **Fig.10** demonstrates the proportional relationship between s ratio and BD spot position  $x_{BD}$ , determined by sorting the s values obtained on a sufficiently large number of tested devices (**Fig.9**). For Onstate TDDB, HBD is observed to occur close to source/drain extension while soft breakdown (SBD) is observed from the channel region (**Figs.11-12**). Under Off-state, only HBD is distinguished in **Figs.11-12** from the middle of the channel until drain extension. The higher breakdown probability observed in LDD regions (**Fig.11**) can be explained by electric

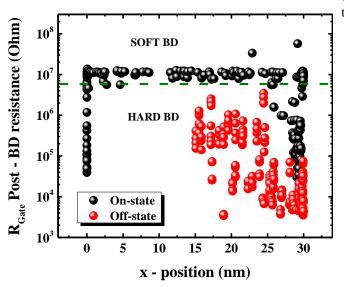

field non uniformity related to charges in spacers (significant on drain side) and channel depolarization due to oxide leakage. The distribution of  $R_{\text{Gate}}$  is plotted in Fig.13 where HBD path resistance is below  $3.5 M\Omega$  and the soft one above this value.

**Figure 12.** Breakdown path resistance plotted as a function of position along the channel. Hard breakdown is exclusively identified for Off-state TDDB.

**Figure 13.** R<sub>GATE</sub> distribution plot for Off-mode and On-mode TDDB showing multi-modal behaviors between hard BD and soft BD.

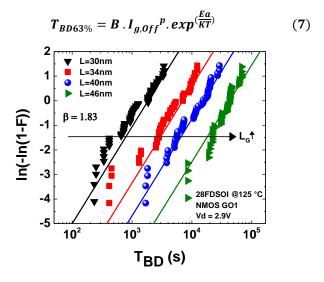

#### C. Breakdown statistics

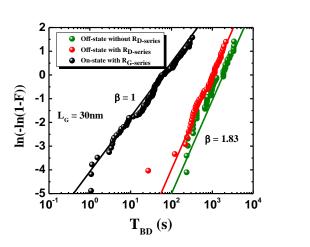

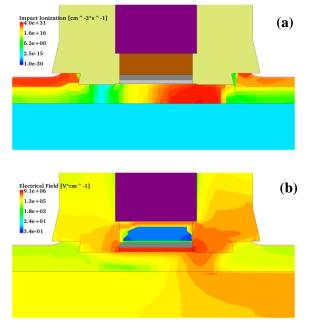

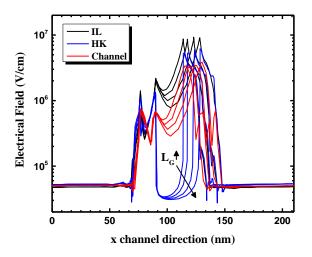

Weibull distributions for TDDB under On and Off modes are plotted in Fig.14 showing no sensitivity to the external series resistance. Processes were simulated thanks to Sentaurus Process tool [22]. The electrical outputs are computed by solving the Poisson equation and current continuity equations coupled with drift-diffusion transport model in Sentaurus Device module [23]. Impact-ionization coefficients are calculated from Chynoweth law [24-25]. Offstate TDDB simulations result in higher impact-ionization generation close to drain (Fig.15.a) induced by a stronger lateral electric field with a peak value at gate to drain edge and

spacer (**Fig.15.b**). TDDB slope value can be related to Si/SiO<sub>2</sub>/HfO<sub>2</sub> gate stack,

$$\beta = \frac{n \cdot (T_{HK} + T_{IL})}{a_0} \tag{4}$$

with n the  $T_{BD}$  time exponent,  $T_{HK}$  is high-K thickness,  $T_{IL}$  is the interface layer thickness with defect cell size as:

$$a_{0-0n} > a_{0-0ff} \tag{5}$$

**Figure 14.** Comparative cumulative distribution plots for GO1  $W_G/L_G = 1 \mu m/30 nm$  28 FDSOI N-FETs with lower Weibull slope obtained for On-state TDDB. External series resistance has no effect on  $\beta$ .

**Figure 15.** TCAD simulations during Off-state TDDB on N-Fet device in logarithmic scale. (a) Impact ionization showing its peak value at drain junction. (b) Electical field profile in channel, Si/SiO<sub>2</sub>/HfO<sub>2</sub>/TiN gate stack and the regions around.

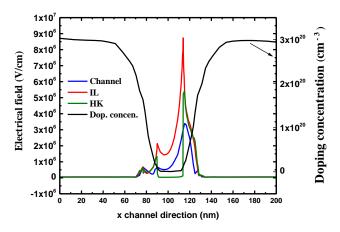

**Figure 16.** Lateral profile of electrical field during Off-state TDDB in channel, interface layer and high-K showing located peak values into gate to drain edge with higher damage generation rate in IL and HK than into the channel

Gate stack is the most sensitive region to failure under Offand On modes with a higher generation rate and electric field into the interface layer (IL) and high-K (HK) [26] as shown in Fig.16. Thus, a bimodal distribution behavior may be observed and different  $\beta$  values could be extracted from IL and high-K, respectively [27]. We show that  $\beta$  slope is found larger under Off-state TDDB (Fig.14) compared to the one expected from standard percolation model under On-state. This higher  $\beta$  value in (4) can be explained by different defect cell size  $a_o$  [28] with (5) [29]. This might be explained by the effect of a longer percolation path from the gate-drain region [30] and distinct oxide defects (Si-O) than interface traps (Si-H as  $P_bO$ ) [4]. This possibly suggests Figs.17a,b that the generated defects under Off mode are tinier and induce longer percolation paths.

**Figure 17.** Schematic illustration of BD triggering through percolation paths showing defect generation into dielectric with On-state TDDB cell size  $a_{0\text{-}On}$  larger than Off mode one  $a_{0\text{-}Off}$ . (a) On-state TDDB uniform stress and (b) Off-state non-uniform stress.

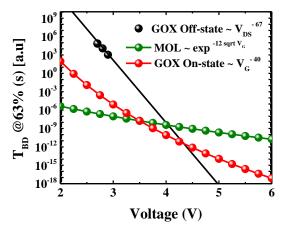

**Fig.18** compares the voltage acceleration factor (VAF) corresponding to MOL dielectric BD and gate-oxide BD ( $T_{\rm BD}$  at 63%) characterized under On- and Off- state TDDB. The results differ significantly as a function of stress voltage. As matter of fact, MOL TDDB follows a square-root VAF dependence, while On-state TDDB follows a gate-voltage power law. Therefore, it indicates that BD mechanism under Off-state does not correspond to spacer BD but rather to gate-oxide dielectric breakdown at the drain- edge.

**Figure 18.** Average  $T_{BD}$  at 63% comparison between gate oxide TDDB stress under Off, On modes and middle of line for FDSOI N-FET  $L_G=30 \text{nm}$ . Voltage acceleration factor VAF obtained under Off-state is different from the spacer dielectric VAF. Off-state  $T_{BD}$  voltage range is extremely tight. MOL and On-state  $T_{BD}$  data are projected.

#### IV. Off-mode $T_{BD}$ modelling from $E_{\rm LAT}$ to $IG_{\rm Off}(T_0)$

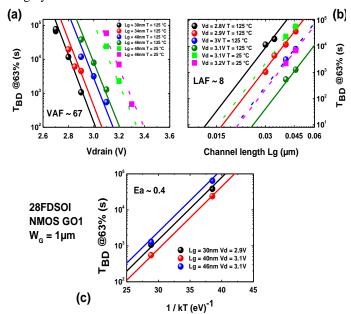

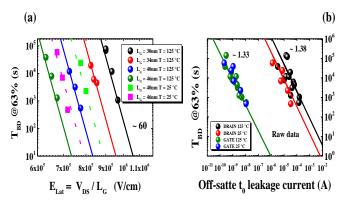

To investigate the potential role of hot-carrier injection under Off-state BD, we independently modelled TDDB in (6)-(7) as a function of  $V_{DS}$ ,  $L_G$  and temperature in **Figs.19** and **Figs.20a-c**. We show that  $T_{BD}$  increases with  $L_G$  (**Fig.19**) without changing markedly  $\beta$ , VAF (**Fig.20.a**), and gatelength acceleration factors (LAF) (**Fig.20.b**). We further extracted temperature activation  $E_a$  (**Fig.20.c**) which is used in (6)-(7):

$$T_{BD} = A \cdot L_G^{LAF} \cdot V_D^{-VAF} \cdot \frac{1}{W_G}^{\frac{1}{\beta}} \cdot e^{(\frac{\ln(-\ln(1-F))}{\beta})} \cdot e^{(\frac{E_G}{KT})}$$

**Figure 19.** TDDB time to failure distribution for various  $L_G=30$  to 46nm from FDSOI N-FETs ( $W_G=1\mu m$ ) at fixed drain voltage  $V_{DS}\!\!=\!\!2.9V$ . Breakdown occurs later for longer devices.

From experimental data, VAF and LAF are found to follow different dynamics. The strong effects of  $L_G$  and  $V_{DS}$  (Figs.19-

20) suggest that Off-state TDDB damage is highly correlated to carrier energy and the amount of injected HC into the gate-oxide induced by impact-ionization from the drain junction. Plotting the results as a function of the average lateral field is given in Figs.21.a. A simplified peak value  $E_{max} \cong V_{DS}/L_G$  at the gate-drain edge does not give satisfactory results, due to  $L_G$  and temperature dependencies, since curves are shifted for devices with various  $L_G$  stressed at equivalent electric field. Under On-state stressing, charge trapping and scatterings lead to band diagram deformation modifying the electrical field profile which becomes non-uniform while the currents remain roughly

**Figure 20.**  $T_{BD}$  time to failure acceleration factors extracted for GO1 28nm FDSOI under Off-state stressing at 125°C (solid lines) and 25°C (dash line). (a)  $T_{BD}$  obtained at 63% vs. drain voltage  $V_{DS}$  with various gate-length  $L_G$ . (b)  $T_{BD}$  plotted at 63% vs.  $L_G$  with various  $V_{DS}$ . (c) Temperature dependence gives small thermal activation. Common VAF (a), LAF (b) and  $E_a$  (c) are obtained independently to  $L_G$  and stressing drain bias  $V_{DS}$ .

**Figure 21.** Lifetime plots as  $T_{BD}$  at 63% for 28nm N-FET (a) vs. electrical field Emax  $\cong V_{DS}/L_G$  enlightening  $L_G$  dependence between 25°C (dash lines) and 125°C (solid lines) and (b) vs. drain and gate oxide initial leakage current overcoming  $L_G$  dependence between 25°C and 125°C. This shows better lifetime monitoring using gate leakage and slightly more dispersion on drain side in 28nm N-FETs.

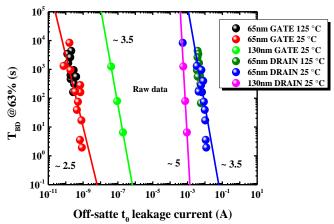

**Figure 22.**  $T_{BD}$  at 63% lifetime model as a function of initial ( $t_0$ ) leakage current in 65nm and 130nm N-FETs gate current and drain current monitors between 25°C and 125°C.

constant (Fig. 17.a). Under Off-state, the electrical field is far less uniform (Fig.16, Fig. 17.b). Hence TDDB results are analyzed as a function of drain leakage current  $I_{D.Off}(V_{GS}=0)$ corresponding to the bias point of I<sub>g,Off</sub> [6]. We found in Fig.21.b with (7) that  $T_{BD}$  results for various  $V_{DS}$ ,  $L_G$  and temperature lie on the same dependence with initial gate current  $I_{G,Off}(t_0)$  with p= -1.3, for same level of drain leakage current. The same trend and co-modality are shown in Fig.22 for different technologies (65nm and 130nm CMOS nodes). Longer devices are exposed to reduced electric field into the channel Fig.23 and Si/SiO<sub>2</sub>/HfO<sub>2</sub> stack at a fixed (half) position during Off-state TDDB. This explains the difference in T<sub>BD</sub> results observed for various channel length in Fig.19 and Fig.21b. Indeed, in the existing literature only few investigations are given on the dependencies between Offstate effective electric field and current with V<sub>DS</sub> and L<sub>G</sub>. Thus, in our previous work we modelled the Off current characteristics [6], similarly to a diode-like framework. We believe that leakage Off currents at drain and gate sides represent relevant figure of merits for HC injection and nonconducting HC under Off-state stressing. Leakage can be used as a main monitor for BD characterization and put in a global framework for Off-state T<sub>BD</sub> modelling. Due to the straight correlation between TDDB and initial leakage current I<sub>0</sub>, this brings benefits for a fast reliability monitoring of process robustness against HBD, since initial leakage currents can be easily implemented with measurement tools.

**Figure 23.** Lateral profile of electrical field during Off-state TDDB in channel, interface layer and high-K for different gate channel length  $L_{\rm G}$  (30nm, 34nm, 40nm, 46nm). Average electrical field is higher for shorter device although the peak value at drain edge is approximately the same for all devices.

#### V. CONCLUSION

Breakdown location during Off-state TDDB degradation in HKMG 28nm FDSOI was studied in detail for relevant conditions related to RF millimeter wave applications. We demonstrated the importance of the localized BD events from the middle of the channel to the gate-drain edge in HKMG 28nm FDSOI node where the role of non-conducting HC has been clearly evidenced. A compact device lifetime model based on leakage currents  $I_{G,Off}$  (or  $I_{D,Off}$ ) power-laws in a diode-like framework has been successfully applied. It simultaneously accounts for drain bias  $V_{\rm DS}$ , channel length  $L_{\rm G}$  and temperature dependencies in comparison to the peak lateral field  $E_{\rm max}$  modelling.

#### REFERENCES

- [1]. X. Garros, V. Knopik, N. Revil, A. Divay, J. Cluzel, J. Lugo, A. Giry, X. Federspiel, G. Bertrand, F. Cacho, "A very Robust and Reliable 2.7 GHz + 31dBm Si RFSOI Transistor for Power Amplifier Solutions", 2019 IEEE Int. Electron Devices Meeting (IEDM), pp. 25.5.1-4.

- [2]. A. Divay, J. Forest, V. Knopik, J. Hai, N. Revil, J. Antonijevic, A. Michard, F. Cacho, E. Vincent, F. Gaillard, "65nm RFSOI Power Amplifier Transistor Ageing at mm W frequencies, 14 GHz and 28 GHz", 2021 Int. Electron Devices Meeting (IEDM), pp. 39.3.1-4.

- [3]. J. Hai, F. Cacho, A. Divay, E. Lauga-Larroze, J.-D. Arnould, J. Forest, "Comprehensive Analysis of RF Hot-Carrier Reliability Sensitivity and Design Explorations for 28GHz Power Amplifier Applications", IEEE Int. Reliability Phys. Symp. (IRPS) 2022, 4B.2.1-6.

- [4]. D. Varghese, H. Kufluoglu, V. Reddy, H. Shichijo, D. Mosher, S. Krishnan, M. Ashraful Alam, "OFF-State Degradation in Drain Extended NMOS Transistors: Interface Damage and Correlation to Dielectric Breakdown", IEEE Trans. on Elec. Dev., vol. 54, n°10, pp. 2669- 2678, 2007.

- [5]. D. Varghese, V. Reddy, H. Shichijo, D. Mosher, S. Krishnan, M. A. Alam, "A Comprehensive Analysis of Off-State Stress in Drain Extended PMOS Transistors: Theory and

- Characterization of Parametric Degradation and Dielectric Failure", in Proc. Int. Reliability Physics Symp. (IRPS) 2008, pp. 566-574.

- [6]. T. Garba-Seybou, X. Federspiel, A. Bravaix, F. Cacho, "New Modelling Off-state TDDB for 130nm to 28nm CMOS nodes", Proc. Int. Reliability Phys. Symp. (IRPS) 2022, pp. 11A.3.1–7.

- [7]. S. Kupke, S. Knebel, S. Rahman, S. Slesazeck, T. Mikolajick, R. Agaiby and M. Trentzsch, "Dynamic off-state TDDB of ultra short channel HKMG nFETS and its implications on CMOS logic reliability," 2014 Int. Reliab. Physics Symposium, (IRPS) 2014, pp. 5B.1.1-5B.1.6.

- [8]. M. Toledano-Luque, P. Paliwoda, M. Nour, T. Kauerauf, B. Min, G. Bossu, M. Siddabathula and T. Nigam, "Off-state TDDB in FinFET Technology and its Implication for Safe Operating Area," 2021 IEEE International Reliability Physics Symposium (IRPS), 2021, pp. 1-6.

- [9]. T. Garba-Seybou, X. Federspiel, A. Bravaix, F. Cacho, "Analysis of the interactions of HCD under "On" and "Off" state modes for 28nm FDSOI AC RF modelling", Proc. Int. Reliability Phys. Symp. (IRPS) 2021, pp. 31–35.

- [10].T. Garba-Seybou, A. Bravaix, X. Federspiel, F. Cacho, "Modeling hot carrier damage interaction between on and off modes for 28 nm AC RF applications", Microelectronics Reliability, vol. 126, p. 114342, 2021.

- [11].F. Cacho, A. Bravaix, T. Garba-Seybou, H. Pitard, X. Federspiel, T. Kumar, F. Giner, A. Michard, D. Celeste, B. Miller, "Device Reliability to Circuit Qualification: Insights and Challenges", Proc. International Integrated Reliability Workshop (IIRW) 2022, pp. 1–7, to be published.

- [12].A. Bravaix, E. Kussener, D. Ney, X. Federspiel, F. Cacho, "Hot-carrier induced breakdown events from Off to On mode in NEDMOS", Proc. Int. Reliability Physics Symp. (IRPS) 2020, 3A4-1-6.

- [13].S. Li, A. Bravaix, E. Kussener, D. Ney, X. Federspiel, F. Cacho, "Hot-carrier degradation in P- and N-channel EDMOS for smart power application", Microelectronics Reliability vol. 114, p. 113811, 2020.

- [14] E. Wu, E. Nowak, "Voltage-Splitting Technique for Reliability Evaluation of Off-State Mode of MOSFETs in Ultrathin Gate Oxides", IEEE Electron Device Letters, vol. 25, no. 6, pp. 414-416. June 2004.

- [15].E. Wu, E. Nowak and Wing Lai, "Off-state mode TDDB reliability for ultra-thin gate oxides: New methodology and the impact of oxide thickness scaling," 2004 IEEE International Reliability Physics Symposium. Proceedings (IRPS) 2004, pp. 84-94.

- [16].X. Federspiel, J. Jasse, D. Ney, D. Roy, M. Rafik, "Middle of the Line Dielectrics Reliability and Percolation Modelling through 65nm to 28nm nodes", Proc. International Integrated Reliability Workshop (IIRW) 2019, pp. 1–4.

- [17].R. Degraeve, B. Kaczer, A. De Keersgieter and G. Groeseneken, "Relation between breakdown mode and location in short-channel nMOSFETs and its impact on reliability specifications," in IEEE Transactions on Device and Materials Reliability, vol. 1, no. 3, pp. 163-169, Sept. 2001

- [18].B. Kaczer, R. Degraeve, A. De Keersgieter, K. Van de Mieroop, V. Simons and G. Groeseneken, "Consistent model for short-channel nMOSFET after hard gate oxide breakdown," in IEEE Transactions on Electron Devices, vol. 49, no. 3, pp. 507-513, March 2002.

- [19].L. Gerrer, G. Ghibaudo and M. Rafik, "New Insights Into Oxide Breakdown Current Partitioning Analysis for MOS Devices," in IEEE Transactions on Device and Materials Reliability, vol. 12, no. 1, pp. 180-182, March 2012.

- [20]. A. Diab, X. Garros, M. Rafik, X. Federspiel, E. Vincent and G. Reimbold, "Impact of gate impedance on dielectric breakdown evaluation for 28 nm FDSOI transistors," Microelectronic Engineering, vol. 178, pp. 21-25, 2017.

- [21].A. P. Nguyen, X. Garros, M. Rafik, F. Cacho, D. Roy, X. Federspiel, F. Gaillard, "Impact of Passive & Active Load Gate Impedance on Breakdown Hardness in 28nm FDSOI Technology", IEEE International Reliability Physics Symposium (IRPS), 2019, pp. 1-5.

- [22].Sentaurus Process User Guide, Version P-2019.03, March 2019.

- [23]. Sentaurus Device User Guide, Version P-2019.03, March 2019.

- [24]. Chynoweth, A. G. (1958) "Ionization Rates for Electrons and Holes in Silicon". Physical Review, 109 (5). 1537-1540.

- [25] R. Van Overstraeten, H. De Man, "Measurement of the ionization rates in diffused silicon p-n junctions," Solid-State Electronics, Volume 13, Issue 5, 1970, Pages 583-608, ISSN 0038-1101.

- [26].T. Nigam, A. Kerber and P. Peumans, "Accurate model for time-dependent dielectric breakdown of high-k metal gate stacks," 2009 IEEE International Reliability Physics Symposium, pp. 523-530.

- [27].E. Y. Wu, "A new formulation of breakdown model for highκ/SiO2 stack dielectrics," 2013 IEEE Int. Reliability Physics Symposium (IRPS), 2013, pp. 5A.4.1-5A.4.7.

- [28].J. Sune, "New physics-based analytic approach to the thinoxide breakdown statistics," in IEEE Electron Device Letters, vol. 22, no. 6, pp. 296-298, June 2001.

- [29].J. Sune, S. Tous, E. Y. Wu, "Analytical Cell-Based Model for the Breakdown Statistics of Multilayer Insulator Stacks," in IEEE Electron Device Letters, vol. 30, no. 12, pp. 1359-1361, Dec. 2009.

- [30].D. Varghese, H. Kufluoglu, V. Reddy, H. Shichijo, D. Mosher, "Multi-probe Two-Dimensional Mapping of Off-State Degradation in DeNMOS Transistors: How and Why Interface Damage Predicts Gate Dielectric Breakdown," 2007 IEEE Int. Electron Devices Meeting, pp. 505-508.