# FM101-CG Hardware Guide

V1.0

www.fibocom.com

#### Copyright

Copyright ©2021 Fibocom Wireless Inc. All rights reserved. Without the prior written permission of the copyright holder, any company or individual is prohibited to excerpt, copy any part of or the entire document, or transmit the document in any form.

#### Notice

The document is subject to update from time to time owing to the product version upgrade or other reasons. Unless otherwise specified, the document only serves as the user guide. All the statements, information and suggestions contained in the document do not constitute any explicit or implicit guarantee.

#### Trademark

Fibocon The trademark is registered and owned by Fibocom Wireless Inc.

#### Contact

Website: https://www.fibocom.com/en/

Address: Floor 10, Building A, Shenzhen International Innovation Valley, First Stone Road, Xili Community, Xili Street, Nanshan District, Shenzhen Tel: +86 755-26733555

## Contents

| Change History                          |

|-----------------------------------------|

| 1. Foreword                             |

| 1.1. Document Description               |

| 1.2. Safety Instructions                |

| 2. Product Overview                     |

| 2.1. Product Introduction               |

| 2.2. Product Specifications             |

| 2.2.1. Radio Frequency Features         |

| 2.2.2. Other Key Features               |

| 2.3. Supported CA Combinations 11       |

| 2.4. Functional Block Diagram 11        |

| 2.5. Evaluation Board                   |

| 3. Pin Definition                       |

| 3.1. Pin Distribution                   |

| 3.2. Pin Function                       |

| 4. Electrical Characteristics           |

| 4.1. Limit Voltage Range                |

| 4.1.1. Absolute Limit Voltage           |

| 4.1.2. Recommended Operating Voltage 21 |

| 4.2. Power Consumption                  |

| 5. Functional Interface                 |

| 5.1. Power Supply                       |

| 5.2. Control Interface                  |

| 5.2.1. Power on/off                     |

| 5.2.1.1. Power on                       |

| 5.2.1.2. Power-on Sequence              |

| 5.2.1.3. Power Off                                    |

|-------------------------------------------------------|

| 5.2.2. Reset                                          |

| 5.3. LED1#                                            |

| 5.4. (U)SIM Card Interface                            |

| 5.4.1. (U)SIM Pin Definition                          |

| 5.4.2. (U)SIM Interface Circuit                       |

| 5.4.3. (U)SIM Card Hot Plug                           |

| 5.4.4. (U)SIM Design Requirements                     |

| 5.5. USB Interface                                    |

| 5.5.1. USB Interface Circuit                          |

| 5.5.2. USB Routing Rules                              |

| 5.5.2.1. USB 2.0 Routing Rules                        |

| 5.5.2.2. USB 3.0 Routing Rules 35                     |

| 5.6. I <sup>2</sup> C Interface                       |

| 5.7. PCM and I <sup>2</sup> S Digital Audio Interface |

| 5.7.1. PCM Interface Definition                       |

| 5.7.2. PCM Application Circuit                        |

| 5.8. PCIe Interface                                   |

| 5.8.1. PCIe Routing Rules                             |

| 5.8.2. PCIe Application Circuit                       |

| 5.9. Flight Mode Control Interface 41                 |

| 5.10. Sleep/Wakeup Interface                          |

| 6. Radio Frequency                                    |

| 6.1. RF Interface                                     |

| 6.1.1. RF Interface Function                          |

| 6.1.2. RF Connector Performance                       |

| 6.1.3. RF Connector Dimensions                        |

| 6.2. Operating Bands                                  |

| 6.3. Transmitting Power                               |

|   | 6.4. Receiving Sensitivity                                | 46   |

|---|-----------------------------------------------------------|------|

|   | 6.5. GNSS Receiving Performance                           | 46   |

|   | 6.6. Antenna Design                                       | 47   |

|   | 6.7. PCB Routing Design                                   | 47   |

|   | 6.7.1. Routing Rules                                      | . 47 |

|   | 6.7.2. Impedance Design                                   | . 48 |

|   | 6.7.3. 3W Principle                                       | . 48 |

|   | 6.7.4. Impedance Design for Four-layer Board              | . 48 |

|   | 6.8. Main Antenna Design                                  | 50   |

|   | 6.8.1. External Antenna                                   | . 50 |

|   | 6.8.2. Internal Antenna                                   | . 51 |

|   | 6.8.2.1. Design Principle of Internal Antenna             | . 51 |

|   | 6.8.2.2. Internal Antenna Classification                  | . 52 |

|   | 6.8.3. Surrounding Environment Design of Internal Antenna | . 57 |

|   | 6.8.3.1. Handling of Speaker                              | . 57 |

|   | 6.8.3.2. Handling of Metal Structural Parts               | . 57 |

|   | 6.8.3.3. Handling of Battery                              | . 57 |

|   | 6.8.3.4. Location of Large Components in Antenna Area     | . 58 |

|   | 6.8.4. Common Problems of Internal Antenna Overall Design | . 58 |

|   | 6.9. Diversity and MIMO Antenna Design                    | 59   |

|   | 6.10. GNSS Antenna Design                                 | 60   |

|   | 6.11. Other Interfaces                                    | 60   |

| 7 | . Thermal Design                                          | 61   |

| 8 | B. Electrostatic Protection                               | 62   |

| 9 | . Structural Specifications                               | 63   |

|   | 9.1. Product Appearance                                   | 63   |

|   | 9.2. Structural Dimensions                                | 63   |

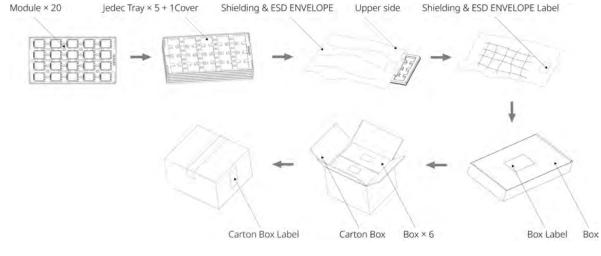

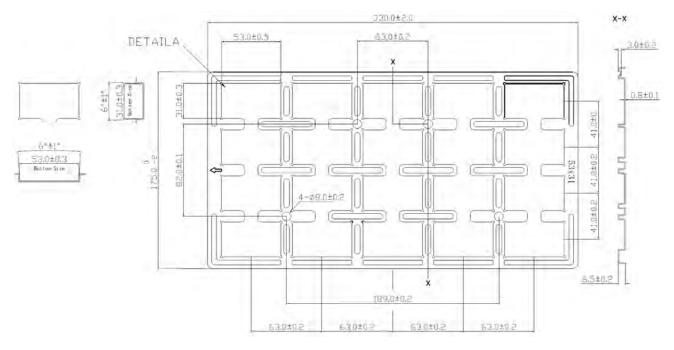

|   | 9.3. Package                                              | 64   |

|   | 9.4. Storage                                              | 65   |

| Appendix A: Acronyms and Abbreviations . |  |

|------------------------------------------|--|

|------------------------------------------|--|

## Change History

V1.0 (2021-11-17) Initial version.

## 1. Foreword

### 1.1. Document Description

This document describes the electrical characteristics, RF performance, dimensions and application environment, etc. of the FM101-CG wireless module. With the assistance of this document and other related documents, application developers can quickly understand the hardware functions of the FM101-CG module and develop product hardware.

### 1.2. Safety Instructions

By following the safety guidelines below, you can ensure your personal safety and help protect the product and work environment from potential damage. Product manufacturers need to communicate the following safety instructions to end users. Fibocom Wireless does not assume any responsibility for the consequences caused by users' misuse because they do not comply with these safety rules.

Road safety first! When you are driving, do not use any handheld mobile device even if it has a hand-free feature. Stop the car before making a call.

Please turn off the mobile device before boarding. The wireless feature of the mobile device is not allowed on the aircraft to prevent interference with the aircraft communication system. Ignoring this note may result in flight safety issue or even violate the law.

When in a hospital or health care facility, please be aware of restrictions on the use of mobile devices. Radio frequency interference may cause medical equipment to malfunction, so it may be necessary to turn off the mobile device.

The mobile device does not guarantee that an effective connection can be made under any circumstances, for example, when there is no prepayment for the mobile device or (U)SIM is invalid. When you encounter the above situation in an emergency, please remember to use emergency calls, and ensure that your device is turned on and in an area with strong signal.

Your mobile device receives and transmits RF signals when it is powered on. Your mobile device will receive and transmit RF signals when it is turned on. RF interference occurs when it is near a TV, radio, computer, or other electronic device.

Keep mobile device away from flammable gases. Turn off the mobile device when you are near to gas stations, oil depots, chemical plants or explosive workplaces. There are potential safety hazards when operating electronic equipment in any potentially explosive area.

## 2. Product Overview

### 2.1. Product Introduction

Fibocom FM101-CG module is designed based on Qualcomm SDX12 platform, supporting Cat 6 network level, and supporting CA network architecture. FM101-CG integrates Baseband, Memory, PMIC, Transceiver, PA and other core devices, supporting TDD-LTE. The maximum downlink rate supported in CA mode is 261 Mbps, and the maximum uplink rate is 30 Mbps. FM101-CG is designed with M.2 package and is applicable to various scenarios such as CPE, VR/AR, gateway, Internet TV set-top box, and intelligent monitoring.

### 2.2. Product Specifications

### 2.2.1. Radio Frequency Features

| Table T. Operating band |                                |  |  |  |  |  |

|-------------------------|--------------------------------|--|--|--|--|--|

| System                  | FM101-CG                       |  |  |  |  |  |

| TDD-LTE Band 42/43/48   |                                |  |  |  |  |  |

|                         | Table 2. Transmission capacity |  |  |  |  |  |

| System                  | FM101-CG                       |  |  |  |  |  |

| Jystem                  |                                |  |  |  |  |  |

|                         | DL peak rate 261 Mbps          |  |  |  |  |  |

| LTE                     |                                |  |  |  |  |  |

#### Table 1. Operating band

#### Table 3. Modulation features

| System | FM101-CG                                     |

|--------|----------------------------------------------|

|        | Support 3GPP R12                             |

|        | Support DL 64QAM, 16QAM and QPSK modulations |

| LTE    | Support UL 16QAM and QPSK modulation         |

|        | Support RF bandwidth 5 MHz to 20 MHz         |

### 2.2.2. Other Key Features

#### Table 4. Other key features

| Item                     | Description                                                                                                                                                                                                                                                    |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply             | DC: 3.135 V–4.4 V<br>Typical voltage: 3.8 V                                                                                                                                                                                                                    |

| Processor                | Qualcomm SDX12, 14nm process, single-core ARM Cortex-A7, up to 1.28 GHz                                                                                                                                                                                        |

| Storage                  | 2Gb LPDDR2 + 2Gb NAND Flash                                                                                                                                                                                                                                    |

| Supported<br>systems     | Linux/Android/Windows                                                                                                                                                                                                                                          |

| Power class              | Class 3 (23dBm ± 2dB) for LTE bands                                                                                                                                                                                                                            |

| Satellite<br>positioning | GPS/GLONASS/Galileo/BDS                                                                                                                                                                                                                                        |

| SMS                      | Support                                                                                                                                                                                                                                                        |

| Audio interface          | Support PCM/I <sup>2</sup> S digital audio interface                                                                                                                                                                                                           |

| USB interface            | A group of USB 3.0 superspeed (SS) interfaces with data transmission<br>rate up to 5 Gbps<br>Compatible with USB 2.0 highspeed (HS) interfaces, with data<br>transmission rate up to 480 Mbps<br>Used for AT command transmission, data transmission, software |

|                          | debugging, software upgrading, etc.                                                                                                                                                                                                                            |

| Item                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCIe interface             | PCIe Gen2 x 1Lane, the maximum transmission rate is 5GT/s, and RC mode is supported                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SIM interface              | 2 groups of SIM card interfaces, supporting dual SIM single standby<br>Support USIM: 1.8 V and 3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| I <sup>2</sup> C interface | 1 group I <sup>2</sup> C with a maximum speed of 3.4 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

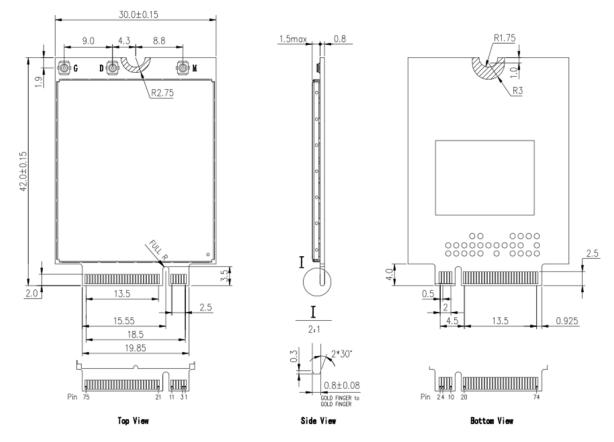

| Physical<br>characteristic | Dimensions: 30 mm × 42 mm × 2.3 mm<br>Packaging: M.2<br>Weight: TBD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Temperature<br>range       | <ul> <li>Operating temperature: -30°C to 75°C</li> <li>The module works normally within this temperature range, and the related performance meets the requirements of 3GPP standards.</li> <li>Extended temperature: -40°C to 85°C</li> <li>The module works normally within this temperature range, and the baseband and RF functions are normal. However, some indicators</li> <li>may exceed the range of 3GPP standards. When the temperature</li> <li>returns to the normal working range of the module, all the indicators</li> <li>of the module meet the requirements of 3GPP standards.</li> <li>Storage temperature: -40°C to 90°C</li> <li>The storage temperature range of the module when the module is powered off.</li> </ul> |

| Software<br>upgrade        | Through USB interface/FOTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Environmental<br>standards | RoHS and halogen-free                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

### 2.3. Supported CA Combinations

#### Table 5. CA combinations supported by FM101-CG

| Combination | FM101-CG |

|-------------|----------|

| 2DLCA       | B42C     |

|             | B48C     |

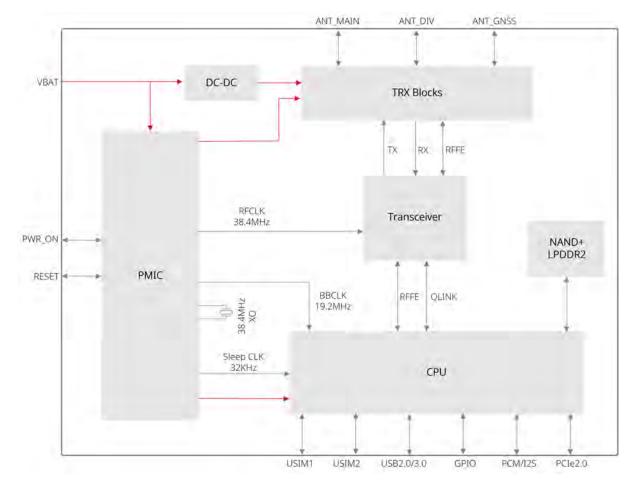

### 2.4. Functional Block Diagram

Functional block diagram shows the main hardware functions of the FM101-CG module, including the baseband and RF functions.

#### Baseband section

- CPU

- PMIC

- LPDDR2

- NAND

- USB, PCIe, (U)SIM, PCM/I<sup>2</sup>S, I<sup>2</sup>C

- LTE TDD controller

#### **RF** section

- RF Transceiver

- RF PA

- RF Switch

- RF filter

- Antenna

Figure 1. Functional block diagram

### 2.5. Evaluation Board

Fibocom provides EVB-M.2 evaluation board to facilitate module debug and testing. For how to use it, see *FIBOCOM EVB-M2 User Guide*.

## 3. Pin Definition

### 3.1. Pin Distribution

The FM101-CG module uses M.2 packaging and have 75 pins in total. The following figure shows the pin mapping.

| 74 | VEC                  | CONFIG_2    | 75 |

|----|----------------------|-------------|----|

| 72 | VCC                  | GND         | 73 |

| 70 | VCC                  | GND         | 71 |

| 68 | I2S MCLK             | CONFIG_1    | 69 |

|    |                      | RESET_N     | 67 |

| 66 |                      | GRFC4       | 65 |

| 64 | COEX_UART_TXD        | GRFC5       | 63 |

| 62 | COEX_UART_RXD        | GRFC6       | 61 |

| 60 | COEX3/GPIO86         | GRFC7       | 59 |

| 58 | RFFE_SDATA           | GND         | 57 |

| 56 | RFFE_SCLK            | REFCLKP     | 55 |

| 54 | PEWAKE#              | REFCLKN     | 53 |

| 52 | CLKREQ#              | GND         | 51 |

| 50 | PERST#               | PERpO       | 49 |

| 48 | UIM2_PWR             | PERnO       | 47 |

| 46 | UIM2_RESET           | GND         | 45 |

| 44 | UIM2_CLK             | PETp0       | 43 |

| 42 | UIM2_DATA            | PETnO       | 41 |

| 40 | SIM2_DETECT          | GND         | 39 |

| 38 | WAKEUP_IN            | USB_SS_RX_P | 37 |

| 36 | UIM1_PWR             | USB_SS_RX_M | 35 |

| 34 | UIM1_DATA            | GND         | 33 |

| 32 | UIM1_CLK             | USB_SS_TX_P | 31 |

| 30 | UIM1_RESET           |             | 29 |

| 28 | 125_WA               | USB_SS_TX_M |    |

| 26 | W_DISABLE2#          | GND         | 27 |

| 24 | 125_TX               | DPR:        | 25 |

| 22 | J2S_RX               | WOWWAN#     | 23 |

| 20 | 125_SCK              | CONFIG_0    | 21 |

|    | Noith                |             |    |

|    |                      | Něrch       |    |

|    | Notch                |             |    |

|    | Notch                | Notern      |    |

| 10 | LED1#                | GND         | 11 |

| 8  | W_DISABLE1#          | USB_DM      | 9  |

| 6  | FULL_CARD_POWER_OFF# | USB_DP      | 7  |

| 4  | VCC                  | GND         | 5  |

| 2  | VEE                  | GND         | 3  |

|    |                      | CONFIG_3    | 1  |

Figure 2. Pin mapping

### 3.2. Pin Function

The FM101-CG module pin function is described in the following table.

| Pin<br>Number | Pin Name                     | I/O | Reset<br>Status | Pin Description                                                                         | Туре              |

|---------------|------------------------------|-----|-----------------|-----------------------------------------------------------------------------------------|-------------------|

| 1             | CONFIG_3                     | DO  | NC              | NC, WWAN-PCIe is configured<br>for FM101-CG module, USB_SS<br>interface type M.2 module |                   |

| 2             | VCC                          | PI  | *               | Power input                                                                             | Power<br>supply   |

| 3             | GND                          |     |                 | Ground                                                                                  | Power<br>supply   |

| 4             | VCC                          | PI  | *               | Power input                                                                             | Power<br>supply   |

| 5             | GND                          |     |                 | Ground                                                                                  | Power<br>supply   |

| 6             | FULL_CARD_<br>POWER_OFF<br># | DI  | PU              | Module on/off control, high-level<br>on, low-level off; internal pull-up                | CMOS<br>3.3V/1.8V |

| 7             | USB_DP                       | DIO | *               | USB 2.0 data +                                                                          | 0.3V-3V           |

| 8             | W_DISABLE1<br>#              | DI  | PU              | Turn off WWAN of the module,<br>i.e. flight mode, active low                            | CMOS<br>3.3V/1.8V |

| 9             | USB_DM                       | DIO | *               | USB 2.0 data –                                                                          | 0.3V-3V           |

| 10            | LED1#                        | OD  | Т               | System status indication, open<br>drain output                                          | *                 |

|               |                              |     |                 |                                                                                         |                   |

| Table 6. | M.2   | pin | function | description |

|----------|-------|-----|----------|-------------|

| Tubic 0. | 111.2 | pin | runction | uescription |

| Pin<br>Number | Pin Name | I/O | Reset<br>Status | Pin Description                                                                         | Туре             |

|---------------|----------|-----|-----------------|-----------------------------------------------------------------------------------------|------------------|

| 11            | GND      |     |                 | Ground                                                                                  | Power            |

| 12            | Notch    | *   | *               | Notch groove                                                                            | supply<br>*      |

| 13            | Notch    | *   | *               | Notch groove                                                                            | *                |

| 14            | Notch    | *   | *               | Notch groove                                                                            | *                |

| 15            | Notch    | *   | *               | Notch groove                                                                            | *                |

| 16            | Notch    | *   | *               | Notch groove                                                                            | *                |

| 17            | Notch    | *   | *               | Notch groove                                                                            | *                |

| 18            | Notch    | *   | *               | Notch groove                                                                            | *                |

| 19            | Notch    | *   | *               | Notch groove                                                                            | *                |

| 20            | I2S_SCK  | DO  | PD              | I <sup>2</sup> S serial clock, reserved                                                 | CMOS<br>1.8V     |

| 21            | CONFIG_0 |     | NC              | NC, WWAN-PCIe is configured<br>for FM101-CG module, USB_SS<br>interface type M.2 module |                  |

| 22            | I2S_RX   | DI  | PD              | I <sup>2</sup> S serial data receiving,<br>reserved                                     | CMOS<br>1.8V     |

| 23            | WOWWAN#  | DO  | PD              | Wakeup host                                                                             | CMOS<br>1.8V     |

| 24            | I2S_TX   | DO  | PD              | I <sup>2</sup> S serial data transmission, reserved                                     | CMOS<br>1.8V     |

| 25            | DPR      | DI  | PU              | Dynamic power control for SAR<br>interrupt detection, active low,<br>reserved           | CMOS<br>3.3V/1.8 |

|               |          |     |                 |                                                                                         |                  |

| Pin<br>Number | Pin Name        | I/O | Reset<br>Status | Pin Description                                                    | Туре              |

|---------------|-----------------|-----|-----------------|--------------------------------------------------------------------|-------------------|

| 26            | W_DISABLE2<br># | DI  | PU              | GNSS positioning is disabled,<br>active low, reserved              | CMOS<br>3.3V/1.8V |

| 27            | GND             |     |                 | Ground                                                             | Power<br>supply   |

| 28            | I2S_WA          | DO  | PD              | I <sup>2</sup> S byte selection, left and right channels, reserved | CMOS<br>1.8V      |

| 29            | USB_SS_TX_<br>M | DO  | *               | Ultra high speed USB data<br>transmitting negative                 | *                 |

| 30            | UIM1_RESET      | DO  | L               | SIM card 1 reset                                                   | CMOS<br>3V/1.8V   |

| 31            | USB_SS_TX_P     | AO  | *               | Ultra high speed USB data<br>transmitting positive                 | *                 |

| 32            | UIM1_CLK        | DO  | L               | SIM card 1 clock                                                   | CMOS<br>3V/1.8V   |

| 33            | GND             |     |                 | Ground                                                             | Power<br>supply   |

| 34            | UIM1_DATA       | DIO | L               | SIM card 1 data                                                    | CMOS<br>3V/1.8V   |

| 35            | USB_SS_RX_<br>M | AI  | *               | Ultra high speed USB data receiving negative                       | *                 |

| 36            | UIM1_PWR        | PO  | *               | SIM card 1 power supply,<br>3V/1.8V                                | CMOS<br>3V/1.8V   |

| 37            | USB_SS_RX_P     | AI  | *               | Ultra high speed USB data<br>receiving positive                    | *                 |

| 38            | WAKEUP_IN       | DI  | *               | Peripheral wake-up module<br>control signal                        | CMOS<br>1.8V      |

|               |                 |     |                 |                                                                    |                   |

| nt © Fibocom Wireless Inc. |  |

|----------------------------|--|

| Pin<br>Number | Pin Name        | I/O | Reset<br>Status | Pin Description                                                                                                                                      | Туре              |

|---------------|-----------------|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 39            | GND             |     |                 | Ground                                                                                                                                               | Power<br>supply   |

| 40            | SIM2_DETEC<br>T | DI  | *               | SIM card 2 detection, and<br>external pull-up and pull-down<br>are required. A card is available<br>at high level by default,<br>SPI_MISO (Reserved) | CMOS<br>1.8V      |

| 41            | PETn0           | DO  | *               | PCIe data transmitting negative                                                                                                                      | *                 |

| 42            | UIM2_DATA       | DIO | L               | SIM card 2 data, SPI_MOSI<br>(Reserved)                                                                                                              | CMOS<br>3V/1.8V   |

| 43            | PETp0           | DO  | *               | PCIe data transmitting positive                                                                                                                      | *                 |

| 44            | UIM2_CLK        | DO  | L               | SIM card 2 clock, SPI_CLK<br>(Reserved)                                                                                                              | CMOS<br>3V/1.8V   |

| 45            | GND             |     |                 | Ground                                                                                                                                               | Power<br>supply   |

| 46            | UIM2_RESET      | DO  | L               | SIM card 2 reset,<br>SPI_CS(Reserved)                                                                                                                | CMOS<br>3V/1.8V   |

| 47            | PERn0           | DI  | *               | PCIe data receiving negative                                                                                                                         | *                 |

| 48            | UIM2_PWR        | PO  | *               | SIM card 2 power supply                                                                                                                              | CMOS<br>3V/1.8V   |

| 49            | PERp0           | DI  | *               | PCIe data receiving positive                                                                                                                         | *                 |

| 50            | PERST#          | DI  | PD              | Module PCIe interface reset.<br>Active low, and an external pull-<br>up resistor is required                                                         | CMOS<br>3.3V/1.8V |

| 51            | GND             |     |                 | Ground                                                                                                                                               | Power<br>supply   |

| Pin<br>Number | Pin Name           | I/O | Reset<br>Status | Pin Description                                                                                                      | Туре              |

|---------------|--------------------|-----|-----------------|----------------------------------------------------------------------------------------------------------------------|-------------------|

| 52            | CLKREQ#            | DIO | Т               | PCIe clock request signal, active<br>low, open drain output, an<br>external pull-up resistor needs<br>to be reserved | CMOS<br>3.3V/1.8V |

| 53            | REFCLKN            | DIO | *               | PCIe reference clock differential negative signal                                                                    | *                 |

| 54            | PEWAKE#            | DO  | Т               | PCIe wake-up signal, active low,<br>open drain output, an external<br>pull-up resistor is required                   | CMOS<br>3.3V/1.8V |

| 55            | REFCLKP            | DIO | *               | PCIe reference clock differential positive signal                                                                    | *                 |

| 56            | RFFE_SCLK          | DO  | PD              | RFFE-MIPI serial clock signal,<br>I2C_SCL (Reserved)                                                                 | CMOS<br>1.8V      |

| 57            | GND                |     |                 | Ground                                                                                                               | Power<br>supply   |

| 58            | RFFE_SDATA         | DIO | PD              | RFFE-MIPI serial data signal,<br>I2C_SDA (Reserved)                                                                  | CMOS<br>1.8V      |

| 59            | GRFC7*             | DO  | PD              | Tuning antenna control bit,<br>reserved                                                                              | CMOS<br>1.8V      |

| 60            | COEX3/GPIO<br>86   | DI  | *               | LTE/WLAN common control signal                                                                                       | CMOS<br>1.8V      |

| 61            | GRFC6*             | DO  | PD              | Tuned antenna control bit 1, reserved                                                                                | CMOS<br>1.8V      |

| 62            | COEX_UART_<br>RXD* | DI  |                 | LTE and WLAN share a serial port receiving signal line, reserved                                                     | CMOS<br>1.8V      |

|               |                    |     |                 |                                                                                                                      |                   |

| Pin<br>Number | Pin Name           | I/O | Reset<br>Status | Pin Description                                                                                                          | Туре            |

|---------------|--------------------|-----|-----------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|

| 63            | GRFC5*             | DO  | PD              | Tuned antenna control bit 2, reserved                                                                                    | CMOS<br>1.8V    |

| 64            | COEX_UART_<br>TXD* | DO  |                 | LTE and WLAN share a serial port transmission signal line, reserved                                                      | CMOS<br>1.8V    |

| 65            | GRFC4*             | DO  | PD              | Tuned antenna control bit,<br>reserved                                                                                   | *               |

| 66            | UIM1_DETEC<br>T    | DI  | PU              | SIM card 1 detection, external<br>pull-up and pull-down are<br>required. A card is available at<br>high level by default | CMOS<br>1.8V    |

| 67            | RESET_N            | DI  | PU              | Module reset. Active low                                                                                                 | CMOS<br>1.8V    |

| 68            | I2S_MCLK           | DO  | *               | I2S MCLK clock output                                                                                                    | *               |

| 69            | CONFIG_1           | DO  | GND             | GND, WWAN–PCIe is configured<br>for the FM101-CG module,<br>USB_SS interface type M.2<br>module                          |                 |

| 70            | VCC                | PI  | *               | Power input                                                                                                              | Power<br>supply |

| 71            | GND                |     |                 | Ground                                                                                                                   | Power<br>supply |

| 72            | VCC                | PI  | *               | Power input                                                                                                              | Power<br>supply |

| 73            | GND                |     |                 | Ground                                                                                                                   | Power<br>supply |

|               |                    |     |                 |                                                                                                                          |                 |

| Pin<br>Number | Pin Name | I/O | Reset<br>Status | Pin Description                                                                         | Туре            |

|---------------|----------|-----|-----------------|-----------------------------------------------------------------------------------------|-----------------|

| 74            | VCC      | PI  | *               | Power input                                                                             | Power<br>supply |

| 75            | CONFIG_2 | DO  | NC              | NC, WWAN-PCIe is configured<br>for FM101-CG module, USB_SS<br>interface type M.2 module |                 |

Pins marked with \* are reserved functions or under development. Unused pins remain floating.

#### Table 7. I/O parameter description

| Туре | Description          |

|------|----------------------|

| PI   | Power input          |

| PO   | Power output         |

| DI   | Digital input        |

| DO   | Digital output       |

| DIO  | Digital input/output |

| AI   | Analog input         |

| AO   | Analog output        |

| AIO  | Analog input/output  |

| OD   | Open drain           |

## 4. Electrical Characteristics

### 4.1. Limit Voltage Range

The limit voltage includes the absolute limit voltage and the operating limit voltage. The absolute limit voltage is the maximum voltage that the module can bear, beyond which the module may be damaged. The operating limit voltage is the normal operating voltage range of the module, beyond which the module will have an abnormal performance.

### 4.1.1. Absolute Limit Voltage

The following table describes the absolute limit voltage ranges of FM101-CG module.

| Parameter | Description                        | Minimum<br>Value (V) | Typical Value | Maximum<br>Value (V) |

|-----------|------------------------------------|----------------------|---------------|----------------------|

| VBAT      | Power supply                       | -0.3                 | 3.8           | 4.75                 |

| GPIO      | Digital IO level supply<br>voltage | -0.3                 | 1.8           | 2.1                  |

Table 8. Absolute limit voltage range

### 4.1.2. Recommended Operating Voltage

#### Table 9. Recommended operating voltage (signal)

|                | Logical low level    |                      | Logical high level   |                      |  |

|----------------|----------------------|----------------------|----------------------|----------------------|--|

| Signal         | Minimum<br>Value (V) | Maximum<br>Value (V) | Minimum<br>Value (V) | Maximum<br>Value (V) |  |

| Digital input  | -0.3                 | 0.36                 | 0.7 × VDD            | VDD + 0.3            |  |

| Digital output | 0                    | 0.45                 | VDD - 0.45           | VDD                  |  |

| RESET_N        | -0.3                 | 0.5                  | 1.25                 | 1.89                 |  |

| FCPO#          | -0.3                 | 0.5                  | 1.25                 | 1.89                 |  |

| Parameter | I/O | Minimum Value (V) | Typical Value | Maximum Value (V) |

|-----------|-----|-------------------|---------------|-------------------|

| VBAT      | PI  | 3.135             | 3.8           | 4.4               |

| USIM1_VDD | PO  | 1.75/2.8          | 1.8/2.85      | 1.85/2.928        |

| USIM2_VDD | PO  | 1.75/2.8          | 1.8/2.85      | 1.85/2.928        |

Table 10. Recommended operating voltage (power supply)

Image: Commended operating voltage (power supply)

### 4.2. Power Consumption

The power consumption of FM101-CG module measured under 3.8 V power supply is described in the following table. For AT commands used for USB sleep and wakeup, see *Fibocom\_FM101\_AT Commands User Manual*.

| Parameter                                     | Mode      | Status                         | Average Current<br>Typical Value (mA) |

|-----------------------------------------------|-----------|--------------------------------|---------------------------------------|

| $I_{off}$                                     | Power off | Module power-off               | 0.06                                  |

|                                               | TDD-LTE   | Paging Cycle #64 (USB sleep)   | 3.3                                   |

| $I_{sleep}$                                   | TDD-LTE   | Paging Cycle #256 (USB sleep)  | 2.2                                   |

|                                               | Radio Off | AT+CFUN=0 (USB sleep)          | 1.8                                   |

|                                               | TDD-LTE   | Paging Cycle #32 (USB wakeup)  | 33                                    |

|                                               |           | Paging Cycle #64 (USB wakeup)  | 32                                    |

| $I_{idle}$                                    |           | Paging Cycle #128 (USB wakeup) | 31                                    |

|                                               |           | Paging Cycle #256 (USB wakeup) | 31                                    |

|                                               |           | Band42 @+23dBm                 | 450                                   |

| $I_{\text{LTE-RMS}(10\text{MHz }1\text{RB})}$ | TDD-LTE   | Band43 @+23dBm                 | 450                                   |

|                                               |           | Band48 @+23dBm                 | 450                                   |

#### Table 11. Power consumption

#### Table 12. 2CA power consumption

|                         | Transmitting Band@FRB@Data |                                  |  |

|-------------------------|----------------------------|----------------------------------|--|

| 2CA Typical Combination | Transmission Status        | sion Status Typical Current (mA) |  |

| 42C                     | B42+B42 @+21dBm            | TBD                              |  |

| 48C                     | B48+B48 @+21dBm            | TBD                              |  |

## 5. Functional Interface

### 5.1. Power Supply

The following table describes the power interface of FM101-CG module.

| Pin Name | I/O | Pin Number                                  | Description                                           |

|----------|-----|---------------------------------------------|-------------------------------------------------------|

| VBAT     | PI  | 2,4, 70, 72, 74                             | Module power supply, 3.135V–4.4V, 3.8V is recommended |

| GND      | G   | 3, 5, 11, 27, 33, 39,<br>45, 51, 57, 71, 73 | GND, all GND pins must be grounded                    |

Table 13. Power interface

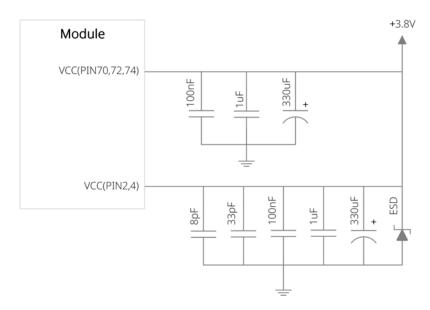

#### Power Input

The FM101-CG module is powered on through the VBAT pin. The following figure shows the recommended power supply design.

Figure 3. Recommended power supply design

The filter capacitor design of power supply is shown in the following table.

| Recommended<br>Capacitor | Application                                | Description                                                                                                                                                                                                                         |

|--------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 330uF x 2                | Voltage stabilizing<br>capacitor           | To reduce the power supply fluctuation<br>when the module works, it is required to<br>adopt low ESR capacitor, which is not less<br>than 440uF, and the driving capacity of<br>VBAT power supply current is not less than<br>2.0 A. |

| 1uF, 100nF               | Digital signal noise                       | Filter out interference caused by clock and digital signals.                                                                                                                                                                        |

| 33pF                     | 850 MHz/900 MHz band                       | Filter out low band RF interference                                                                                                                                                                                                 |

| 8.2pF                    | 1800/1900/2100/2300/<br>2500/2600 MHz band | Filter out middle/high band RF<br>interference.                                                                                                                                                                                     |

#### Table 14. Power supply filter capacitor design

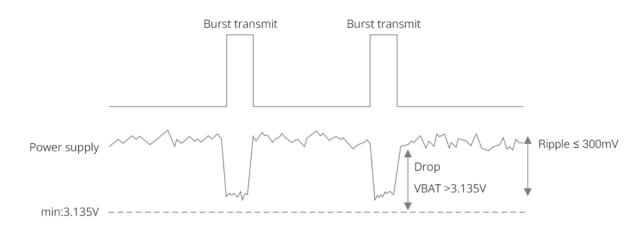

Stable power supply ensures proper operating of the FM101-CG module. During design, ensure that the power supply ripple is less than 300 mV (circuit ESR < 100 m $\Omega$ ). When the module is working in maximum load, ensure that the power supply voltage is not lower than 3.135V. Otherwise, the module may power off or restart. When the module is working in Burst transmit state, the power limit is shown in the following figure.

### 5.2. Control Interface

The module has three control signals for power on/off and reset of the module. The pins are defined in the following table.

| Pin Name                                | I/O | Pin<br>Number | Description                                                                                                                                                            |

|-----------------------------------------|-----|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

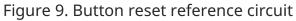

| RESET_N                                 | DI  | 67            | In the power-on state, pull down RESET_N for 0.5s<br>to 3s, and then release it. The module is reset. The<br>chip is internally pulled up.                             |

| FULL_CARD_<br>POWER_OFF<br>#(3.3V/1.8V) | DI  | 6             | Module on/off signal, pull up to power on, and pull<br>down to power off. In the power-off state, pull up<br>the FCP# for more than 1.2s. The module is<br>powered on. |

| Table 15. Contro | ol signal |

|------------------|-----------|

|------------------|-----------|

#### 5.2.1. Power on/off

#### 5.2.1.1. Power on

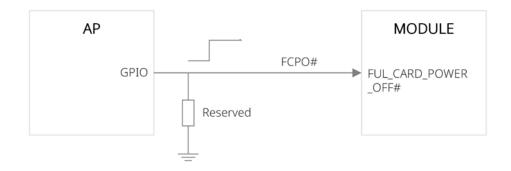

When the module power-on pin FCPO# (FULL\_CARD\_POWER\_OFF#) is connected to an external voltage of 3.3 V or 1.8 V, the module is powered on. When the AP (Application Processor) controls the power-on of the module, it is recommended to use GPIO with the reset status of low or internal pull-down.

Figure 5. AP controls the power-on circuit of the module

#### 5.2.1.2. Power-on Sequence

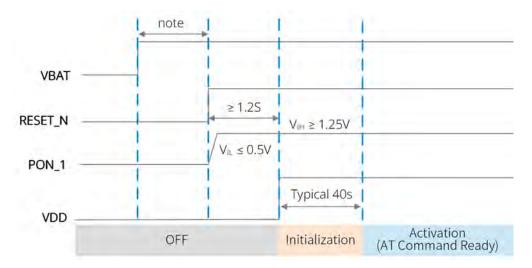

The following figure shows the power-on sequence.

Figure 6. Power-on sequence (FCPO#)

Before pulling the FCPO# pin high, ensure that the VBAT voltage is stable. It is recommended that the time interval between powering on VBAT and pulling low or high the power-on control pin is not less than 40ms. The power-on control is automatically pulled up inside the module.

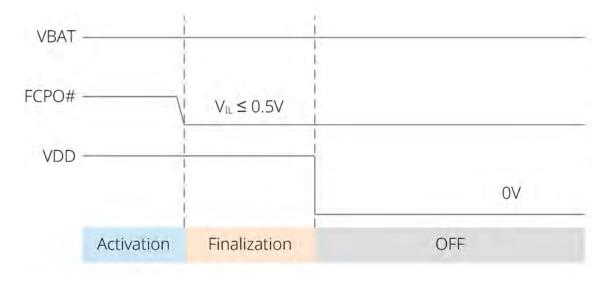

#### 5.2.1.3. Power Off

When the module is powered on, pull down FCPO#, and the module is powered off. The

recommended power-off sequence is shown in the following figure.

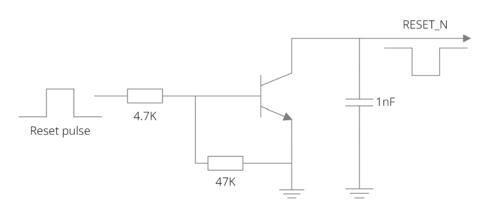

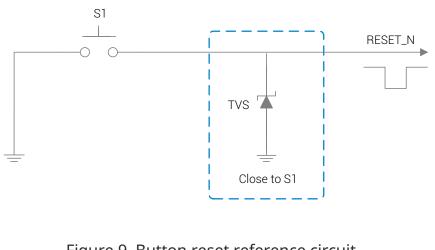

### 5.2.2. Reset

FM101-CG module can be reset by hardware and software.

#### Table 16. Reset methods

| Reset Method   | Action                                                       |

|----------------|--------------------------------------------------------------|

| Hardware reset | Pull down the RESET_N pin for 0.5s or more, and then release |

| Software reset | Send the AT+CFUN=15 command                                  |

Figure 8. OC drive reset reference circuit

Figure 10. Reset sequence

It is recommended to wait at least 20 seconds between two reset operations. The RESET pin can be internally pulled up, without external pull-up. Keep the pin floating when it is not used.

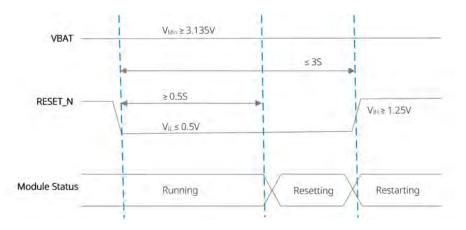

### 5.3. LED1#

The LED1# signal is used to indicate the operating status of the module, as described in the table below.

| Module Operating Mode   | LED1# Signal         |

|-------------------------|----------------------|

| RF function is enabled  | Low level (LED on)   |

| RF function is disabled | High level (LED off) |

The LED driver circuit is shown in the following figure.

Figure 11. Reference circuit of network status indicators

### 5.4. (U)SIM Card Interface

FM101-CG module has built-in (U)SIM card interface, and supports 1.8 V and 3.0 V (U)SIM cards.

### 5.4.1. (U)SIM Pin Definition

(U)SIM pin definition is described in the following table.

| Pin<br>Number | Pin Name   | I/O | Reset<br>Status | Description        | Туре    |

|---------------|------------|-----|-----------------|--------------------|---------|

| 30            | UIM1_RESET | DO  | L               | USIM1 reset        | 1.8V/3V |

| 32            | UIM1_CLK   | DO  | L               | USIM1 clock        | 1.8V/3V |

| 34            | UIM1_DATA  | DIO | L               | USIM1 data         | 1.8V/3V |

| 36            | UIM1_PWR   | РО  |                 | USIM1 power supply | 1.8V/3V |

#### Table 18. (U)SIM pin definition

| Pin<br>Number | Pin Name    | I/O | Reset<br>Status | Description                                                                                                                                            | Туре    |

|---------------|-------------|-----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 40            | SIM2_DETECT | DI  |                 | USIM2 detection Active high<br>by default. And high level<br>indicates a SIM card is<br>inserted; and low level<br>indicates a SIM card is<br>removed. | 1.8V    |

| 42            | UIM2_DATA   | DIO | L               | USIM1 data                                                                                                                                             | 1.8V/3V |

| 44            | UIM2_CLK    | DO  | L               | USIM1 clock                                                                                                                                            | 1.8V/3V |

| 46            | UIM2_RESET  | DO  | L               | USIM1 reset                                                                                                                                            | 1.8V/3V |

| 48            | UIM2_PWR    | РО  |                 | USIM1 power supply                                                                                                                                     | 1.8V/3V |

| 66            | SIM1_DETECT | DI  |                 | USIM1 detection Active high<br>by default. And high level<br>indicates a SIM card is<br>inserted; and low level<br>indicates a SIM card is<br>removed. | 1.8V    |

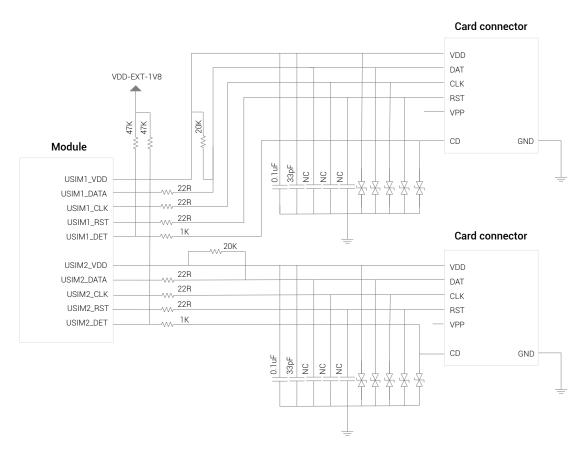

### 5.4.2. (U)SIM Interface Circuit

#### (U)SIM Card Slot with Card Detection Signal

(U)SIM card slot should be selected for (U)SIM design. It is recommended to use (U)SIM card slot with hot plug detection function.

The following figure shows the reference design circuit. When (U)SIM card is inserted, USIM\_DET pin is at high level, when (U)SIM card is removed, USIM\_DET pin is at low level.

Figure 12. (U)SIM card slot with card detection signal

### 5.4.3. (U)SIM Card Hot Plug

The FM101-CG series module supports the (U)SIM card hot plug function. The module detects the status of the USIM1\_DET/USIM2\_DET pin to determine whether a (U)SIM card is inserted or removed.

USIM1\_DET/USIM2\_DET is active high by default (if the card is at high level, the card is inserted; otherwise, the card is removed). The hot plug detection can be enabled/disabled by the AT command as follows.

| AT Command | Function                                  | Remark          |

|------------|-------------------------------------------|-----------------|

| AT+MSMPD=1 | (U)SIM card hot plug detection is enabled | Default setting |

#### Table 19. (U)SIM card hot plug function configuration

| AT Command | Function                                   | Remark                  |

|------------|--------------------------------------------|-------------------------|

| AT+MSMPD=0 | (U)SIM card hot plug detection is disabled | Effective after restart |

### 5.4.4. (U)SIM Design Requirements

(U)SIM circuit design must meet EMC standards and ESD requirements, and at the same time, EMS capability must be improved to ensure that the (U)SIM can work stably. The following points need to be strictly observed in the design:

- (U)SIM card slot should be located as close to the module as possible, and kept away from the RF antenna, DCDC power, clock signal lines and other strong interference sources.

- (U)SIM card slot is covered by metal shield shell to improve EMS.

- The routing length from the module to the (U)SIM card slot shall not exceed 100 mm. Longer cable will reduce signal quality.

- The USIM\_CLK and USIM\_DATA signal lines are grounded and isolated to avoid mutual interference. If conditions do not permit, at least the (U)SIM signal must be grounded as a set.

- The filter capacitor and ESD device of the (U)SIM card signal line are placed close to the (U)SIM card slot.

- The total capacitance of the equivalent capacitance and the parallel filter capacitance of the ESD device is less than 47pF.

- USIM\_DATA requires a pull-up resistor of 20KΩ to USIM\_VDD.

- Refer to the specification of (U)SIM card slot for PCB packaging design. The PCB surface layer under the 6 contactors should be keepout to avoid short circuit caused by the contactor pricked to the copper plane.

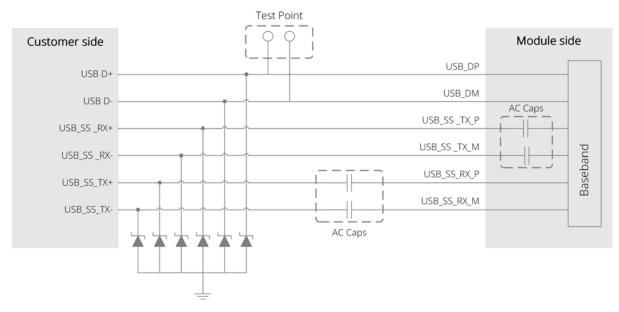

### 5.5. USB Interface

FM101-CG module supports USB 3.0 (5 Gb/s) ultra-high-speed data transmission, and is also compatible with USB high-speed (480 Mb/s) for download, debugging, data transmission and other functions.

USB pin definition is shown in the following table.

| Pin Name    | I/O | Pin Number | Description                                  |

|-------------|-----|------------|----------------------------------------------|

| USB_DP      | AIO | 7          | USB 2.0 differential data signal (+)         |

| USB_DM      | AIO | 9          | USB 2.0 differential data signal (–)         |

| USB_SS_TX_M | AO  | 29         | USB 3.0 differential transmitting signal (–) |

| USB_SS_TX_P | AO  | 31         | USB 3.0 differential transmitting signal (+) |

| USB_SS_RX_M | AI  | 35         | USB 3.0 differential receiving signal (–)    |

| USB_SS_RX_P | AI  | 37         | USB 3.0 differential receiving signal (+)    |

|             |     |            |                                              |

#### Table 20. USB pin definition

### 5.5.1. USB Interface Circuit

The USB interface reference circuit is shown in the following figure.

Figure 13. Reference design of USB interface circuit

### 5.5.2. USB Routing Rules

#### 5.5.2.1. USB 2.0 Routing Rules

Since the module supports USB 2.0 High-Speed, TVS Junction capacitance on the USB\_D+/D– differential signal line must be less than 1 pF, and a 0.5 pF TVS is recommended.

USB\_D- and USB\_D+ are high speed differential signal lines with the maximum transmission rate of 480 Mbit/s. The following rules must be strictly followed in PCB layout:

- USB\_D– and USB\_D+ signal lines should have the differential impedance of  $90\Omega\pm10\Omega$ .

- USB\_D- and USB\_D+ signal line difference must be less than 2mm in length and parallel, avoiding the right-angle routing.

- USB\_D- and USB\_D+ signal lines should be routed on the layer that is closest to the ground layer, and protected with GND all around.

#### 5.5.2.2. USB 3.0 Routing Rules

USB\_SS\_RX\_P/USB\_SS\_RX\_M and USB\_SS\_TX\_P/USB\_SS\_TX\_M are two groups of differential signals, with differential impedance controlled at  $90\Omega \pm 7\Omega$ ; the trace length difference within the differential pair is controlled to  $\leq 0.15$  mm, and the trace length difference between the differential groups is controlled to  $\leq 10$  mm.

Minimize vias during high-speed cabling to ensure continuous impedance.

USB 3.0 signals are super speed differential signal lines with the maximum theoretical transfer rate of 5Gbps. The following rules shall be followed carefully in PCB layout:

- USB\_SS\_TX\_P/USB\_SS\_TX\_M and USB\_SS\_RX\_P/USB\_SS\_RX\_M are two pairs of differential signal lines, and their differential impedance should be controlled as 90Ω±7Ω.

- Traces in the differential pair must be parallel with equal length, and the length

difference should be controlled less than 0.15 mm, avoiding right-angle traces.

- Traces between differential pairs must be parallel with equal length, and the length difference should be controlled less than 10 mm, avoiding right-angle traces.

- The two pairs differential signal lines should be routed on the layer that is closest to the ground layer, and protected with GND all around.

## 5.6. I<sup>2</sup>C Interface

FM101-CG series module supports 1-way  $I^2C$  interface, and the standard  $I^2C$  specification, version 3.0 is applied.

I<sup>2</sup>C external pull-up is required. See Figure 14 for reference design.

| Pin Name | Pin    | Туре | Description                   |

|----------|--------|------|-------------------------------|

|          | Number | 51   |                               |

| I2C_SDA  | 42     | OD   | I <sup>2</sup> C data signal  |

| I2C_SCL  | 43     | OD   | I <sup>2</sup> C clock signal |

Table 21. I<sup>2</sup>C pin definition

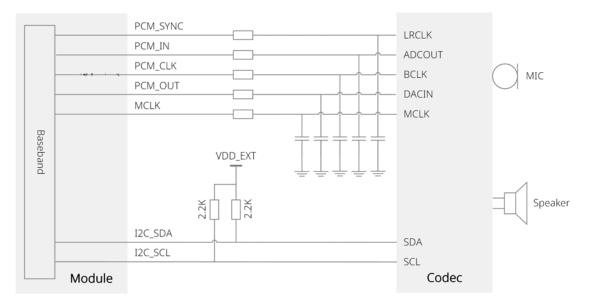

### 5.7. PCM and I<sup>2</sup>S Digital Audio Interface

The FM101-CG module provides a digital audio interface (PCM/I<sup>2</sup>S) for communication with external codec and other digital audio devices.

### 5.7.1. PCM Interface Definition

PCM interface signals include transmission clock PCM\_CLK, frame synchronization signal PCM\_SYNC, and input and output PCM\_IN/PCM\_OUT.

| Pin Name | I/O | Pin Number | Description                                                  |

|----------|-----|------------|--------------------------------------------------------------|

| I2S_SCK  | IO  | 20         | PCM clock signal, I2S_SCLK(Reserved),<br>UART1_RTS(Reserved) |

| I2S_RX   | DI  | 22         | PCM input signal, I2S_D0(Reserved),<br>UART1_RX(Reserved)    |

| I2S_TX   | DO  | 24         | PCM output signal, I2S_D1(Reserved),<br>UART1_CTS(Reserved)  |

| I2S_WA   | IO  | 28         | PCM sync signal, I2S_WS(Reserved),<br>UART1_TX(Reserved)     |

| I2S_MCLK | DO  | 68         | I <sup>2</sup> S main clock signal (reserved)                |

#### Table 22. PCM pin definition

Default transmission clock frequency is TBD MHz, sampling rate is TBD KHz, and resolution is TBD bit. The PCM channel can also be configured as I<sup>2</sup>S interface. Please contact Fibocom technical support for adjustment.

### 5.7.2. PCM Application Circuit

The application reference circuit of the external Codec chip of the PCM interface is shown in the following figure.

### 5.8. PCIe Interface

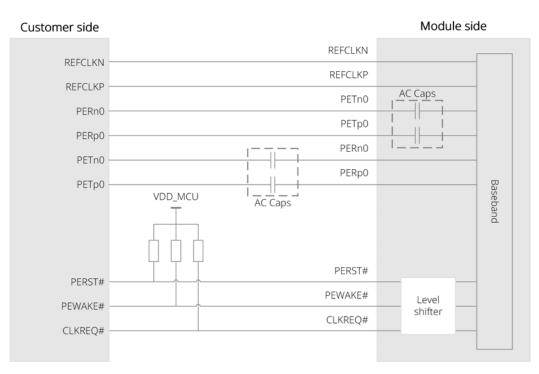

FM101-CG module supports a group of PCIe GEN 2.0 x 1 lanes.

| Pin Name | I/O | Pin<br>Number | Description                                       |

|----------|-----|---------------|---------------------------------------------------|

| PETn0    | DO  | 41            | PCIe data transmitting signal negative            |

| PETp0    | DO  | 43            | PCIe data transmitting signal positive            |

| PERn0    | DI  | 47            | PCIe Data receiving signal negative               |

| PERp0    | DI  | 49            | PCIe Data receiving signal positive               |

| PERST#   | DI  | 50            | PCIe mode reset signal                            |

| CLKREQ#  | DIO | 52            | PCIe clock request signal with external pull-up   |

| REFCLKN  | DIO | 53            | PCIe reference clock signal negative              |

| PEWAKE#  | DO  | 54            | PCIe RC mode wake-up signal with external pull-up |

| REFCLKP  | DIO | 55            | PCIe reference clock signal positive              |

|          |     |               |                                                   |

#### Table 23. PCIe pin definition

### 5.8.1. PCIe Routing Rules

**FM101-CG** module supports PCIe 2.0 x1, including three differential pairs: transmitting pair TXP/N, receiving pair RXP/N and clock pair CLKP/N.

PCIe can achieve the maximum transmission rate of 5GT/s. The following rules must be strictly followed in PCB layout:

- The differential signal pairs are required to be parallel traces with equal length, and the difference in length is less than 0.15 mm.

- The differential signal pair traces shall be as short as possible and be controlled within 15 inch (380 mm) for AP end.

- The impedance of differential signal pair traces is controlled to be  $100\Omega \pm 10\%$ .

- Avoid discontinuous reference ground, such as segment and space.

- When the differential signal traces go through different layers, the via hole of ground signal should be close to that of signal, and generally, each pair of signals require 1-3 ground signal via holes and the traces shall never cross the segment of plane.

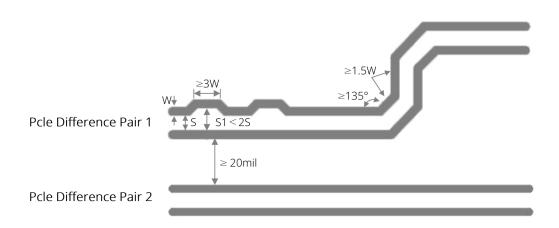

- Try to avoid bended traces and avoid introducing common-mode noise in the system, which will influence the signal integrity and EMI of differential pairs. As shown in the following Figure, the bending angle of all traces should be equal to or greater than 135°, the spacing between differential pair traces should be larger than 20mil, and the traces caused by bending should be greater than 1.5 times trace width at least. When a serpentine route is used for length match with another route, the bended length of each segment shall be at least 3 times the route width (≥ 3W). The largest spacing between the bended part of the serpentine trace and another one of the differential traces must be less than 2 times the spacing of normal differential traces (S1 < 2S).</li>

Figure 15. PCIe routing requirements

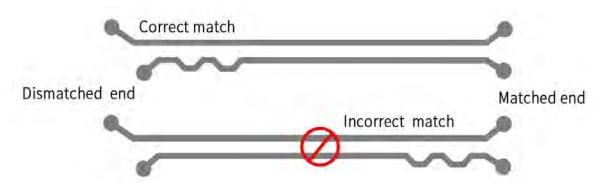

The difference in length of two data lines in differential pair should be within 0.15 mm, and the length match must be met for all parts. When the length match is conducted for the differential lines, the designed position of correct match should be close to that of incorrect match, as shown in the following figure. However, there is no specific requirements for the length match of transmitting pair and receiving pair, that is, the length match is only required in the internal differential lines rather than between different differential pairs. The length match should be close to the signal pin and pass the small-angle bending routing design.

Figure 16. Length match design of PCIe difference pair

#### 5.8.2. PCIe Application Circuit

Please refer to the following figure for PCIe application circuit, and *Fibocom\_FM101-NA\_Reference Design* for details.

Figure 17. PCIe application circuit

### 5.9. Flight Mode Control Interface

W\_DISABLE\_N pin is described in the following table.

| Table 24. W_DISABLE_N pin descript | ion |

|------------------------------------|-----|

|------------------------------------|-----|

| Pin Name    | I/O | Pin Number | Description                          |

|-------------|-----|------------|--------------------------------------|

|             | DI  | 26         | Module flight mode control (internal |

| W_DISABLE_N | DI  | 26         | pulled up by default)                |

FM101-CG module supports two ways as described in the following table to enter flight mode:

| Table 25. Ways for module to enter flight mode |                   |                                                          |  |  |

|------------------------------------------------|-------------------|----------------------------------------------------------|--|--|

| 1                                              |                   | Send AT+GTFMODE=1 to turn on the hardware control flight |  |  |

|                                                |                   | mode function; pulled up or float the pin                |  |  |

|                                                | Hardware GPIO     | The module is in normal mode when W_DISABLE# pin is      |  |  |

|                                                | interface control | pulled up by default. When this pin is pulled down, the  |  |  |

|                                                |                   | module enters flight mode.                               |  |  |

|                                                |                   | The module uses software to control the flight mode by   |  |  |

| 2                                              | AT command        | default. When AT+GTFMODE=0:                              |  |  |

|                                                | control           | run the AT+CFUN=0 command to enter flight mode.          |  |  |

|                                                |                   | run the AT+CFUN=1 command to enter normal mode.          |  |  |

#### - I- I -<u>دا: ما</u> ~

### 5.10. Sleep/Wakeup Interface

When the module is in sleep mode, the module can be awakened by pulling down WAKEUP\_IN pin.

| Pin Name  | I/O | Pin Number | Description                                           |

|-----------|-----|------------|-------------------------------------------------------|

| WAKEUP_IN | DI  | 38         | External device wake-up module, active low by default |

The module supports setting wake-up mode and waking up active level through AT commands. For details of configuration method, see

Fibocom\_FM101-NA\_AT Commands User Manual.

## 6. Radio Frequency

### 6.1. RF Interface

### 6.1.1. RF Interface Function

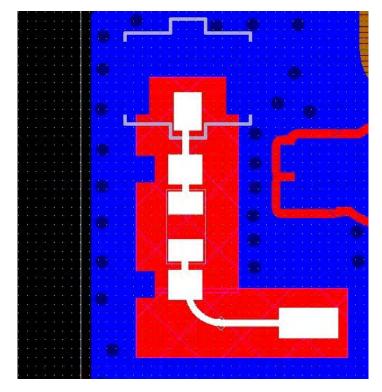

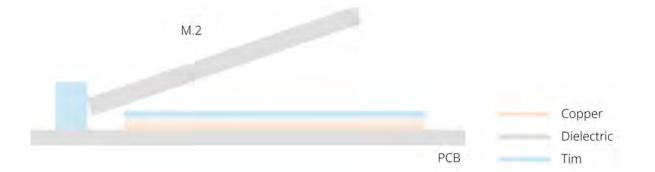

The FM101-CG module supports three RF connectors used for external antenna connection. As shown in the following figure, "M" refers to the RF main antenna for receiving and transmitting RF signals; "D" refers to the diversity antenna for receiving diversity RF signals; "G" refers to GNSS antenna.

### 6.1.2. RF Connector Performance

| Rated Condition |                          | Environmental Condition |

|-----------------|--------------------------|-------------------------|

| Frequency range | Characteristic impedance | Temperature range       |

| DC to 6 GHz     | 50Ω                      | –40°C to +85°C          |

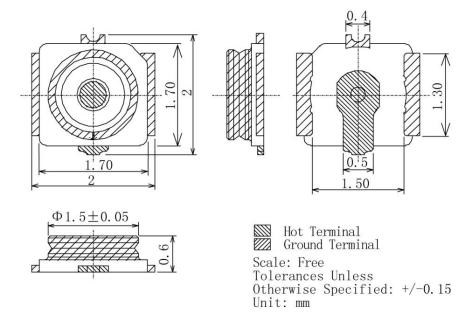

### 6.1.3. RF Connector Dimensions

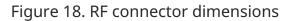

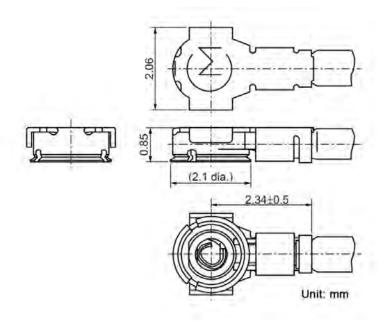

FM101-CG module adopts standard M.2 module RF connectors, the model name is 818004607 from ECT company, and the connector dimensions are 2 mm  $\times$  2 mm  $\times$  0.6 mm, as shown in the following figure.

Figure 19. 0.81 mm coaxial cable matched RF connector dimensions

### 6.2. Operating Bands

| Band    | Mode    | Transmit (MHz) | Receive (MHz) |

|---------|---------|----------------|---------------|

| Band 42 | LTE TDD | 3400~3600      | 3400~3600     |

| Band 43 | LTE TDD | 3600~3800      | 3600~3800     |

| Band 48 | LTE TDD | 3550-3700      | 3550-3700     |

### 6.3. Transmitting Power

The following table describes the RF output power of FM101-CG module.

| Band    | Minimum Value | Maximum Value |

|---------|---------------|---------------|

| LTE TDD | < -40 dBm     | 23 dBm ± 2 dB |

### 6.4. Receiving Sensitivity

| Table 29. FM101-CG dual antenna | receiving sensitivity |

|---------------------------------|-----------------------|

|---------------------------------|-----------------------|

| Mode    | Band    | Main Set Sensitivity<br>Typ (dBm) | Diversity Sensitivity<br>Typ (dBm) |

|---------|---------|-----------------------------------|------------------------------------|

| LTE TDD | Band 42 | -97                               | -98                                |

|         | Band 43 | -97                               | -98                                |

|         | Band 48 | -97                               | -98                                |

### 6.5. GNSS Receiving Performance

The GNSS of FM101-CG module supports GPS/GLONASS/BDS/GALILEO, and the performance parameters of GNSS are shown in the following table.

| Indicator<br>Performance | Description      | Result | Unit  |

|--------------------------|------------------|--------|-------|

|                          | Cold start       | 39     | dB-Hz |

| Sensitivity              | Acquisition      | -145   | dBm   |

|                          | Tracking         | -156   | dBm   |

|                          | Cold Start       | 40     | S     |

| TTFF                     | Warm Start       | 35     | S     |

|                          | Hot Start        | 3      | S     |

| Static Accuracy          | Nominal accuracy | 3      | m     |

#### Table 30. GNSS performance parameters

The above data is an average value obtained by testing some samples at 25°C.

### 6.6. Antenna Design

#### Antenna indicators

The antenna requirements for FM101-CG module are described in the following table.

|                     | Table ST. Module Antenna Requirements                         |

|---------------------|---------------------------------------------------------------|

| FM101-CG module mai | n antenna requirements                                        |

|                     | VSWR: ≤ 2                                                     |

| LTE                 | Input power: > 28dBm                                          |

|                     | Input impedance: 50Ω                                          |

|                     | Antenna gain: < 3.6dBi                                        |

|                     | Antenna isolation: > 25dB                                     |

|                     | Antenna correlation coefficient: < 0.5                        |

|                     | Frequency range: 1559 MHz–1609 MHz                            |

|                     | Polarization direction: right-circular or linear polarization |

| GNSS                | VSWR: < 2:1                                                   |

|                     | Passive antenna gain: > 0dBi                                  |

#### Table 31. Module Antenna Requirements

### 6.7. PCB Routing Design

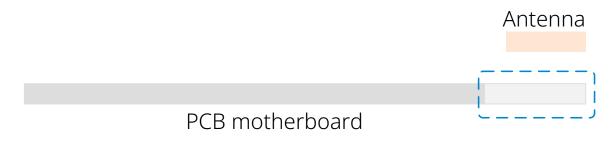

### 6.7.1. Routing Rules

For modules that don't have a RF connector, customers need to route a RF trace to connect to the antenna feeding point or connector. It is recommended to use a microstrip line. The shorter the better. The insertion loss should be controlled less than 0.2dB; and impedance should be controlled within  $50\Omega$ .

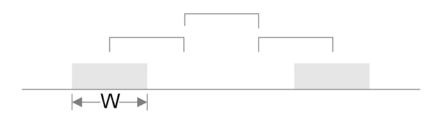

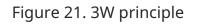

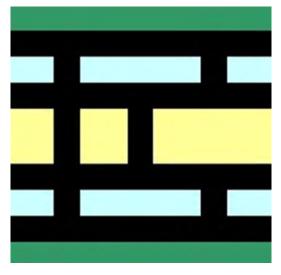

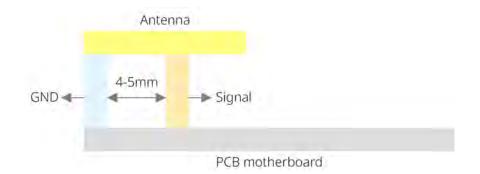

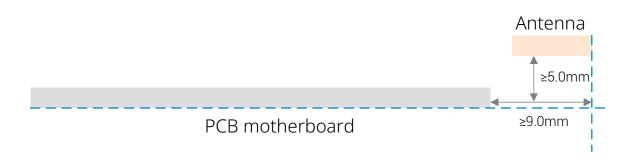

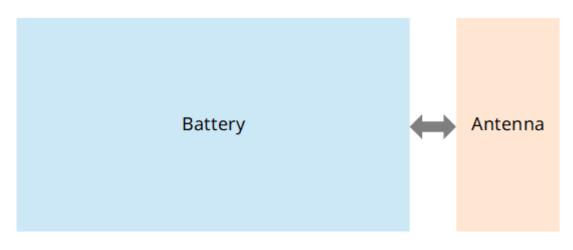

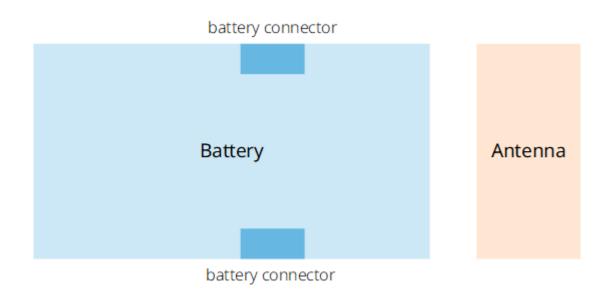

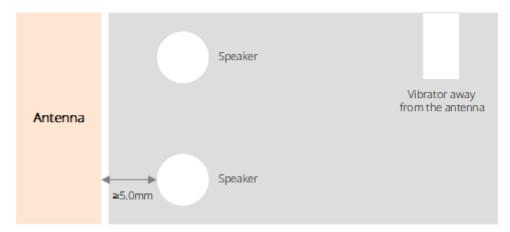

Add a  $\pi$ -type circuit (two parallel-component- grounded pins are connected directly to the main GND) between the module and antenna connector (or feeding point) for antenna debugging.