### **UC Irvine**

### **UC Irvine Electronic Theses and Dissertations**

### **Title**

Reliability and Timing Aware GPU Management on Embedded Systems

### **Permalink**

https://escholarship.org/uc/item/622892sq

### **Author**

Lee, Haeseung

### **Publication Date**

2017

Peer reviewed|Thesis/dissertation

## $\begin{array}{c} {\rm UNIVERSITY\ OF\ CALIFORNIA,} \\ {\rm IRVINE} \end{array}$

# Reliability and Timing Aware GPU Management on Embedded Systems ${\bf DISSERTATION}$

submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in Computer Engineering

by

Haeseung Lee

Dissertation Committee: Professor Mohammad Al Faruque, Chair Professor Fadi Kurdahi Professor Pai Chou

## **DEDICATION**

To my wife and family for their unconditional love and support

## TABLE OF CONTENTS

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ST (                     | OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\mathbf{v}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ST (                     | OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | vii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ST (                     | OF ALGORITHMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | viii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ST (                     | OF ABBREVIATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CKN                      | OWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| JRR                      | ICULUM VITAE                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | xi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BSTI                     | RACT OF THE DISSERTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                              | xiii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.1<br>1.2<br>1.3        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1<br>5<br>11<br>11<br>12<br>14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.1<br>3.2<br>3.3<br>3.4 | GPU Application Model Fault Model Vulnerable Period Estimation for GPU 3.3.1 Latency of Instruction Execution 3.3.2 Control Flow Management During Vulnerable Period Estimation 3.3.3 Vulnerable Period Estimation GPU Architecture Aware Instruction Scheduling to Improve Soft-error Reliability 3.4.1 Vulnerable Period Aware Instruction Scheduling 3.4.2 Example of the Proposed Instruction Scheduling 3.4.3 Comparison with Performance-aware Instruction Scheduling Algorithm | 26<br>27<br>28<br>29<br>35<br>36<br>38<br>40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                          | ST (CST (CST (CKN)) URR 1.1 1.2 1.3 Rela Des 3.1 3.2 3.3                                                                                                                                                                                                                                                                                                                                                                                                                              | ST OF FIGURES ST OF ALGORITHMS ST OF ABBREVIATIONS CKNOWLEDGMENTS URRICULUM VITAE  BSTRACT OF THE DISSERTATION  Introduction 1.1 Introduction 1.2 Motivational Case Studies 1.3 Contributions 1.3.1 Problem and Research Challenges 1.3.2 Our Novel Contributions  Related Works  Design-time: GPU Architecture-aware Instruction Scheduling Algorithm 3.1 GPU Application Model 3.2 Fault Model 3.3 Vulnerable Period Estimation for GPU 3.3.1 Latency of Instruction Execution 3.3.2 Control Flow Management During Vulnerable Period Estimation 3.3 Vulnerable Period Estimation 3.4 GPU Architecture Aware Instruction Scheduling to Improve Soft-error Reliability 3.4.1 Vulnerable Period Aware Instruction Scheduling 3.4.2 Example of the Proposed Instruction Scheduling 3.4.3 Comparison with Performance-aware Instruction Scheduling Algorithm |

| 3.5.2 Experimental Results                                                     | . 53 54 . 55 . 57 . 58   |  |  |  |

|--------------------------------------------------------------------------------|--------------------------|--|--|--|

| 4 Run-time: Part I: Aging-aware GPU Workload Distribution Unit 4.1 Aging Model | <b>54</b> . 55 . 57 . 58 |  |  |  |

| 4.1 Aging Model                                                                | . 55<br>. 57<br>. 58     |  |  |  |

|                                                                                | . 57<br>-<br>. 58        |  |  |  |

|                                                                                | -<br>. 58                |  |  |  |

| 4.2 Process Variation Model                                                    | . 58                     |  |  |  |

| 4.3 Aging-Aware Resource Management on Embedded GPUs under Process Vari-       |                          |  |  |  |

| ation                                                                          |                          |  |  |  |

| 4.3.1 Process Variation-aware Workload Distribution Algorithm                  |                          |  |  |  |

| 4.3.2 Instruction Distribution Unit                                            |                          |  |  |  |

| 4.4 Evaluation                                                                 |                          |  |  |  |

| 4.4.1 Experimental Setup                                                       |                          |  |  |  |

| 4.4.2 Experimental Results                                                     |                          |  |  |  |

| 4.5 Chapter Summary                                                            | . 73                     |  |  |  |

| 5 Run-time: Part II: Timing-aware GPU Workload Scheduling Framew               |                          |  |  |  |

| 5.1 System Model                                                               | . 75                     |  |  |  |

| 5.2 Event-driven Application Model                                             | . 76                     |  |  |  |

| 5.3 Run-time Scheduling Framework for GPU-based Real-time Embedded System      | ms 77                    |  |  |  |

| 5.3.1 Temporal and Spatial Preemption                                          |                          |  |  |  |

| 5.3.2 Workload Splitter                                                        | . 78                     |  |  |  |

| 5.3.3 GPU Execution Schedule Generator                                         | . 85                     |  |  |  |

| 5.3.4 Example of the Scheduling Framework                                      | . 88                     |  |  |  |

| 5.4 Evaluation                                                                 | . 90                     |  |  |  |

| 5.4.1 Experimental Setup                                                       | . 90                     |  |  |  |

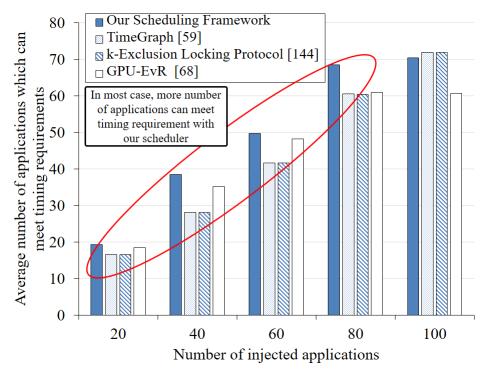

| 5.4.2 Number of the Applications Meeting Deadlines                             | . 92                     |  |  |  |

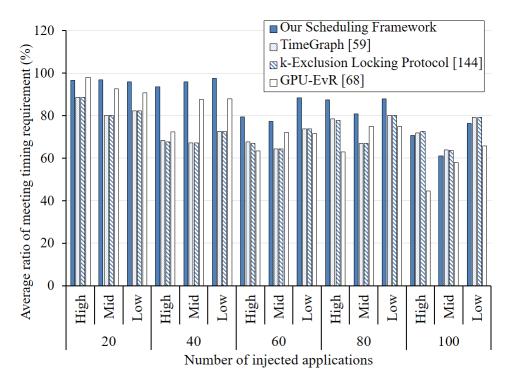

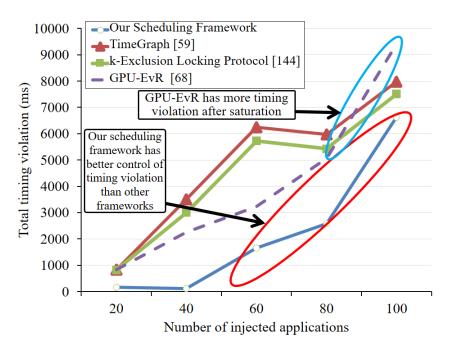

| 5.4.3 Controlling the Effect of Timing Violation                               | . 95                     |  |  |  |

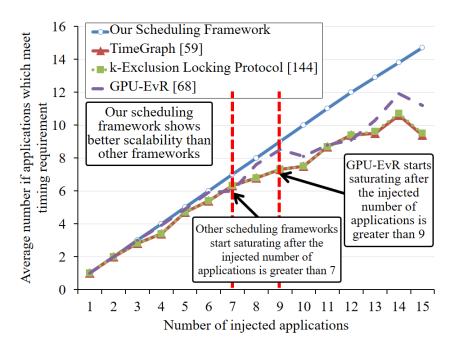

| 5.4.4 Scalability Analysis of the Scheduling Frameworks                        | . 97                     |  |  |  |

| 5.5 Chapter Summary                                                            | . 99                     |  |  |  |

| 6 Conclusion and Future Works                                                  | 100                      |  |  |  |

| 6.1 Conculstion                                                                | . 100                    |  |  |  |

| 6.2 Future Works                                                               | . 102                    |  |  |  |

| Bibliography                                                                   | 103                      |  |  |  |

## LIST OF FIGURES

|      |                                                                                                                                                      | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1  | Intelligent Driving Assistance System Similar to Audi A7's Auto Pilot System Utilizing GPU-based Embedded System [95]                                | 2    |

| 1.2  | Motivational Example Scenario on the GPU-based Embedded System                                                                                       | 6    |

| 1.3  | Kernel Launch Overhead for Varying Number of Threads                                                                                                 | 7    |

| 1.4  | Motivational Example to Illustrate the Relation Between Vulnerable Period and Instruction Schedule                                                   | 8    |

| 1.5  | Example Behavior of the Existing Warp Scheduler and Instruction Dispatcher with/without Process Variation.                                           | 9    |

| 1.6  | Simulation Results to Show the Effect of the Process Variation on Embedded GPUs.                                                                     | 10   |

| 3.1  | Example Pipeline Stages of Arithmetic Instructions                                                                                                   | 30   |

| 3.2  | Example Pipeline Stages of Memory Access Instructions                                                                                                | 31   |

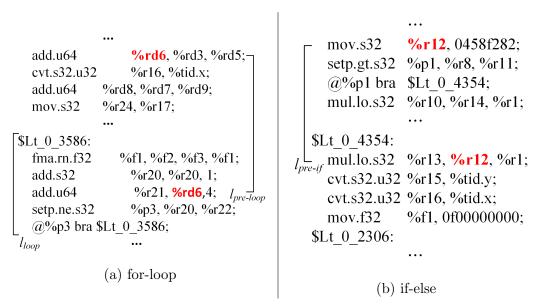

| 3.3  | Example Kernel Code for For-Loop and If-Else                                                                                                         | 36   |

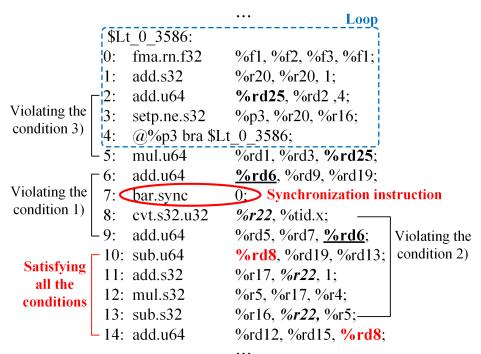

| 3.4  | Example Code for the Proposed Instruction Scheduling                                                                                                 | 41   |

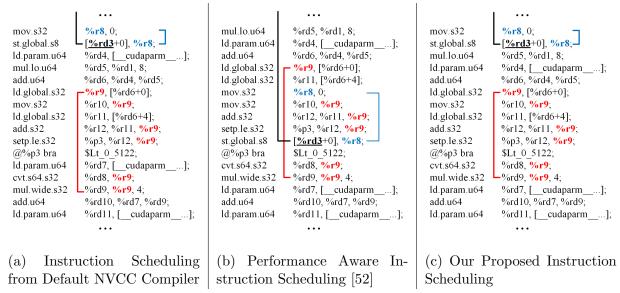

| 3.5  | Instruction Scheduling Results for BFS Application from the NVCC, Performance Aware Instruction Scheduling [52], and Our Proposed Instruction        |      |

|      | Scheduling                                                                                                                                           | 42   |

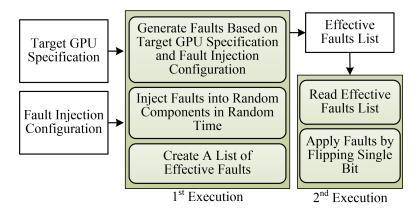

| 3.6  | Experimental Setup for Fault Injection Flow                                                                                                          | 44   |

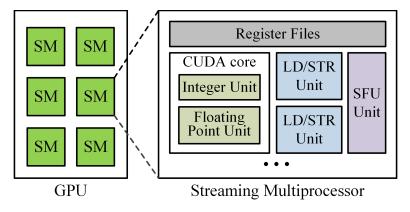

| 3.7  | A High-Level Block Diagram of GPU Architecture Used for Our Experiments.                                                                             | 45   |

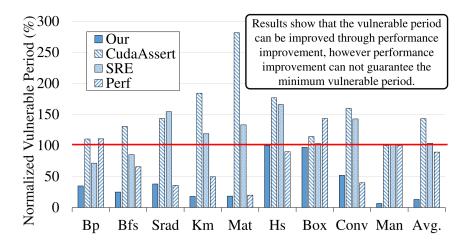

| 3.8  | Vulnerable Period Improvement Compared to [32], [73], and [52]                                                                                       | 47   |

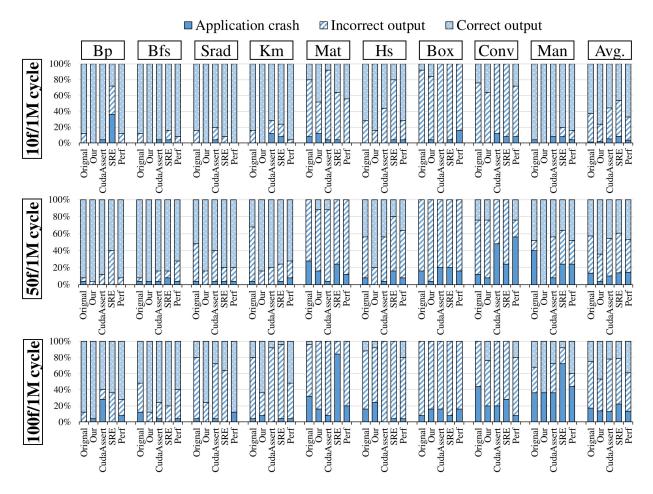

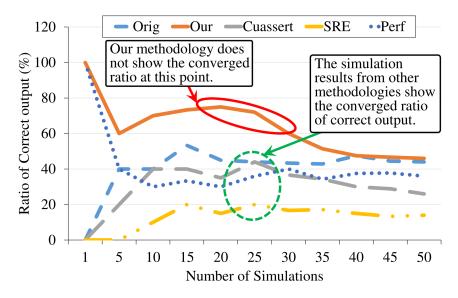

| 3.9  | Soft-error Reliability Improvement Compared to [32], [73], and Performance Driven Instruction Scheduling [52]. Each Application is Executed 25 Times | _,   |

|      | with Different Fault Injection Rates                                                                                                                 | 48   |

| 3.10 | Ratio of Correct Output for Hotspot Application with 50 Faults Injection                                                                             | 50   |

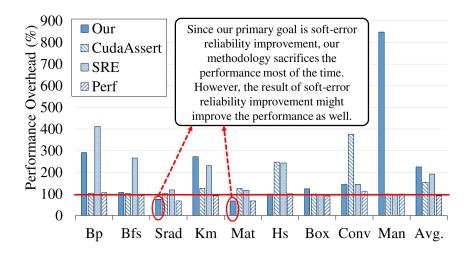

| 3.11 | Performance Overheads Compared to [32], [73], and [52]                                                                                               | 52   |

| 3.12 | Average Power Consumption Overheads Compared to [32], [73], and [52]                                                                                 | 52   |

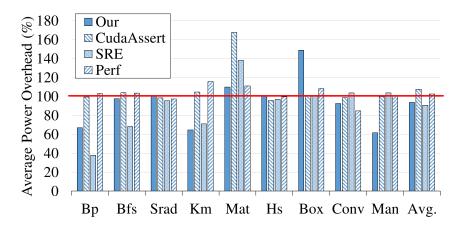

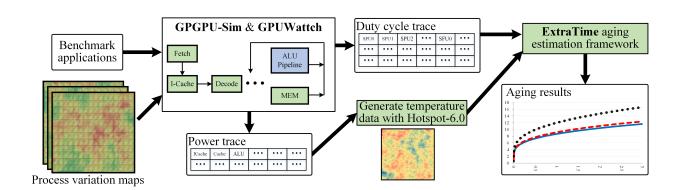

| 4.1  | High-level Flow and Overview of the Proposed Technique                                                                                               | 59   |

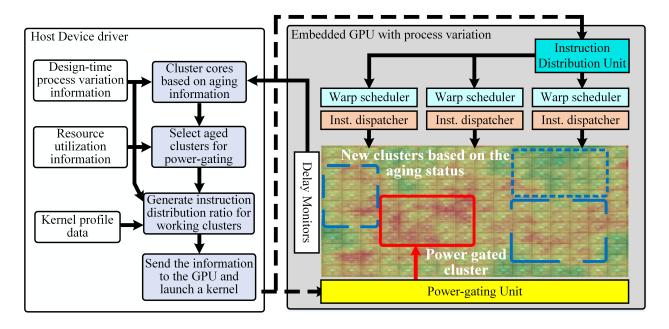

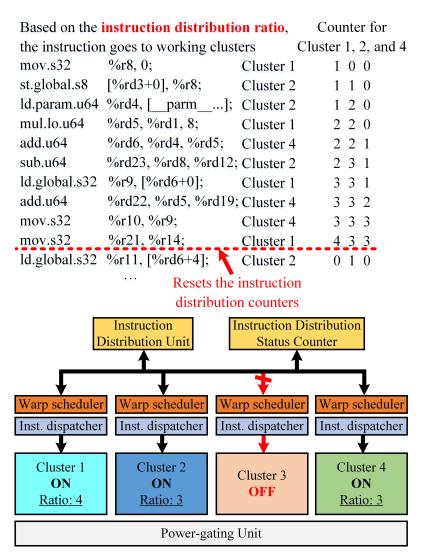

| 4.2  | Example for Estimation of Instruction Distribution Ratio with 4 Working                                                                              |      |

|      | Clusters (WCs)                                                                                                                                       | 63   |

| 4.3  | Example of the Instruction Distribution Unit                                                                                                         | 65   |

| 4.4  | Overview of the Experimental Setup                                                                                                                   | 66   |

|      |                                                                                                                                                      |      |

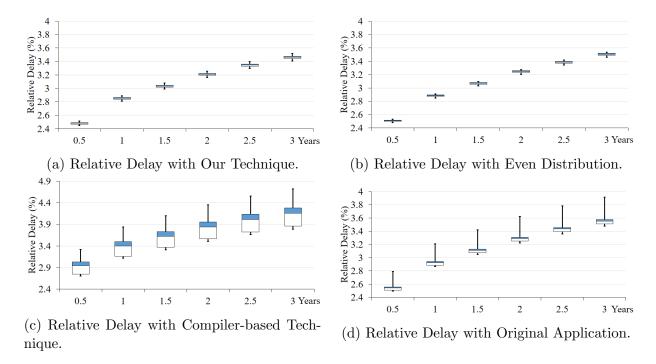

| 4.5  | Relative Delay for SobelFilter Application with 50 Different Process Varia-      |    |

|------|----------------------------------------------------------------------------------|----|

|      | tion Maps: a) Our Technique, b) Even Distribution [69], c) Compiler-based        |    |

|      | Technique [75] and d) Original Application                                       | 68 |

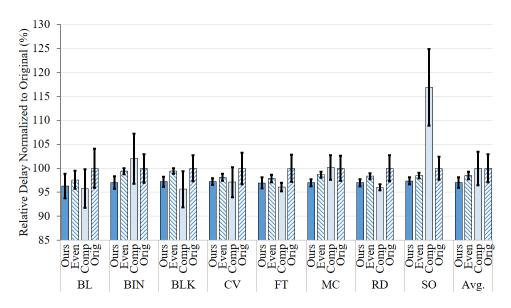

| 4.6  | Normalized Average Relative Delay After 3 Years Compared to the Even             |    |

|      | Distribution [69], the Compiler-based Technique [75], and Original Applications. | 69 |

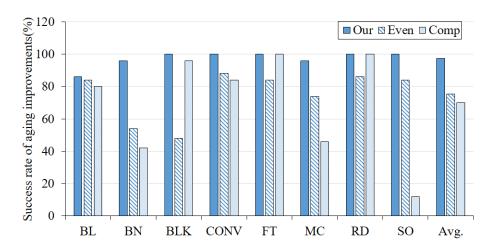

| 4.7  | Success Rate of Aging Improvement for 50 Different Process Variation Maps        |    |

|      | Compared to the Even Distribution [69] and Compiler-based Technique [75].        | 70 |

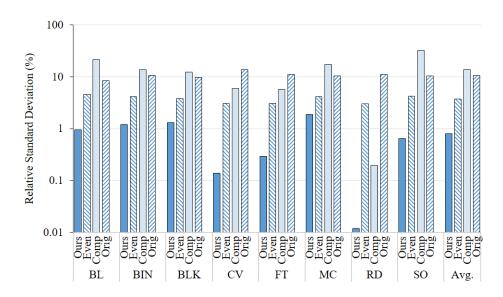

| 4.8  | Average of Relative Standard Deviations of SP/SFU Units Across the Em-           |    |

|      | bedded GPU Compared to the Even Distribution [69], the Compiler-based            |    |

|      | Technique [75], and Original Applications.                                       | 70 |

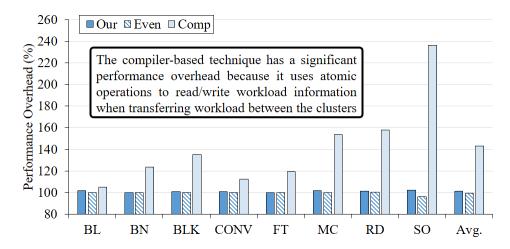

| 4.9  | Normalized Average Performance Overhead for Our Technique, the Even Dis-         |    |

|      | tribution [69], and the Compiler-based Technique [75]                            | 71 |

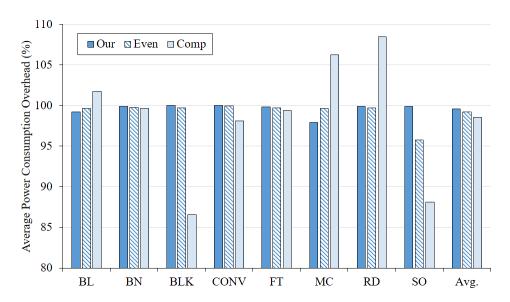

| 4.10 | Normalized Average Power Consumption Overhead for Our Technique, the             |    |

|      | Even Distribution [69], the Compiler-based Technique [75], and Original Ap-      |    |

|      | plications                                                                       | 72 |

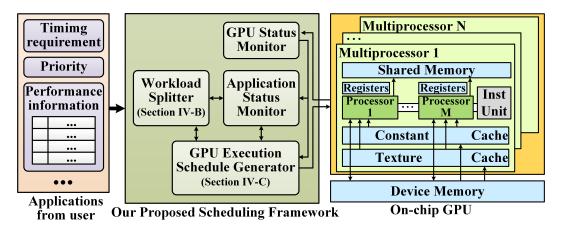

| 5.1  | Overview of the Proposed Run-time Scheduling Framework on a GPU-based            |    |

|      | Embedded System                                                                  | 75 |

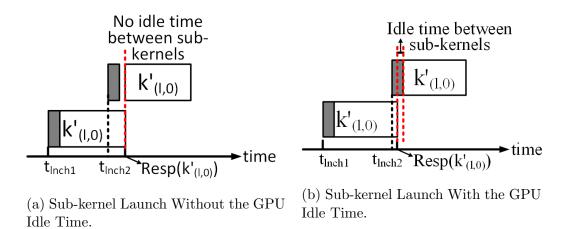

| 5.2  | Examples for Launching Sub-kernels                                               | 85 |

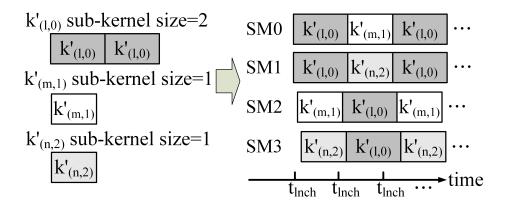

| 5.3  | Example Sub-kernel Launches on the GPU Execution Schedule Generator              | 86 |

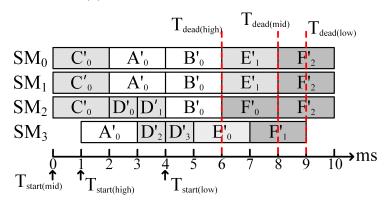

| 5.4  | Complete Working Example of the Proposed Scheduling Framework                    | 88 |

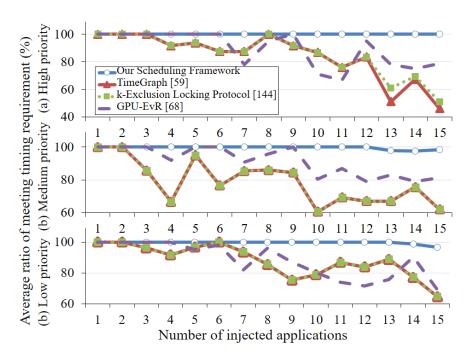

| 5.5  | Number of Applications Which Meet Deadlines Compared to [59], [144], and         |    |

|      | [68]                                                                             | 93 |

| 5.6  | Priority Distribution of the Applications Which Meet Deadlines Compared to       |    |

|      | [59], [144], and $[68]$                                                          | 95 |

| 5.7  | Average Total Timing Violation Compared to [59], [144], and [68]                 | 96 |

| 5.8  | Scalability Comparison of Our Scheduling Framework Compared to [59], [144],      |    |

|      | and [68]                                                                         | 97 |

| 5.9  | Priority Distribution Which Meet Deadlines During Scalability Analysis Com-      |    |

|      | pared to [59], [144], and [68]                                                   | 98 |

### LIST OF TABLES

|            |                                                | Page |

|------------|------------------------------------------------|------|

| 3.1<br>3.2 | Our Algorithm Execution Time                   |      |

|            | GPGPU-Sim Configuration for NVIDIA's Tegra TK1 |      |

|            | Rodinia Benchmark Suite [18]                   |      |

## LIST OF ALGORITHMS

|             |                                                | Page            |

|-------------|------------------------------------------------|-----------------|

| 1 2         | Algorithm for Computing Vulnerable Period      |                 |

| 3<br>4<br>5 | Aging-Aware Cluster Formation                  | . 62            |

| 6<br>7<br>8 | Algorithm to Split the Application Kernels     | els. 83<br>. 84 |

| 9           | Algorithm for GPU Execution Schedule Generator | . 81            |

### LIST OF ABBREVIATIONS

ADAS Advanced Driving Assistance Systems

**APIs** Application Programming Interfaces

AVF Architectural Vulnerability Factor

CMPs Chip Multi-Processors

CR Capacity Rate

CUDA Compute Unified Device Architecture

**DMR** Dual-Modular Redundancy

**DVFS** Dynamic Voltage and Frequency Scaling

**GPU** Graphics Processing Unit

**HCI** Hot Carrier Injection

ILP Instruction Level Parallelism

**ILV** Instruction-Level Vulnerability

IVI Instruction Vulnerability Index

**JIT** Just-In-Time

JLSP Job-Level Static-Priority

MEBF Mean Executions Between Failures

MPSoC Multiprocessor System-on-a-Chip

**NBTI** Negative Bias Temperature Instability

**NoC** Network-on-Chip

**PSO** Particle Swarm Optimization

**QoS** Quality of Service

RMT Redundant Multithreading

RTL Register Transfer Level

SFU Special Functional Unit

SM Streaming Multiprocessor

**SMT** Simultaneous Multithreading

**SP** Stream Processor

### ACKNOWLEDGMENTS

It has been a long and wonderful journey to pursue the doctorate degree during the past five years, and life would have been much more difficult without the support from my professors, family, colleagues and friends. Thus, I would like to take this opportunity to thank these great people for encouraging and inspiring me in this journey.

First and foremost, I would like to gratefully and sincerely thank my advisor, Professor Mohammad A. Al Faruque, for his guidance, motivation, understanding and patience during my graduate study at UC Irvine. It has been a great learning experience to be a member of his research group and a teaching assistant of his class. His considerable insights, kind personality and sense of humor created an enjoyable and pleasant working environment in our group. Thanks to this, I have learned much more from our meetings and conversations in the past few years, not only on researching and teaching, but also on life and philosophy. This is a treasure that will benefit me for a whole lifetime.

Next, I would like to thank Professor Fadi Kurdahi and Pai H. Chou, for taking time out of their busy schedules to serve as my committee members and provide me constructive suggestions and feedback on my dissertation.

Many thanks to my colleagues in the Advanced Integrated Cyber-Physical Systems (AICPS) group, including Jiang Wan, Korosh Vatanparvar, Sujit Rokka Chhetri, Sina Faezi, Anthony B. Lopez, and Xiaohong Li, for the fruitful talks, discussions and teamwork. I appreciate all their help during my graduate program.

I would like to express my appreciation to my parents, Eunyoung Lee and Hunam Jeon, for their unconditional love and endless faith in me. Their support is the very source of power and morale for me to pursue my dream.

Also, I can never forget my parents-in-law Seohyang Kim, who I am always grateful for her generous inspiration and their firm believe in me.

Last but not least, I would like to express my deepest gratitude to my family. My best friend and wife Jiyoun Kim, her encouragement, dedication and love during my PhD years was in the end what made this dissertation possible. John Seungju Lee, my baby boy, who has been the light of my life for the last two years and who has given me the extra strength and motivation to get things done.

### **CURRICULUM VITAE**

### Haeseung Lee

#### **EDUCATION**

Doctor of Philosophy in Computer Engineering 2017 University of California, Irvine Irvine, California Master of Science in Electrical Engineering 2013 Arizona State University Tempe, Arizona Master of Science in Computer Engineering 2009 Seoul, South Korea Chung-Ang University Bachelor of Engineering in Electrical and Electronics Engineering 2004 Chung-Ang University Seoul, South Korea

#### RESEARCH EXPERIENCE

Graduate Research Assistant2013–2017University of California, IrvineIrvine, CaliforniaGraduate Research Assistant2011–2013Arizona State UniversityTempe, Arizona

#### TEACHING EXPERIENCE

Teaching Assistant 2014–2017 University of California, Irvine Irvine, California

#### REFEREED JOURNAL PUBLICATIONS

## Run-time Scheduling Framework for Event-driven Applications on a GPU-based Embedded System

2016

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 35, no. 12, pp. 1956-1967, March 2016.

### GPU Architecture Aware Instruction Scheduling for Improving Soft-error Reliability

2017

IEEE Transactions on Multi-Scale Computing Systems (TMSCS), vol. 3, no. 2, pp. 86-99, February 2017.

## Aging-aware Workload Management on Embedded GPU Under Process Variation

2017

IEEE Transactions on Computers (TC) (Under submission)

#### REFEREED CONFERENCE PUBLICATIONS

## GPU-EvR: Run-time Event Based Real-time Scheduling Framework on GPGPU Platform

Apr 2014

IEEE/ACM Design Automation and Test in Europe (DATE), Dresden, 2014, pp. 1-6.

### PAIS: Parallelization Aware Instruction Scheduling for Improving Soft-error Reliability of GPU-based Systems

Mar 2016

IEEE/ACM Design Automation and Test in Europe (DATE), Dresden, 2016, pp. 1568-1573.

## Low-overhead Aging-aware Resource Management on Embedded GPUs

Jun 2017

ACM/IEEE Design Automation Conference (DAC), Austin, TX, USA, 2017, pp. 1-6.

### ABSTRACT OF THE DISSERTATION

Reliability and Timing Aware GPU Management on Embedded Systems

By

### Haeseung Lee

Doctor of Philosophy in Computer Engineering

University of California, Irvine, 2017

Professor Mohammad Al Faruque, Chair

The demand for low-power and high-performance computing has been driving the semiconductor industry for decades. In order to satisfy these demands, the semiconductor technology has been scaled down and multi/many-core processors have been proposed. Among the multi/many-core processors, Graphics Processing Units (GPUs) have been employed in the critical path of applications due to its programmability, high-performance, and low power consumption. Moreover, state-of-the-art GPUs have the capability to process multiple GPU workloads concurrently. Therefore, GPUs have been considered to be an essential part of embedded systems because of the increased number of throughput-oriented applications on real-time embedded systems, such as autonomous driving and advanced driving assistant applications. However, there are several challenges for using the GPUs in embedded systems. First, due to the small feature size, the state-of-the-art nano-scale multi-core processors, including GPUs, has faced severe reliability challenges like soft-error and processor degradation. Next, there is a noticeable (die-to-die and within-die) parameter variation due to the advanced semiconductor technology. Therefore, the lifetime and workload management of embedded GPUs under process variation is considered one of the most important aspects to ensure functional correctness over a long period of time. Last, existing application scheduling frameworks on a GPU do not have enough flexibility to handle the dynamic behavior of multiple event-driven applications.

In order to tackle the above mentioned challenges, in this thesis, we propose a reliability and timing aware workload management framework on GPU-based real-time embedded systems. The proposed framework consists of two parts: design-time and run-time workload management. The proposed design-time workload management unit analyzes GPU kernel functions and generates PTX instruction schedules that maximizes the soft-error reliability. At the same time, the application profiles are generated for run-time workload management. The proposed run-time workload management unit includes two parts: Streaming Multiprocessor (SM) scheduling unit and aging-aware workload distribution unit. During run-time, depending on the system status and requirements, the proposed scheduling unit partitions the GPU workloads into sub-workload and generates sub-workloads launch sequences to handle the dynamic behavior of the event-driven applications. Concurrently, in the SM, the proposed aging-aware workload distribution unit jointly considers the current aging status and the process variation status and distributes the workload across the SM to maximize the lifetime of the GPU.

## Chapter 1

### Introduction

### 1.1 Introduction

In recent years, embedded systems demand higher computational power, and need to respond to many random external and internal events. The number of throughput-oriented applications in the embedded systems keeps increasing [29, 34, 53, 76, 79, 106, 136, 142]. To satisfy these demands for low-power and high-performance computing, semiconductor industries have done extensive technology scaling and have proposed various multi/many-core processor architectures. Among these multi/many-core processors, Graphics Processing Units (GPUs) have been considered and employed in the critical path of applications in embedded systems due to their programmability, high-performance, and low power consumption [11, 13, 43, 68, 76, 78, 85, 105, 112, 118, 146]. In addition to the previously mentioned advantages, CPUs and GPUs, in GPU based embedded systems, share the same memory which results in a near-zero data transfer latency [76].

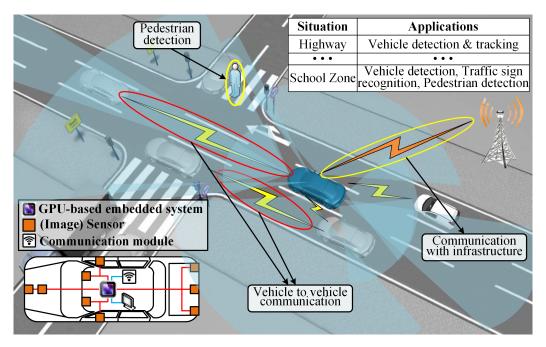

Figure 1.1 shows an example of a real-world GPU-based embedded system. The figure provides the abstract diagram of an *intelligent driving assistance system*, which is similar

Figure 1.1: Intelligent Driving Assistance System Similar to Audi A7's Auto Pilot System Utilizing GPU-based Embedded System [95].

to the Audi A7's auto pilot system, on a GPU-based embedded system (a Tegra mobile embedded system from Nvidia) [95]. In Figure 1.1, each box represents one (image) sensor and the shaded area represents the coverage of each (image) sensor. These sensors monitor the vehicle's surroundings. Each sensor detects different objects, for example, sensors near the windshield read traffic signs and sensors in the front detect pedestrians. Meanwhile, the vehicle is connected to the vehicular network (e.g. vehicle to vehicle communication network) through various communication modules.

While driving, a mixture of safety critical and non-safety applications is launched by the system depending on the current system status. For example, when driving on a highway, the system would launch a set of safety critical and high priority applications for *vehicle detection*. On the other hand, when driving in a school area, the system would launch a different set of safety critical and high priority applications for *pedestrian detection* and *traffic sign recognition*. At the same time, non-safety critical and low priority applications may be running on the system.

However, there are several challenges for using the GPU-based embedded systems. First, in embedded systems, each application would have a different priority and deadline depending on the current system status. Note that in this type of embedded system, small timing violations may cause degradation in *Quality of Service* (QoS), such as glitches in an instance of a traffic sign image. Therefore, the system is a soft real-time system and the QoS of the system highly depends on the status of safety critical and high priority applications. However, existing application scheduling frameworks on a GPU do not have enough flexibility to handle the dynamic behavior of the event-driven applications. This is because in the existing scheduling frameworks: 1) only temporal preemption is considered and 2) one application occupies the GPU at a time.

Second, due to the small feature size, the state-of-the-art nano-scale multi-core processors, including GPUs, have faced several reliability challenges such as soft-error [16, 19, 38, 40, 74, 120, 129, 130], aging effects [14, 19, 20, 37, 61, 84, 102, 137], and (die-to-die and with-in-die) parameter variation [1, 4, 57, 64, 101, 110, 119, 132]. The real-world GPUs are susceptible to the soft-errors even under normal conditions [24, 40, 90, 98]. The probability that the softerror occurs on a single hardware component is proportional to the time that the hardware component is used [143]. The soft-error reliability of the GPU is important because the GPUbased system handles most of its computation by using the GPU. In other words, if the GPU produces incorrect results, the entire system may behave incorrectly. In order to improve the soft-error reliability of the GPU, many methodologies have been proposed [32, 55, 73, 135, 139. However, instruction scheduling has not been considered for improving the softerror reliability of the GPU. Negative Bias Temperature Instability (NBTI) and Hot Carrier Injection (HCI) are considered among the most critical aging-related reliability challenges in nano-scaled semiconductors [14, 19, 20, 37, 61, 84, 102, 137]. The amount of transistor degradation caused by NBTI and HCI is proportional to the time a transistor is stressed or switched [19, 75, 88, 103]. Various workload management techniques have been proposed to balance the stress level across the chip to minimize NBTI and HCI effect. To alleviate the effects of process variation, typically, multi-core processors have employed a chip-level guardbanding technique, which operates at the lowest frequency. However, the state-of-the-art multi-core processors uses a core-level guardbanding technique, which applies different frequencies for each core, to further improve the overall performance. Due to the core-level guardbanding technique, each core of a single-chip would have different operating frequency and duty cycle, which leads to varying stress levels and thermal variations across the chip. These stress/thermal variations likely introduce randomness in the system state. The existing workload management techniques have a limitation in minimizing the aging effect with the core-level guardbanding technique. Especially, with the core-level guardbanding technique, the GPU randomly distributes the instructions to its cores. This is due to the asynchronous behavior of the components in the GPU.

In summary, the state-of-the-art GPU-based embedded systems suffer from the following challenges:

- Existing application scheduling frameworks on a GPU do not have enough flexibility to handle the dynamic behavior of the event-driven applications.

- Due to the small feature size, the semiconductor technology has faced severe reliability challenges like soft-error and processor degradation. The soft-error has been improved by using various methodologies such as redundancy methodologies. However, the GPU compiler has yet to be considered for improving the soft-error reliability of the GPU.

- A noticeable within-die parameter variation and core-level guardbanding technique increase the randomness of the system state. Therefore, existing aging management techniques have a limitation in maximizing the lifetime of embedded GPUs in the presence of the parameter variation.

### 1.2 Motivational Case Studies

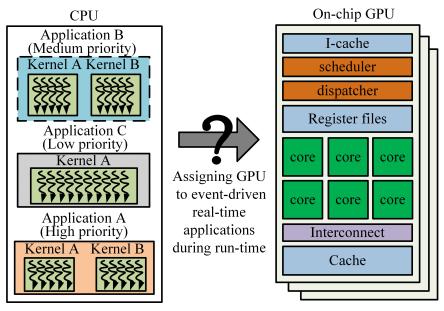

In order to highlight the above mentioned challenges, we perform several case studies on real-world applications. Figure 1.2 illustrates a scenario where multiple applications, with different priorities, are executed on the target GPU-based embedded system. Figure 1.2a describes the abstract behavior of the target system while Figure 1.2b provides the information about the input applications. Since the current GPU processes the workloads sequentially, the response time of each application heavily depends on the arrival time. In our example, the high priority application A starts executing after the lower priority applications B and C have completed. Note that application A does not meet its deadline. However, application A could meet its deadline if the target GPU-based embedded system may be capable of generating schedules during run-time, in addition to supporting preemption.

Note that after the host launches a kernel function, only the GPU can control the kernel behavior [92]. In other words, due to the limitation of the GPU hardware, the GPU does not allow the reallocation of the GPU resources for ongoing kernels. Therefore, the host can either wait for the completion of the kernel, or alternatively, launch another kernel. However, typically, a kernel is a collection of thousands of identical GPU threads and the host partitions a kernel based on the configuration. After submitting an entire kernel to the GPU, it is possible that some part of the kernel is running on the GPU and the other part of the kernel is waiting on the GPU hardware queue. Therefore, when partitioning a GPU kernel in the host, an opportunity arises to reallocate the GPU resources and implement both temporal and spatial preemption on a GPU-based embedded system.

In order to see the feasibility of multiple sub-kernel launches, we measured the average performance overhead for an empty kernel launch while using two different GPUs (Nvidia GTX660 and Tegra K1). Figure 1.3a shows the source code while Figure 1.3b shows the corresponding observational results. According to Figure 1.3b, the average empty kernel

(a) Target GPU-based Embedded System.

| App | Prio. | Arr. time         | deadline          | Exec. time | Cmpl. time        |

|-----|-------|-------------------|-------------------|------------|-------------------|

| A   | High  | $2.5 \mathrm{ms}$ | 4.2ms             | 1.5ms      | $6.5 \mathrm{ms}$ |

| В   | Mid   | $1 \mathrm{ms}$   | $3.5 \mathrm{ms}$ | 2ms        | $3 \mathrm{ms}$   |

| С   | Low   | $2 \mathrm{ms}$   | $6.5 \mathrm{ms}$ | 2ms        | $5 \mathrm{ms}$   |

(b) Input Event-driven Application Information.

Figure 1.2: Motivational Example Scenario on the GPU-based Embedded System.

launch overheads for GTX660 and Tegra K1 are  $12\mu s$  and  $64\mu s$ , respectively.

The example scenario shown in Figure 1.2 indicates that the GPU needs to be efficiently assigned and provide preemption capabilities, in order to meet the deadlines of the applications. Moreover, the results in Figure 1.3 imply that the performance overhead of launching multiple sub-kernels may be relatively small compared to the execution time, of the kernel, within a single launch. The following capabilities are what make our groundbreaking approach possible; 1) partitioning application kernels into multiple sub-kernels in order to represent the GPU resources (re)allocation and 2) launching the sub-kernels with the objective of assigning more GPU cores to higher priority applications in order to apply the GPU resources (re)allocation.

```

1 __global__ void empty_kernel(input) {;}

3 int main()

4 {

0.07

Average kernel launch

// Time measure start

0.06

0.05

0.04

0.03

-GTX 660

for (int i=0; i<repeat; i++) {</pre>

--Tegra K1

GTX 660

Tegra K1

// launch empty kernel

9

Average (ms)

0.012386

0.064121

\( \frac{1}{6} \) 0.02 \( 0.01 \)

empty_kernel <<<grid, block>>>(input);

10

// wait until empty kernel finish

11

cudaDeviceSynchronize();

12

121

13

Number of threads

14

// Time measure end

15

(b) Instruction Distribution with Process

Variation.

16

// Take the average and cleanup

17

18 }

```

(a) Part of Source Code for Measuring Kernel Launch Overhead.

Figure 1.3: Kernel Launch Overhead for Varying Number of Threads.

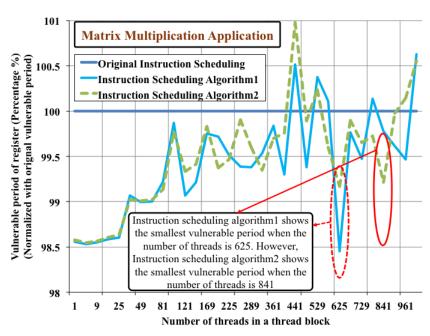

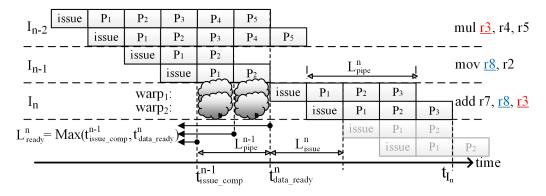

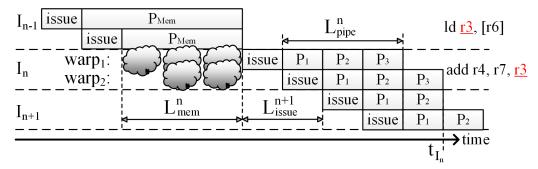

In order to observe how the instruction scheduling affects the soft-error reliability, we have created a total of three matrix multiplications by modifying its instruction schedule. The vulnerable period is the metric to measure the soft-error reliability of a GPU application [55, 86] (see Section 3.2 for more details). The vulnerable period is the time from the moment that the data is produced until the last moment that the data is consumed [86]. We then measured the vulnerable period of these three matrix multiplication applications by using the GPGPU-Sim [8] simulator and show the experimental results in Figure 1.4. Below we provide some observations of these experimental results.

The total amount of the vulnerable period is not proportional to the number of threads in a thread block. The vulnerable periods vary depending on the number of threads in a thread block.

Figure 1.4: Motivational Example to Illustrate the Relation Between Vulnerable Period and Instruction Schedule.

In addition, there is no instruction schedule that always shows the minimum vulnerable period. For example, *Scheduling Algorithm 1* shows the smallest vulnerable period when the number of threads is 625. However, when the number of threads is 841, *Scheduling Algorithm 2* shows the smallest vulnerable period.

These experimental results indicate that the vulnerable period of an application does not only depend on the instruction scheduling but also on the parallel behavior of the GPU. The result may show a small amount of change in the vulnerable period. This is because of the simple kernel function and a small number of threads. However, the result in Figure 1 still shows the possibility that the vulnerable period, which is related to the soft-error reliability, may be improved through the instruction scheduling. Therefore, the parallel behavior of the GPU and the instruction scheduling need to be considered together to further improve the soft-error reliability.

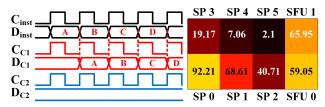

Figure 1.5 provides example case studies to show how the process variation and core-level guardbanding affect the workload distribution on the GPU. Figure 1.5(a) describes the sim-

- (a) Instruction Distribution without Process Variation.

- (b) Instruction Distribution with Process Variation.

Figure 1.5: Example Behavior of the Existing Warp Scheduler and Instruction Dispatcher with/without Process Variation.

plified behavior of the instruction dispatcher and two clusters (C1 and C2) without the process variation and core-level guardbanding. Without the core-level guardbanding, all the clock signals ( $C_{inst}$ ,  $C_{C1}$ , and  $C_{C2}$ ) are synchronized and four instructions (A, B, C, and D) are sent to the cluster 1, C1. The cluster 2, C2, will get the instructions after the cluster 1's pipeline is full. However, with the core-level guardbanding, the instruction dispatcher and the clusters show different behavior. As described in Figure 1.5(b), each component has a different operating frequency due to the core-level guardbanding. Besides, because of the asynchronous behavior, each cluster gets two instructions. The instructions A and D are assigned to the C1 and the instructions B and C are assigned to the C2. The example in Figure 1.5 implies that the process variation and the core-level guardbanding cause some degree of workload distribution. However, as shown in Figure 1.5(b), the workload is not evenly distributed because C1 and C2 have different operating frequencies.

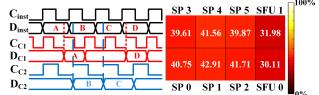

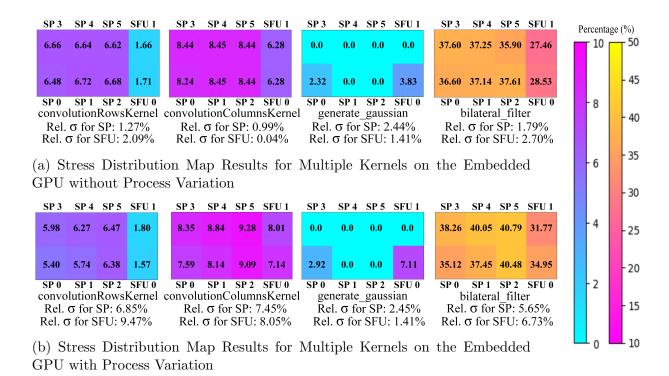

In order to demonstrate the aforementioned unbalanced workload distribution with the process variation and core-level guardbanding, we perform experiments with real world applications. In state-of-the-art embedded GPUs, such as NVIDIA's Tegra TK1, multiple instructions are issued in a single clock cycle. Each instruction represents the behavior of 32 threads which is handled by the cluster of 32 cores and called warp. This warp is the basic execution unit of NVIDIA's GPU. However, due to the process variation and cluster-level guard banding, the stress is not evenly distributed across the GPU even though each cluster processes the same number of instructions. We use the GPGPU-Sim simulator [8],

Figure 1.6: Simulation Results to Show the Effect of the Process Variation on Embedded GPUs.

which is a configurable cycle-level GPU architectural simulator. We configured the GPGPU-Sim to have a similar configuration with the GPU in NVIDIA's Tegra TK1 (1 Streaming Multiprocessor, 192 CUDA cores, etc.) and executed the following benchmark applications: bilateral filter and 2D convolution. In GPGPU-Sim, each Stream Processor (SP) and Special Functional Unit (SFU) handles the execution of a single warp. The SP and SFU units are mapped into a process variation map that is generated in [38, 120].

During the experiments, we evenly distributed the instructions to the SP and SFU units. Then, the pipeline status of the SP and the SFU units are collected to generate a stress (workload) distribution map for each benchmark application with/without the process variation. Figure 1.6 shows experimental results for various GPU kernel functions. Figure 1.6(a) shows the stress map results when all the SP and SFU units operate with the same frequency. The stress map and the standard deviation imply that the stress is evenly distributed across the GPU. On the other hand, after considering the process variation and cluster-level guard-

bandinf technique, the stress is not evenly distributed. Figure 1.6(b) shows the stress map and standard deviation results with the process variation. The stress map shows that each SP and SFU unit has a different amount of stress while processing the same number of instructions. In addition, the standard deviation of stress for the SP and SFU units is increased by 4.3 and 52.3 times in average, respectively. The results indicate that that current warp schedulers and instruction dispatchers have a limitation in minimizing the NBTI and HCI effects under the process variation. Therefore, there is a need for a fine-grained workload management technique that reconfigures the cluster of cores and distributes the workload to minimize the NBTI and HCI effects on the embedded GPUs under the process variation.

### 1.3 Contributions

### 1.3.1 Problem and Research Challenges

The above mentioned problems for GPU-based embedded systems poses the following research challenges:

- How to partition GPU kernels into multiple sub-kernels during run-time, such that

multiple application kernels could concurrently occupy the GPU, where the number of

the applications that meet their deadline is maximized.

- Estimation of the soft-error of GPU applications by considering the accurate GPU execution model and Generation of the instruction schedule in order to maximize the soft-error reliability of a GPU application during design-time.

- Due to the variation in degradation and core-level guard banding, the process variation aware cluster (warp) formation is required. In addition, the warp scheduler and the

instruction dispatcher should balance the workload distribution across the GPU by considering the degradation levels and process variation together.

### 1.3.2 Our Novel Contributions

In order to address the above mentioned challenges, we propose a reliability and timing aware workload management framework which includes:

- A GPU architecture-aware instruction scheduling algorithm (Section 3) that maximizes the soft-error reliability of a GPU application during design-time by considering the impact of the parallel behavior of the GPU.

- A timing-aware workload scheduling framework (Section 5) which partitions the GPU kernel into multiple sub-kernels during run-time in order to implement spatial preemption. Depending on the current status of the target GPU-based embedded system and the application priority, the proposed workload splitter decides the number of sub-kernels and the size of each sub-kernel.

- A aging-aware workload distribution unit (Section 4) that generates core cluster information based on the current NBTI and HCI information during run-time. After that, the proposed workload distribution unit is configured based on the above mentioned information. The instructions are distributed based on the instruction distribution ratio to minimize the aging effects under the process variation.

The rest of this dissertation is organized as follows: Chapter 2 discusses related works. Chapter 3 explains the design-time part of the proposed framework. Chapter 5 and 4 discuss the run-time part of the proposed framework. Chapter 5 provides a discussion on the proposed flexible run-time workload scheduling. Chapter 4 gives an explanation for the proposed

aging-aware workload distribution under the process variation. Finally, Chapter 6 concludes the dissertation.

## Chapter 2

### Related Works

A large body of research aims to maximize the lifetime of embedded GPUs while increasing the flexibility on workload scheduling. Research has been conducted to improve the soft-error reliability of the processors including GPUs [32, 39, 54, 73, 111, 121, 128, 135, 139]. Some research works have shown the impact of soft-errors by using radioactive sources [97, 133]. However, usage of these radioactive sources is difficult and not for the general purpose applications, therefore some research works have focused on the technique to model the soft-error behavior [6, 49, 62] and evaluate the soft-error resiliency of an application [31, 45, 86, 97, 122, 133]. Research works have proposed to detect the occurrence of the soft-errors and ensure the correctness of an application by using various techniques (i.e. redundant execution [54, 121, 128, 135, 139], insertion of protection code [32, 73], and leveraging architectural characteristics [39, 111]). In the rest of this section, we discuss in detail the above mentioned research works.

Various research works have been conducted to demonstrate the impact of soft-error and evaluate the soft-error resilience of the GPU application [31, 45, 86, 97, 122, 133]. One research [86] proposed a metric to quantify the soft-error reliability based on the detailed

timing behavior of an application. Other research works [97] and [133] showed the impact of the radiation-induced soft-error on the NVIDIA's GPU. In order to inject the actual soft-error into the GPU, the target system is exposed to the neutron beam. Another research in [117] has evaluated the soft-error resilience of several safety-critical applications. An embedded GPGPU platform has been exposed to neutron flux in order to measure the soft-error resilience. A soft-error estimation framework is proposed in order to accurately estimate the soft-error rate, work in [45]. Unlike the traditional netlist-based technique, the proposed framework estimated the soft-error rate from the layout of the target processor. The impact of soft-error reliability has been discussed in [31] and [122]. Various techniques (i.e. debugger based fault injection) are used to show the impact of soft-error reliability of the GPU. These research works have successfully demonstrated the impact of soft-error in real-world environment and applications. However, these works do not propose the technique to improve the soft-error reliability.

Research has been conducted to model the soft-error behavior. One research in [6] has proposed a soft-error model to provide the failure probability of various interleaving techniques for the SRAM. Other research in [49] has discussed about the soft-error model for 25nm technology. Another research in [62] has proposed a cross layer analysis approach for modeling the soft-error behavior on the FinFET transistors. The proposed approach performs 3D simulations from the interactions in FinFET structures up to circuit level. A soft-error susceptibility estimation technique has been proposed in [83]. The proposed technique uses symbolic modeling to estimate the soft-error susceptibility of a combinational logic circuit. However, since the detailed GPU architecture is not available to the research community, the research works are not applicable.

Research has been conducted to provide the soft-error injection tools because it is extremely difficult to perform the experiment in a radiation environment [30, 72]. One research in [72] has proposed a soft-error injection tool that injects a single bit-flip into the data object in the

binary. Other research in [30] has proposed a soft-error injection technique that randomly selects the instruction and changes its result. However, these research works have limitations in modeling the random behavior of soft-error. For instance, although not all the injected soft-errors cause bit-flips, these research works inject a bit-flip whenever the soft-error occurs.

Research has been conducted in order to find the incorrect behavior and ensure the functional correctness [54, 77, 121, 128, 135, 139]. One research in [77] has proposed an application framework to handle the soft-errors on GPU DRAM. The DRAM errors in GPUs are detected by using the dual parity technique and the application is recovered from the checkpoints. Other research in [139] has proposed a software level Dual-Modular Redundancy (DMR) technique. Each stage has a monitor function and its result is compared to the result from that monitor function. Another research in [54] has proposed a redundant technique that utilizes the GPU idle time caused by the branch divergence. A duplication technique proposed in [121] has redundant execution for the critical parts of the GPU pipeline and recomputes erroneous results when error is detected. A redundant execution methodology is proposed in [128] and it uses the idle time of the GPU in order to minimize the performance overhead. An automatic Redundant Multithreading (RMT) technique is proposed in [135]. The proposed technique modifies an application's code during compile-time to add redundant execution. However, these works may cause a significant amount of performance and power overhead, because the proposed techniques are based on redundant execution or recomputation.

Research has also been conducted to improve the soft-error reliability by leveraging the parallel behavior of the GPU [39, 111]. It is shown in [39] that the GPU's soft-error reliability is affected by its parallel behavior. For example, one research in [111] has demonstrated that the Mean Executions Between Failures (MEBF) of a GPGPU application is affected by the parallel behavior of the GPU. In order to show the relationship between the MEBF and the parallel behavior of the GPU, the *grid* and the *block size* of a GPGPU application is modified. However, these research works do not provide the techniques to find the *grid* and

the block size and improve the soft-error reliability of the GPU.

Various instruction scheduling algorithms have been proposed to improve the soft-error reliability [114, 115, 116]. One research project in [115] has proposed a metric to quantify the soft-error reliability by using both the detailed timing behavior of the application and the hardware information. Based on the proposed metric, an instruction schedule is generated to maximize the soft-error reliability. Other research in [114] has proposed an instruction schedule algorithm to maximize the soft-error reliability under various performance constraints. Another research in [116] has proposed an instruction schedule to maximize the soft-error reliability for a specific component. Based on the compiler option, the proposed instruction scheduling algorithm maximizes the soft-error reliability of the selected components. For example, if the compiler option selects the register file, then the proposed instruction generates an instruction schedule that maximizes the soft-error reliability of the register file. However, since these instruction scheduling algorithms are based on RISC processors such as SPARC-V8 architecture, they are not applicable to the GPU. In addition, due to the fact that the probability of the soft-error occurrence is proportional to the time that the hardware component is used, the performance-aware instruction scheduling may be considered to improve the soft-error reliability [52]. However, since the performance-aware instruction scheduling focuses on maximizing the GPU resource utilization, improvement in the soft-error reliability is limited.

Research has been conducted for detection and protection of the vulnerable parts in GPGPU applications [21, 32, 73, 100]. One research in [32] has proposed the checker functions that are inserted to protect the potentially vulnerable parts of a GPGPU application. Other research in [100] has proposed a compilation technique that improved the control-flow reliability. Another research in [73] has proposed a compile-time methodology that protects the memory access instructions by inserting checker instructions. One study in [21] has proposed an application-level technique that modifies the loop code during the compile-time. However,

these works have limitations in improving the soft-error reliability of the GPU because the soft-error may occur in any part of a GPGPU application.

A large body of research aims to minimize the effects of NBTI and HCI on multi/many-core systems. The work in [42] surveys various trade-off points between power, performance and reliability in multi/many-core systems-on-chip. The surveys show that there are multiple control knobs to optimize power, performance, and reliability of multi/many-core systems.

A task migration technique [9] is proposed to minimize the effect of NBTI. The proposed technique uses the spare processor in order to migrate tasks from the near-to-die primary processor to the young processor. However, this technique is not applicable to the GPUs because they do not have spare cores. A circuit design technique is proposed to minimize the amount of NBTI-induced clock skew [17]. A Network-on-Chip (NoC) router architecture was proposed to increase the lifetime of the NoC-based general purpose Chip Multi-Processors (CMPs) [63]. The proposed architecture optimizes the duty cycle of the NoC during its idle time. Whenever the NoC router does not have any packet to process, the proposed exercise module operates and optimizes the duty cycle as much as possible. However, the proposed architecture is not applicable to the GPUs because it is tailored to the NoC-based general purpose CMPs and has a considerable amount of area/power overhead that restricts its application to GPUs which have many small cores. The work in [3] has proposed a dynamic routing algorithm for heterogeneous NoC architectures to overcome the NBTI-induced performance degradation. Based on the NBTI information of each router, the routing path is generated to minimize the performance degradation.

Task allocation techniques are proposed to minimize the impact of NBTI degradation on heterogeneous multi-core processors [103, 126]. The proposed techniques assign the application's function to processors based on the application information and the current NBTI status. However, unlike existing NoC-based multi-core architectures, the computational cores in the GPU form clusters of cores and share the instructions. Therefore, the afore-mentioned works

are not scalable to embedded GPUs. The concept of Capacity Rate (CR) [125] has been proposed to indicate whether a core is able to accept the workload or not. The proposed CR is estimated based on the critical path delay and the power consumption status of the core. Based on the estimated CR, tasks are assigned to the cores to balance workloads while minimizing communication overhead. However, since there is no direct communication between the cores in the GPUs, the proposed technique is not suitable. The work in [15] shows that the power gating technique can be used to reduce the NBTI effect. Using the power gating and several circuit models, the work shows that the power gating may allow synthesizing low-leakage circuits with maximum lifetime. However, this work does not discuss how the power gating should work with complex multi-core architectures to minimize the NBTI effect. An analytical model [47] has been proposed to estimate the lifetime of Multiprocessor System-on-a-Chip (MPSoC). Based on the proposed analytical model, a mapping between the tasks and the processors are generated. However, the proposed model aims for the MP-SoC platform, thus it is not scalable to the GPUs. An on-chip NBTI degradation sensor is proposed in [60]. The proposed sensor uses a delay-locked loop to measure the threshold voltage in a PMOS transistor. However, there is no discussion on how to maximize the lifetime of the GPUs.

Research has been conducted to control the behavior of processors under the process variation. A thread-to-core mapping technique is proposed in [120] to maximize the performance of a many-core processor. During run-time, the proposed technique dynamically generates thread-to-core mappings based on the current thermal and power profile. The work in [38] has proposed a thread-to-core mapping technique to mitigate the aging effect on many-core processors under the process variation. The proposed technique generates an aging prediction map based on the power consumption pattern and the process variation. A scheduling algorithm [46] is proposed to maximize the performance of MPSoC-based systems under the process variation. The proposed scheduling algorithm considers the spatial correlation between the processors to minimize the effect of the process variation. A run-time workload

distribution technique [104] has been proposed to minimize the effect of the process variation. It employs a scheduling policy that uses a linear programming and a bin-packing formulation together. A variation-aware task mapping algorithm for MPSoC is proposed in [82] that assigns the execution time of each core. However, given that the above mentioned techniques aim for Network-on-Chip (NoC) based multi/many-core platforms, they are not scalable to the GPUs. A frequency assignment technique has been proposed in [2] to maximize the performance of GPUs under process variation. The proposed technique assigns different frequencies for each SM core. After this step, SMs are assigned to applications based on their workload profile. The work in [81] has proposed a technique to minimize the effect of process variation on a processor. The proposed technique controls the mapping between tasks and cores based on the aging status and implements per-core Dynamic Voltage and Frequency Scaling (DVFS) to maximize the lifetime of the processor. A notion called Instruction-Level Vulnerability (ILV) has been proposed in [109]. Through the ILV, the process variation can be exposed to the software to maximize the performance of systems. However, since the proposed ILV is tailored to RISC processors, it is not applicable to the GPUs. The work in [23] has proposed a technique to map application threads to Simultaneous Multithreading (SMT) cores under the process variation. The proposed technique utilizes the operating system and hardware performance counters to create an application profile under the process variation. After creating the profile, based on the application profile, the mapping between the application threads and the cores is generated to maximize the performance of the system. However, the application's profile based on the SMT cores is not able to capture the characteristics of the GPUs.

Research has been conducted to alleviate the aging effects on the GPUs under the process variation. A system-level technique [25] is proposed to measure the effect of NBTI on the GPU and to find the defected cores. However, since the proposed technique only detects defected cores, the proposed technique does not control workload distribution and maximize the lifetime of the GPU. In order to minimize the NBTI effect on the warp scheduler in a

GPU, the work in [147] has proposed a two-stage architecture. In order to minimize the workload on the warp scheduler, the proposed two-stage architecture implements an input module that checks the warps and sends some warps which are ready to execute. An NBTI-aware register file allocation technique has been proposed in [88] that includes additional hardware to perform aging-aware register assignment. The work in [127] has proposed a technique to mitigate the effects of the NBTI and the process variation on the register file of GPUs. The proposed technique classifies the register files into two categories: fast and slow register files. After this classification, based on the application profile and NBTI status, the fast and the slow register files are assigned. However, these works do not consider the utilization of computational cores on the GPU.

To minimize the NBTI effect and maximize the lifetime of the GPU, compiler-based techniques [75, 108] have been proposed. During run-time, the Just-In-Time (JIT) compiler generates a healthy kernel function based on the current aging status of the GPU. This healthy kernel includes some additional workloads to transfer the workloads from the degraded cores to healthy cores. The amount of additional workload depends on the number of degraded cores. However, the proposed techniques require the JIT compiler support, which causes a non-negligible performance overhead, for run-time kernel compilation. Moreover, the additional workloads may cause a significant performance overhead to transfer the workloads between the degraded cores and healthy cores. An SM level clock gating technique [19] has been proposed to maximize the lifetime of the GPUs. The proposed technique finds the optimal number of SMs to handle GPU applications and controls the clock signal at SM granularity. However, in general, the embedded GPUs have few SMs [94]. Thus, the proposed technique is not scalable in this case. A technique to minimize the process variation effect on the GPU has been proposed in [70]. The proposed technique maximizes the performance of the GPUs by applying maximum frequency to each core, which may aggravate aging or disable slow cores which may result in performance loss. Overall, this technique does not consider the lifetime of the GPUs under the process variation. A workload management technique [69] is proposed to maximize the lifetime of the GPU. It assigns the instructions to different clusters based on the current aging status. However, since it does not consider the process variation, it may not improve the lifetime of the GPU in the presence of process variation.

State-of-the-art application scheduling frameworks have been proposed in order to leverage the GPU-based embedded system's performance and low power consumption. Works in [51, 67] use GPUs to improve the performance of real-time graphics applications such as 3D image reconstruction and facial detection. Work in [148] improves the IP routing performance by using GPUs. Work in [28] discusses the limitations of GPUs in the real-time applications. Works in [33, 99, 131, 145] use GPUs to process the compute-intensive part of medical imaging applications and archive real-time performance. Works in [22, 36] use GPUs to improve the performance of object tracking applications. Work in [50] proposes Application Programming Interfaces (APIs) for real-time systems in order to ease the use of GPUs. Work in [134] proposes an algorithm to distribute the large amount of data and schedule the workloads to achieve high utilization of a multi CPU-GPU platform (under real-time constraints). Work in [87] presents a real-time road sign detection framework for the Advanced Driving Assistance Systems (ADAS), where the presented framework uses the Particle Swarm Optimization (PSO) algorithm to improve the detection performance. The above mentioned research works use the GPUs to improve the performance of a single application and achieve real-time performance. However, the above mentioned works are tailored for single applications, they have limitations in handling multiple and different applications.

In order to support multiple applications on complex real-time embedded systems (such as our target GPU-based embedded system), preemption is required. To overcome this problem, various research works have been conducted. Work in [89] proposes a lowest priority first based light-weight feasibility analysis of CPU-based real-time systems. However, since the proposed work focuses on the feasibility analysis of CPU-based real-time systems, there is