# SPECIFICATION FOR TFT LCD MODULE

**CUSTOMER:**

| CUSTOME                                                                                                                                                                                                                                      | R MODULE :            |             |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------|--|--|--|--|--|

| HL MODE                                                                                                                                                                                                                                      | L: <u>HG101WU06</u> 5 | <u></u>     |  |  |  |  |  |

| ☐Preliminary Specification  ☐Final Specification                                                                                                                                                                                             |                       |             |  |  |  |  |  |

| Customer Confirmation                                                                                                                                                                                                                        | column:               |             |  |  |  |  |  |

| Approved by :                                                                                                                                                                                                                                | Dept. :               | Data :      |  |  |  |  |  |

| Please return one of the copies of the specification with your signature to us within two weeks after you receive this document. If it is not returned, we will assume that you agree to the entire contents of this specification document. |                       |             |  |  |  |  |  |

| Designed by                                                                                                                                                                                                                                  | Checked by            | Approved by |  |  |  |  |  |

Hongguang Display HG101WU065 1/23

# **Contents**

| No. | Items                     | Page |

|-----|---------------------------|------|

| 1.0 | General Description       | 3    |

| 2.0 | Absolute Maximum Ratings  | 5    |

| 3.0 | Electrical Specifications | 6    |

| 4.0 | Optical Specifications    | 13   |

| 5.0 | Reliability Test          | 17   |

| 6.0 | Packing Information       | 18   |

| 7.0 | Handling & Cautions       | 19   |

| 8.0 | Appendix                  | 22   |

Hongguang Display HG101WU065 2/23

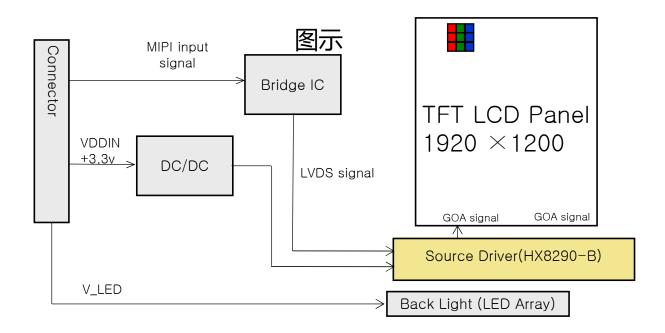

### 1.0 GENERAL DESCRIPTION

### 1.1 Introduction

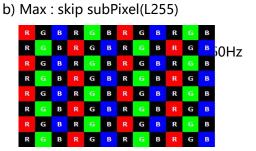

HG101WU065 is a color active matrix TFT LCD FOB using amorphous silicon TFT 's (Thin Film Transistors) as an active switching devices. This module has a 10.1 inch diagonally measured active area with WUXGA resolutions (1920 horizontal by 1200 vertical pixel array). Each pixel is divided into RED, GREEN, BLUE dots which are arranged in vertical stripe and this module can display 16.7M colors.

### 1.2 Features

- MIPI Interface;

- 8bit display 16.7M colors

- High contrast ratio and Transmittance

Hongguang Display HG101WU065 3/23

# 1.3 Application

G Industrial

# 1.4 General Specification

The followings are general specifications at the HG101WU065.

<Table 1. LCD Module Specifications>

| Parameter            | Specification                              | Unit   | Remarks  |

|----------------------|--------------------------------------------|--------|----------|

| Active Area          | 216.8064(H)*135.504(V)                     | mm     |          |

| Number Of Pixels     | 1920(H)×1200(V)                            | pixels |          |

| Pixel Pitch          | 0.03764(H)×RGB×0.11292(V)                  | mm     |          |

| Pixel Arrangement    | Pixels RGB stripe arrangement              |        |          |

| Display Mode         | Normally Black                             |        |          |

| Display Colors       | 16.7M(8bit )                               | colors |          |

| Surface Treatment    | НС                                         |        |          |

| Contrast Ratio       | 900:1(typ.)                                |        |          |

| Viewing Angle(CR>10) | 80/80/80/80(typ.)                          |        |          |

| Response Time        | 30(typ.)/35(max.)                          | ms     |          |

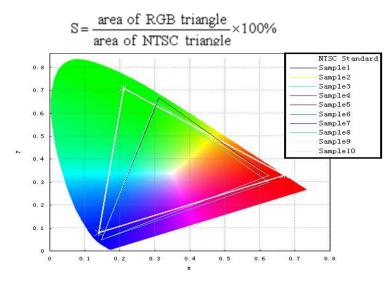

| Color Gamut          | 72%NTSC                                    |        | @BOE BLU |

| Power Consumption    | BLU:3.73(Typ.)                             | W      |          |

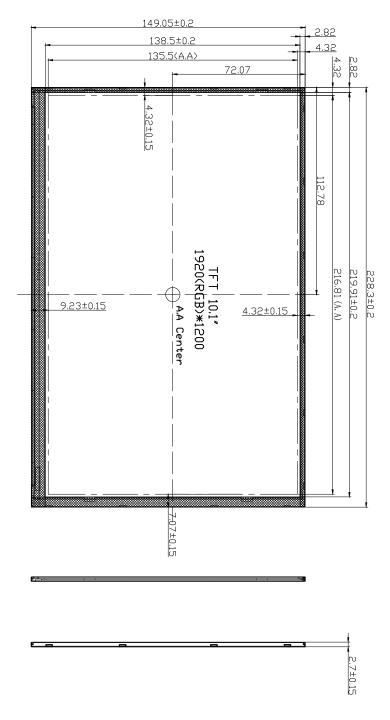

| Outline Dimension    | 228.3(H)*149.05.(V)*2.7(typ)(5.05ma<br>x.) | mm     |          |

# 2.0 ABSOLUTE MAXIMUM RATINGS

The followings are maximum values which, if exceed, may cause faulty operation or damage to the unit.

< Table 2. Absolute Maximum Ratings>

| Param                         | Parameter           |                 | Min.    | Max. | Unit | Remarks   |

|-------------------------------|---------------------|-----------------|---------|------|------|-----------|

| Power<br>Supply               | LCD<br>Module       | VDD             | VSS-0.3 | 3.6  | V    | Ta = 25 ℃ |

| Operating Te                  | mperature           | T <sub>OP</sub> | -20     | +70  | °C   |           |

| Storage Ten                   | Storage Temperature |                 | -30     | +80  | °C   |           |

| Operating Ambient<br>Humidity |                     | Нор             | 10      | 90   | %RH  |           |

| Storage Humidity              |                     | Hst             | 10      | 90   | %RH  |           |

Hongguang Display HG101WU065 5 / 23

### 3.0 ELECTRICAL SPECIFICATIONS

### 3.1 TFT LCD Module

< Table 3. LCD Module Electrical specifications >  $[Ta = 25 \pm 2 \text{ }^{\circ}\text{C}]$

| Вомом                | Parameter    |        |      | Values |      | Unit | Notes  |  |

|----------------------|--------------|--------|------|--------|------|------|--------|--|

| Parameter            |              | Symbol | Min. | Тур.   | Max. | Onit |        |  |

| Dower Cup            | nlu Valtaga  | VDD    | 3.0  | 3.3    | 3.6  | V    |        |  |

| Power Sup            | ply Voltage  | VRP    |      |        | 300  | mV   | Ripple |  |

| Power Supply Current |              | IDD    | -    | 300    | 360  | mA   | Note 1 |  |

| Power Consumption    |              | PLCD   | -    | 1      | 1.2  | W    | Note 1 |  |

| Rush                 | current      | IRUSH  | -    | -      | 3.0  | А    | Note 2 |  |

|                      | Input        | VIH    | 2.7  |        | 3.3  | V    |        |  |

| CMOS                 | CMOS Voltage | VIL    | 0    |        | 0.5  | V    |        |  |

| Interface            | Output       | VOH    | 2.7  |        | 3.3  | V    |        |  |

|                      | Voltage      | VOL    | 0    |        | 0.5  | V    |        |  |

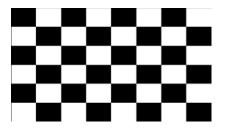

Notes : 1. The supply voltage is measured and specified at the interface connector of LCM. The current draw and power consumption specified is for VDD=3.3V, Frame rate  $f_V$  and Clock frequency = 490MHz. Test Pattern of power supply current

a) Typ: Mosaic 8 x 6 Pattern(L0/L255)

2. The duration of rush current is about 2ms and rising time of Power Input is 1ms(min)

Hongguang Display HG101WU065 6/23

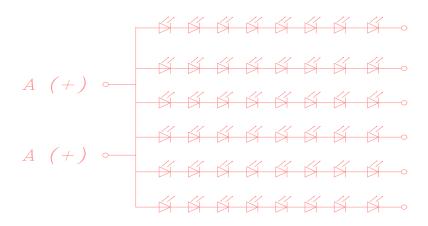

# 3.2 Back-Light Unit

Table 4. LED Driver Electrical Specifications >

| Darameter           |                | Values |      | Unit | Notes |                      |

|---------------------|----------------|--------|------|------|-------|----------------------|

| Parameter           |                | Min.   | Тур. | Max. | Onit  | Notes                |

| LED Forward Voltage | $V_{F}$        | -      | -    | 3.0  | V     | Note 1               |

| LED Forward Current | l <sub>F</sub> | -      | 22   | -    | mA    | (8pcs<br>Serial 6pcs |

| Power Consumption   | $P_{LED}$      | -      | 3.73 | -    | W     | Parallel.)           |

| LED Quantity        | -              | -      | 48   | -    | EA    |                      |

| LED Life Time       | N/A            | 15000  | -    | -    | Hrs   | IF=22mA<br>Note 2    |

If=120mA, Vf=25.6V, Lv=400cd/m2

Notes: 1. Power supply voltage25.6V for LED Driver

Calculator Value for reference IF  $\times$  VF  $\times$  48/ 85%( efficiency) = PLED

2. The LED Life-time define as the estimated time to 50% degradation of initial luminous.

Hongguang Display HG101WU065 7/23

### 3.2 INPUT TERMINAL PIN ASSIGNMENT

This LCD employs one interface connections, a 34 pin connector is used for the LCD module electronics interface.

# 3.2.1 Pin assignment for LCD module

Connector: FH34SRJ-34S-0.5SH(50) (HRS) or equivalent

# < Table4. Pin Assignment for LCD Module Connector >

| Pin No. | Symbol   | Description                        | I/O |

|---------|----------|------------------------------------|-----|

| 1       | VLEDIN   | LED POWER SUPPLY                   | Р   |

| 2       | VLEDIN   | LED POWER SUPPLY                   | Р   |

| 3       | VLEDIN   | LED POWER SUPPLY                   | Р   |

| 4       | I2C_SDA  | OTP_SDA                            | I   |

| 5       | I2C_SCL  | OTP_SCL                            | I   |

| 6       | AGING    | H,BIST;L NORMAL mode;              | I   |

| 7       | ID       | ID Pin (1.8V拉高或拉低)                 | I   |

| 8       | ADDR     | 1.8V拉高或拉低(预留)                      | I   |

| 9       | GND      | Power Ground                       | Р   |

| 10      | GND      | Power Ground                       | Р   |

| 11      | GND      | Power Ground                       | Р   |

| 12      | DSI_D3N  | MIPI data pair 3 negative signal   | I   |

| 13      | DSI_D3P  | MIPI data pair 3 positive signal   | I   |

| 14      | GND      | Power Ground                       | Р   |

| 15      | DSI_D0N  | MIPI data pair 0 negative signal   | I   |

| 16      | DSI_D0P  | MIPI data pair Opositive signal    | I   |

| 17      | GND      | Power Ground                       | Р   |

| 18      | DSI_CLKN | MIPI data pair CLK negative signal | I   |

| 19      | DSI_CLKP | MIPI data pair CLK positive signal | I   |

| 20      | GND      | Power Ground                       | Р   |

| Pin No. | Symbol  | Description                      | I/O |

|---------|---------|----------------------------------|-----|

| 21      | DSI_D1N | MIPI data pair 1 negative signal | I   |

| 22      | DSI_D1P | MIPI data pair 1positive signal  | I   |

| 23      | GND     | Power Ground                     | Р   |

| 24      | DSI_D2N | MIPI data pair 2negative signal  | I   |

| 25      | DSI_D2P | MIPI data pair 2positive signal  | I   |

| 26      | GND     | Power Ground                     | Р   |

| 27      | STBYB   | Timing control(3.3V)             | I   |

| 28      | SCL     | SCL for EEPROM IC (1.8V)         |     |

| 29      | SDA     | SDA for Bridge IC (1.8V)         |     |

| 30      | LED_PWM | Backlight LED Driver PWM (1.8V)  |     |

| 31      | LED_EN  | LED_EN                           |     |

| 32      | VDD_OTP | OTP Power supply VDD OTP=8.6V    |     |

| 33      | VDDIN   | 3.3V                             | Р   |

| 34      | VDDIN   | 3.3V                             | Р   |

Hongguang Display HG101WU065 9/23

# 3.3 Interface timing Parameter and AC/DC Parameter

The HG101WU065 is operated by the DE only

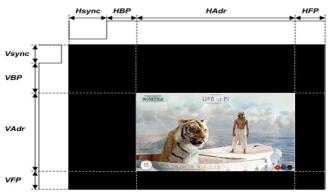

# < Table 5. MIPI Timing Parameter >

|        |                 |                           |                  | 9 . 4 |       |       |                  |

|--------|-----------------|---------------------------|------------------|-------|-------|-------|------------------|

| ITEM   |                 |                           | SYNBOL           | min   | typ   | max   | UNIT             |

| I CD   | Frame Rate      |                           | -                | -     | 60    | -     | Hz               |

| LCD    | LCD Pixels Rate |                           | -                | 150.0 | 150.0 | 159.9 | MHz              |

|        | Mini CLV        | Frequency                 | fCLK             | 490   | 490   | 498   | MHz              |

|        | Mipi CLK        | Period                    | Telk             | 2.01  | 2.04  | 2.04  | ns               |

|        |                 | Horizontal total ti<br>me | tHP              | 1946  | 1946  | 1951  | $t_{CLK}$        |

|        |                 | Horizontal Active time    | tHadr            |       | 1920  |       | $t_{CLK}$        |

|        | Horizontal      | Horizontal Pulse<br>Width | tHsync           | 1     | 1     | 1     | $t_{CLK}$        |

|        |                 | Horizontal Back<br>Porch  | tHBP             | 32    | 32    | 32    | $t_{CLK}$        |

| Timing |                 | Horizontal Front<br>Porch | tHFP             | 110   | 110   | 133   | $t_{CLK}$        |

|        |                 | Vertical total time       | tvp              | 1343  | 1343  | 1366  | t <sub>H</sub>   |

|        |                 | Vertical Active ti<br>me  | tVadr            | 1200  |       |       | t <sub>H</sub>   |

|        | Vertical        | Vertical Pulse Wi<br>dth  | tVsync           | 1     | 1     | 1     | t <sub>H</sub>   |

|        |                 | Vertical Back Por<br>ch   | tVBP             | 14    | 14    | 14    | $t_{\mathrm{H}}$ |

|        |                 | Vertical Front Por<br>ch  | tVFP             | 11    | 11    | 16    | t <sub>H</sub>   |

|        | Bit Ra          | ate                       | TX SPD<br>(MBPS) | 980   | 980   | 995   | Mbps             |

|        |                 | Lane                      | _                | -     | 4     | -     | Lane             |

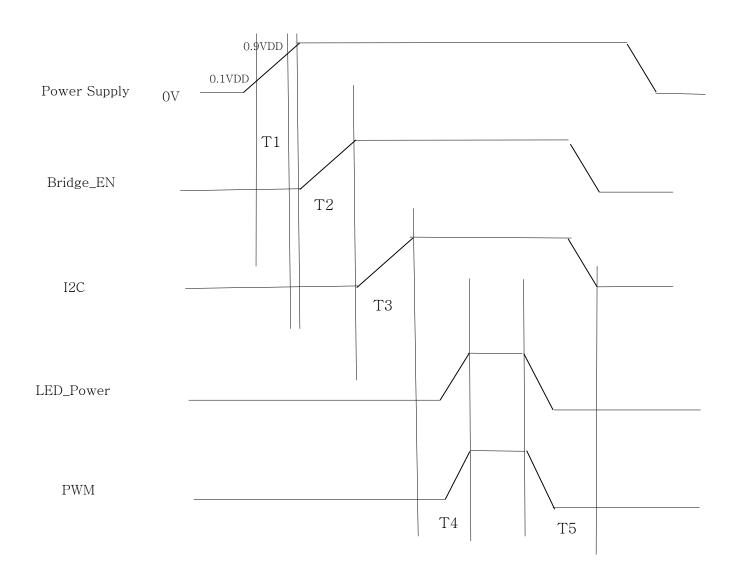

# 3.4 Power Sequence

$0.5 \text{ ms} \le T1 \le 10 \text{ ms}$

T2:10ms

T3:10ms

200ms ≤T4

200ms ≤T5

Hongguang Display HG101WU065 11/23

# **3.4 Power Sequence**

| INITIALIZATION<br>SEQUENCE<br>NUMBER | INITIALIZATION SEQUENCE DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Init seq 1                           | Power on 1 HANA MARKET COSTANT AND A COSTANT |  |  |  |  |

| Init seq 2                           | After power is applied and stable, the DSI CLK lanes MUST be in HS state and the DSI data lanes MUST be driver to LP11 state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Init seq 3                           | Set EN pin to Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Wait 10 ms (1)                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Init seq 4                           | Tie EN pin to High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Wait 10 ms (1)                       | ECTAINORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Init seq 5                           | Initialize all CSR registers to their appropriate values based on the implementation (The SN65DSI8x is not functional until the CSR registers are initialized)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Init seq 6                           | Set the PLL_EN bit (CSR 0x0D.0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Wait 10 ms (1)                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Init seq 7                           | Set the SOFT_RESET bit (CSR 0x09.0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Wait 10 ms (1)                       | . LONE LONE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Init seq 8                           | Change DSI data lanes to HS state and start DSI video stream                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Wait 5 ms (1)                        | 0.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Init seq 9                           | Read back all resisters and confirm they were correctly written                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Init seq 10                          | Write 0xFF to CSR 0xE5 and CSR 0xE6 to clear the error registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Wait 1 ms (1)                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Init seq 11                          | Read CSR 0xE5 and CSR 0xE6. If CSR 0xE5 and CSR 0xE6 != 0x00, then go back to step #2 and re-initialize                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

<sup>(1)</sup> Minimum recommended delay. It is fine to exceed these.

- 注: 1) CSR registers, PLL\_EN,SOFT\_RESET都是寄存器,上电时需要通过I2C配置。Data的状态由处理器进行控制。

- 2) Sequence 9,10,11,这些是IC监测到错误后重新启动时的初始化流程,如果不需要可以不设置。

- 3) 背光PWM时序需与LED\_Power同时上电。

### 4.0 OPTICAL SPECIFICATIONS

### 4.1 Overview

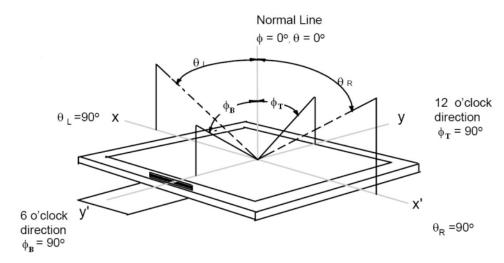

The test of optical specifications shall be measured in a dark room (ambient luminance  $\leq$  1lux and temperature =  $25\pm2^{\circ}\text{C}$ ) with the equipment of Luminance meter system (Gonio meter system and TOPCON BM-5) and test unit shall be located at an approximate distance 50cm from the LCD surface at a viewing angle of  $\theta$  and  $\Phi$  equal to 0°. We refer to  $\theta\varnothing=0$  (=03) as the 3 o' clock direction (the "right"),  $\theta\varnothing=90$  (=012) as the 12 O' clock direction ("upward"),  $\theta\varnothing=180$  (=09) as the 9 O' clock direction ("left") and  $\theta\varnothing=27$  0(=06) as the 6 O' clock direction ("bottom"). While scanning  $\theta$  and/or  $\varnothing$ , the center of the measuring spot on the Display surface shall stay fixed.

### 4.2 Optical Specifications

# < Table 9. Optical Table >

| Item                                          | Symbol              | Condition | Min   | Tym   | Max   | Unit              | Note                  |

|-----------------------------------------------|---------------------|-----------|-------|-------|-------|-------------------|-----------------------|

| item                                          |                     | Condition |       | Тур.  | IVIAX | Offic             | Note                  |

|                                               | θL                  |           | 70    | 80    |       |                   |                       |

| Viewing Angle                                 | $\theta_{\text{R}}$ | Cr≥10     | 70    | 80    |       | deg               | <u>Note 1</u>         |

| Viewing Angle                                 | $\Psi_{T}$          | CIZIO     | 70    | 80    |       | deg               | <u>ivote i</u>        |

|                                               | $\psi_{\text{B}}$   |           | 70    | 80    |       |                   |                       |

| Contrast Ratio                                | Cr                  | θ=0°      | 700   | 900   |       | -                 | Note 2                |

| Response Time                                 | Tr+Tf               | FF=0°     |       | 30    | 35    | ms                | Note 3                |

|                                               | Rx                  |           |       | 0.644 |       | -                 | @BOE BLU<br>Note 4    |

|                                               | Ry                  | θ=0°      | -0.03 | 0.344 | +0.03 |                   |                       |

|                                               | Gx                  |           |       | 0.315 |       |                   |                       |

| Color Coordinate of CIE1931                   | Gy                  |           |       | 0.632 |       |                   |                       |

| Color Coordinate of CiE1931                   | Вх                  |           | -0.03 | 0.157 |       |                   |                       |

|                                               | Ву                  |           |       | 0.054 |       |                   |                       |

|                                               | Wx                  |           |       | 0.310 |       |                   |                       |

|                                               | Wy                  |           |       | 0.330 |       |                   |                       |

| NTSC Ratio                                    | NTSC                | CIE1931   |       | 72    |       | %                 | @BOE BLU<br>Note 5    |

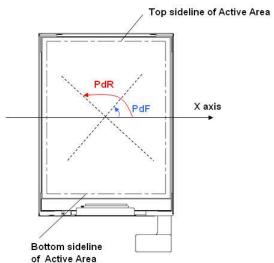

| Polarization Direction of Fro<br>nt Polarizer | PdF                 |           | _     | 0     |       | deg               | Absorption            |

| Polarization Direction of Rea<br>r Polarizer  | PdR                 | -         |       | 90    |       | deg               | <u>axis</u><br>Note 6 |

| Luminance of White                            | Y <sub>w</sub>      | θ=0°      | 1     | 400   | -     | cd/m <sup>2</sup> | Note 7                |

| Brightness Uniformity                         | △Bp                 | θ=0°      | 75    | 80    | -     | %                 | Note 8                |

### Note 1:The definition of Viewing Angle

Refer to the graph below marked by  $\theta$  and  $\phi$ .

### Note2:ThedefinitionofContrastRatio

(Contrast Ratio is measured in optimum common electrode voltage)

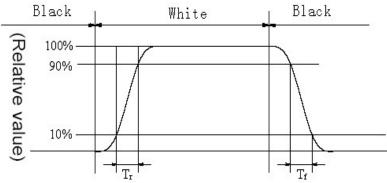

### Note3:DefinitionofResponse time.(Test LCD using RD80S or similar equipments):

The output sign also photo detector are measured when the input sign also are changed from "black " to "white" (Voltage falling time) and from "white" to "black" (Voltage rising time), respectively. The response time is defined as the time interval between the 10% and 90% of amplitudes . Refer to fi gures below.

### Note 4: Color Coordinates of CIE 1931

The test condition is at ILED=20mA and measured on the surface of LCD module at 25°C.

Measurement equipment: CS2000 or similar equipments

The Color Coordinate (CIE 1931) is the measurement of the center of the display shown in below figure.

### Note 5: Definition of Color of CIE Coordinate and NTSC Ratio.

### **Note 6: Polarization Direction Definition**

- Viewing direction is normal user viewing direction which is vertical to the display surface

- •The polarizer which is closer to viewer is defined as Front Polarizer

- •The polarizer which is on the rear side of viewer is defined as Rear Polarizer

- •The X axis is defined as parallel line to top & bottom sidelines of the Active Area

- •PdF which is marked in blue arrow is polarization degree of Front polarizer

- PdB which is marked in red arrow is polarization degree of Back polarizer

- •The polarization degree parameter must be indicated in range of 0deg to 180deg according to above definition

Hongguang Display HG101WU065 15/23

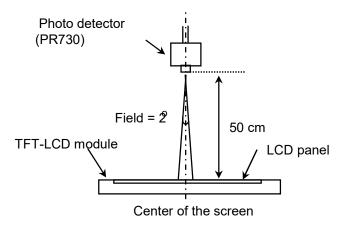

### **Note7:Luminance measurement**

The test condition is at ILED=22mA and measured on the surface of LCD module at 25°C.

- ●The data are measured after LEDs are lighted on for more than 9 minutes and LCM displays are fully white. The brightness is the value of center measured spots. Measurement equipment LMS OTS or si milar equipments(Field of view:1deg,Distance:50cm)

- Measuring surroundings: Dark room.

- •Measuring temperature: Ta=25°C.

- •Adjust operating voltage to get optimum contrast at the center of the display.

- •Measured value at the center point of LCD panel must be after more than 5 minutes while backlight turning on.

Optical characteristics measurement setup

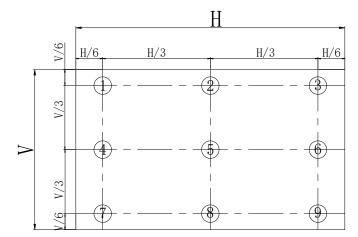

### **Note8:Uniformity**

- •The test condition is at ILED=22mA and measured on the surface of LCD module at 25°C.

- Measurement equipment:LMS OTS or similar equipments

- •The luminance uniformity is calculated by using following formula:

- $\bullet \triangle Bp = Bp (Min.) / Bp (Max.) \times 100 (%)$

- ●Bp (Max.) = Maximum brightness in 9 measured spots

- •Bp (Min.) = Minimum brightness in 9 measured spots.

# **5.0 RELIABLITY TEST**

The Reliability test items and its conditions are shown in below.

<Table 10. Reliability Test Parameters >

| No | Test Items                                        | Conditions                      |

|----|---------------------------------------------------|---------------------------------|

| 1  | High temperature storage test                     | 80°C 240hr                      |

| 2  | Low temperature storage test                      | -30°C 240hr                     |

| 3  | Low temperature operation test                    | -20℃ 240hr                      |

| 4  | High temperature operation test                   | 70°C 240hr                      |

| 5  | High temperature & high humidity (operation test) | 60℃ 90%RH 240hr                 |

| 6  | Thermal Shock Test                                | -40°C~85°C 0.5hr/cycle 100cycle |

| 7  |                                                   |                                 |

| 8  |                                                   |                                 |

| 9  |                                                   |                                 |

| 10 |                                                   |                                 |

|    |                                                   |                                 |

Hongguang Display HG101WU065 17/23

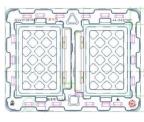

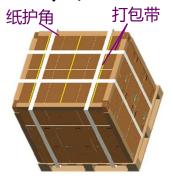

# 6.0 PACKING INFORMATION(产品形态: MDL)

# **Packing procedure:**

-. 将 2pcs LCM 平放入Tray, 下E部PE 垫片 CF 侧向上放置;

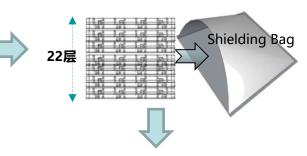

- -. 将22pcs PET Tray 平放入Shielding Beg, 顶部为空Tray进行抽真空处理;

- -. Tray 无需区分旋转码放

- -. 每个Pallet上放8层Box, 1层4箱

- -. Pallet 缠绕膜包装

- -. 756pcs / Pallet

- -.将PET Tray堆码后平放入Inner Box 上下放置EPE Board

- -. 容量: 42pcs/Inner Box

Hongguang Display HG101WU065 18/23

# 7.0 Handling & Cautions

### 7.1 Mounting Method

- The panel of the LCD consists of two thin glasses with polarizers which easily get damaged. So extreme care should be taken when handling the LCD.

- Excessive stress or pressure on the glass of the LCD should be avoided. Care must be taken to insure that no torsional or compressive forces are applied to the LCD unit when it is mounted.

- If the customer's set presses the main parts of the LCD, the LCD may show the abnormal display. But this phenomenon does not mean the malfunction of the LCD and should be pressed by the way of mutual agreement.

- To determine the optimum mounting angle, refer to the viewing angle range in the specification for each model.

- Mount a LCD module with the specified mounting parts.

### 7.2 Caution of LCD Handling and Cleaning

- Since the LCD is made of glass, do not apply strong mechanical impact or static load onto it. Handling with care since shock, vibration, and careless handling may seriously affect the product. If it falls from a high place or receives a strong shock, the glass may be broken.

- The polarizers on the surface of panel are made from organic substances. Be very careful for chemicals not to touch the polarizers or it leads the polarizers to be deteriorated.

- If the use of a chemical is unavoidable, use soft cloth with solvent (recommended below) to clean the LCD 's surface with wipe lightly.

- -IPA(Isopropyl Alcohol), Ethyl Alcohol, Trichlorotriflorothane

- Do not wipe the LCD's surface with dry or hard materials that will damage the polarizers and others. Do not use the following solvent.

- -Water, Ketone, Aromatics

- It is recommended that the LCD be handled with soft gloves during assembly, etc. The polarizers on the LCD's surface are vulnerable to scratch and thus to be damaged by sharp particles.

- Do not drop water or any chemicals onto the LCD's surface.

- A protective film is supplied on the LCD and should be left in place until the LCD is required for operation.

- The ITO pad area needs special careful caution because it could be easily corroded.

Do not contact the ITO pad area with HCFC, Soldering flux, Chlorine, Sulfur, saliva or

fingerprint. To prevent the ITO corrosion, customers are recommended that the ITO

area would be covered by UV or silicon.

# 7.3 Caution Against Static Charge

- The LCD modules use C-MOS LSI drivers, so customers are recommended that any unused input terminal would be connected to Vdd or Vss, do not input any signals before power is turn on, and ground you body, work/assembly area, assembly equipments to protect against static electricity.

- Remove the protective film slowly, keeping the removing direction approximate 30-degree not vertical from panel surface, If possible, under ESD control device like ion blower, and the humidity of working room should be kept over 50%RH to reduce the risk of static charge.

- Avoid the use work clothing made of synthetic fibers. We recommend cotton clothing or other conductivity-treated fibers.

- In handling the LCD, wear non-charged material gloves. And the conducting wrist to the earth and the conducting shoes to the earth are necessary.

# 7.4 Caution For operation

- It is indispensable to drive the LCD within the specified voltage limit since the higher Voltage than the limit causes the shorter LCD's life. An electro-chemical reaction due to DC causes undesirable deterioration of the LCD so that the use of DC drive should avoid.

- Do not connect or disconnect the LCD to or from the system when power is on.

- Never use the LCD under abnormal conditions of high temperature and high humidity.

- When expose to drastic fluctuation of temperature (hot to cold or cold to hot), the LCD may be affected; Specifically, drastic temperature fluctuation from cold to hot, produces dew on the LCD's surface which may affect the operation of the polarizer and the LCD.

- Response time will be extremely delayed at lower temperature than the operating temperature range and on the other hand at higher temperature LCD may turn black at temperature above its operational range. However those phenomena do not mean malfunction or out of order with the LCD. The LCD will revert to normal operation once the temperature returns to the recommended temperature range for normal operation.

- Do not display the fixed pattern for a long time because it may develop image sticking due to the LCD structure. If the screen is displayed with fixed pattern, use a screen saver.

# 7.5 Packaging

- Modules use LCD element, and must be treated as such.

- -Avoid intense shock and falls from a height.

- -To prevent modules from degradation, do not operate or store them exposed directly to sunshine or high temperature/humidity for long periods.

# 7.6 Storage

- A slight dew depositing on terminals is a cause for electro-chemical reaction resulting in terminal open circuit. Relative humidity of the environment should therefore be kept below 60%RH.

- Original protective film should be used on LCD's surface (polarizer). Adhesive type

protective film should be avoided, because it may change color and/or properties of

the polarizers.

- Do not store the LCD near organic solvents or corrosive gasses.

- Keep the LCD safe from vibration, shock and pressure.

- Black or white air-bubbles may be produced if the LCD is stored for long time in the lower temperature or mechanical shocks are applied onto the LCD.

- In the case of storing for a long period of time for the purpose or replacement use, the following ways are recommended.

- -Store in a polyethylene bag with sealed so as not to enter fresh air outside in it.

- -Store in a dark place where neither exposure to direct sunlight nor light is.

- -Keep temperature in the specified storage temperature range.

- -Store with no touch on polarizer surface by the anything else. If possible, store the LCD in the packaging situation LCD when it was delivered.

# 7.7 Safety

- For the crash damaged or unnecessary LCD, it is recommended to wash off liquid crystal by either of solvents such as acetone and ethanol an should be burned up later.

- In the case the LCD is broken, watch out whether liquid crystal leaks out or not. If your hands touch the liquid crystal, wash your hands cleanly with water an soap as soon as possible.

- If you should swallow the liquid crystal, first, wash your mouth thoroughly with water, then drink a lot of water and induce vomiting, and then, consult a physician.

- If the liquid crystal should get in your eyes, flush your eyes with running water for at least fifteen minutes.

- If the liquid crystal touches your skin or clothes, remove it and wash the affected part of your skin or clothes with soap and running water.

# 8.0 APPENDIX

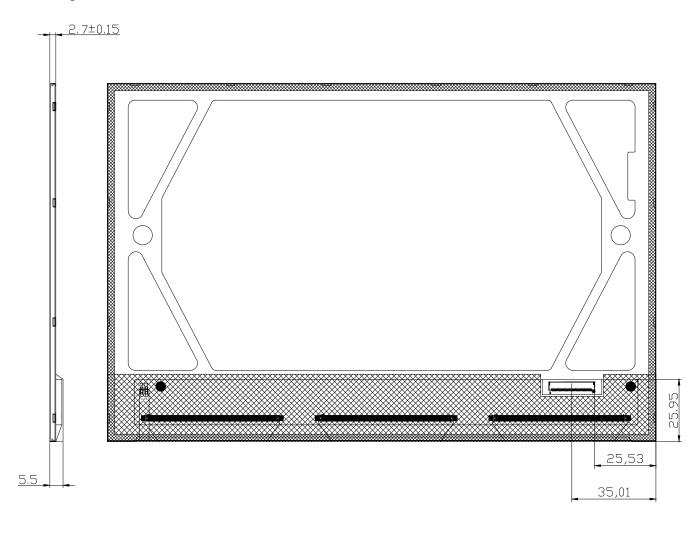

# **Mechanical Drawing**

Drawing Attachment: Front

Hongguang Display HG101WU065 22/23

# **Mechanical Drawing** Drawing Attachment: Back

HG101WU065 Hongguang Display 23/23