Werner Dilger Fidunhofer-Institut f*u*r Inforniations - und Datonverarbeitung D-7500 Karlsruhe 1

## ABSTRACT

An associative processor for theorem proving in first order logic is described. It. is designed on the basis of the deduc-tion plan method, introduced by Cox and Pietrzykowski. The main features of this method are the separation of unification from deduction and the incorporation of a method for intelligent backtracking- This kind of backtracking is based on a special unification procedure. An improved version of this unitization procedure is given, which outputs a unification graph with constraints. In the case of a unification conflict, sufficient inf:onnation for a directed backtracking step can be gained from the unifiestion graph. According to the deduction plan method, the ASSIP-T memory consists of two parts, one for the deduction plan and the other for the uni-fication graph. ASSIP-T can perform de-duction and unification in parallel. Beth duction and unification in parallel. Both m e m o ry parts consist of a set of subparts each of which keeps the information about clauses or terms, respectively. A subpart is a 1 i n e a r a r r ay of cells pr o v i d e d with a control u n i t a nd can be re g a rd e d as a subprocessor.

# 1. In Production

The progress of microelectronics allows the realizations of more and more powerful processors for special purposes. One such type of processors is the associative processor. Its associative memory allows content oriented parallel access to the data stored in it. This makes the associative processors well suited for pattern handling processes. In artificial intelligence e.g., most processes are pattern directed deductions. One of it is theorem proving. In this paper a model of an associative processor is described which is able to prove theorems of first order logic. It is designed on the basis of the deduction plan method, i.e. it incorporates a method for intelligent backtracking. After some basic definitions in the

After some basic definitions in the second section, the deduction plan method is described. The special unification procedure used within this method follows. The output of this procedure is a unificaHans-Albert Schneider Computer Science Department University of Kaiserslautern Postfach 3 04 9 D-6750 Kaisorslautern

tion graph with constraints. In the case of a unification conflict, the unification graph gives sufficient information for a directed backtracking step. This is described in section 5. Then the structure of the ASSIP-T processor which is aimed to perform the deduction plan method is described. Section 7 gives the data structures which are to be mapped on the ASSIP-T memory. Finally, the representation of the data structures in the ASSIP-T memory is sketched.

### Basic Definitions

A labelled graph is a triple G = (V(G), I(G), E(G)) where V(G), I(G), and E(G) are the sets of nodes, labels, and edges respectively. A path of length n in G is a sequence w =  $v_1, e_1, v_2, e_2, \dots$   $e_n, v_{n+1}$  (n=0) with  $v_j \in V(G)$  and  $e_j \in E(G)$ . If  $v_j = v_{n+1}$ , the path is called closed. A closed path which contains each inner node at most once is called a cycle.

Assume there are given disjoint alphabets of variables, function symbols and predicate symbols. Each function and predicate symbol has an arity. A constant is a O-ary function symbol. An expression is a variable or a term. A term is a constant or a string of the form  $f(q_1, \ldots, q_n)$ , where f is an n-ary function symbol (n=1) and  $q_1, \ldots, q_n$  are expressions. An atom is a string of the form  $P(q_1, \ldots, q_n)$ , where P is an n-ary predicate symbol (n=0) and  $q_1, \ldots, q_n$  are expressions. If A is an atom, then A and -A are literals. A clause is a finite set of literals. The empty clause is denoted by  $\Box$ .

A constraint is a set consisting of two expressions. A set of constraints is called a constraint set. If p and q are expressions (terms), then p is a subexpression (subterm) of q if p = q or q = $f(q_1, \ldots, q_n)$  and p is a subexpression (subterm) of one of the  $q_1$ . An expression (term) p is a subexpression (subterm) of a constraint set C, if there is a constraint  $\{q_1, q_2\}$  in C such that p is a subexpression (subterm) of  $q_1$  or of  $q_2$ . The set of all subexpressions of C is denoted by SEXPR(C).

A substitution is a finite set of pairs (v,q), denoted by v/q, where v is a variable and q an expression and v  $\pm$  q. Application of a substitution  $\sigma$  =  $\{v_1/q_1, \dots, v_n/q_n\}$  to an expression or a literal p is the replacement of each occurrence of  $v_i$  in p by  $q_i$  , for all i = 1,...,n.  $\sigma$  is called a remaining if  $q_1, \ldots, q_n$  are pairwise different variables and  $(v_1, \ldots, v_n)$  (1  $\{q_1, \ldots, q_n\} = \emptyset$ . A clause cl is called a variant of a clause cl, if cl and cl have no variables in common and there is a renaming  $\sigma$  such that cl =  $\sigma$  cl. If  $E = \{p_1, \ldots, p_n\}$  is a set of expressions then a substitution  $\sigma$ is called a unifier of E, if  $op_1 = \dots = op_n$ . E is then called unifiable.  $\sigma$  is called a most general unifier of E if for each unifier  $\tau$  there is a unifier  $\rho$  such that  $\tau = \sigma \cdot \rho$ .

Let  $C = \{c_1, \ldots, c_n\}$  be a constraint set. The set BE(C) of Boolean expressions over C is defined by

- 1. 0,1,c<sub>1</sub>,...,c<sub>1</sub>  $\in$  BE(C). 2. II B<sub>1</sub>,B<sub>2</sub>  $\in$  BE(C), then (B<sub>1</sub>  $\vee$  B<sub>2</sub>),

- $(B_1 \land B_2) \in BE(C)$ .

3. BE(C) contains no other elements.

3. Deduction Plans

The deduction plan method is a resolution based method, i.e. a refutation method. It starts with a set of clauses and tries to construct a "closed" and "correct" deduction plan. If it succeeds, the clause set is proved to be unsatisfiable. The central idea of the method is to separate deduction from unification. This allows the application of a special unification algorithm which, in the case of a unifi-cation conflict, not simply stops with failure, rather it yields information about the causes of unification conflicts, namely certain deduction steps, which then can be reset. In section 5 this way of processing is called "intelligent backtracking "

The nodes of the deduction plan are the input clauses and eventually variants of them. Two clauses can be connected by an edge if they contain literals with the same precidate symbol but different signs (negated or not negated). Therefore a (labelled) edge between two clauses cl and  $cl_2$  is a triple ( $cl_1$  (t,u,v),  $cl_2$ ,),

where u and v are literals in  $cl_1$  and  $cl_2$ respectively, satisfying the condition on their predicate symbols and negation signs, t is the type of the edge. There are two types of edges: SLB and RED. All edges are of type SLB except those refering backward to a clause which is already in use. If each literal in each clause in-cluded in the plan occurs in an edge, the deduction plan is closed. If the set

of pairs of torms arising from the pairing of literals by edges is uniliable, the deduction plan is correct. Cf. for this section (Cox and Pietrzykowski 1979) a n d (Cox and Pietrzykowski 1981).

Def in ition

Let S be a set of input clauses and L = U cl. A deduction graph on S is a graph c1CS

G = (V(G), I(G), E(G)) which has the variants of S as node set V(G),  $T(G) \subseteq (SUB,RED) \times L \times L$ with: if  $e = (cl_1, b, cl_2) \in E(G)$  then b =

(t,u,v),  $u \in cl_1, \ v \in cl_2, \ t \ is called the$

type of the edge e, a the starting literal and v the target literal. A literal u of a dause cl is called key literal iff there is an incoming edge with type SLB and target literal u. Each literal u of a dause čl is called a *sub problem* iff it is not a key literal. A subproblem u E cl is *open* iff there is no outcoming edge with sťarting literal u. A subproblem ŭ is called closed iff it is not. open . os (G) 1 s the set of open subproblems of a deduction graph G. G is called *closed*, iff os(G) - 0. A node cl is called *predecessor* of

a node cl., iff there is a path from cl

to d<sub>n</sub> which contains only edges of type

SLB (SUB-path). If u is the starting Iiteral of the first edge of a SUB-path from cl to  $cl_2$ , then u is called *preceding literal* of  $cl_2$  and  $cl_2$  is called *successor* of c 1 .

We omit the definition of the deduction plan here. It is a deduction graph which is constructed by a number of deduction steps, i.e. edge drawing steps, starting from a basic plan which consists of one node only.

Example

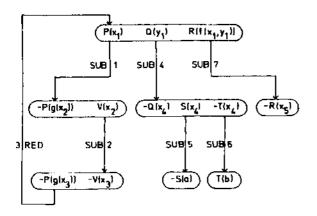

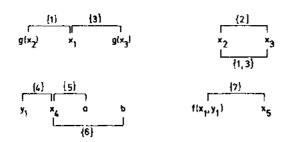

$S = \{ \{ P(x), Q(y), R(f(x,y)) \} \}$  $\{-P(g(x)), V(x)\},\$  $\{-P(g(x)), -V(x)\},\$  $\{-Q(x), S(x), -T(x)\},\$ (-s(a)),{-s(b)}, (T(b)),  $\left\{-R(\mathbf{x})\right\}$

is a set of eight input clauses. Figure 1 shows a closed deduction plan for S. The edges are drawn in such a way that they begin beyond the starting literal and point to the target literal. Therefore they are only labelled by their type and, beyond it, by the numbers of the steps in the plan construction within which the edges were drawn. The literals  $-F(g(x_2)), -V(x_3), -Q(x_4), -S(a), T(b),$

and -R(x<sub>5</sub>) are key literals, the other literals are subproblems. The first dause in S is the basic node, it is a predecessor

### of all nodes.

Figure 1: A closed deduction plan

#### Detinition

Let G be a deduction plan and e an edge of G with label (t,u,v), where (omitting the sign)  $u = P(u_1, \ldots, u_n)$ ,  $v = P(v_1, \ldots, v_n)$ (n.0). To e a constraint set C(e) is assigned by

$$C(e) = \{\{u_1, v_1\}, \dots, \{u_n, v_n\}\}$$

A constraint set  $C(G)$  is assigned to G by

$$C(G) = 0 = C(e)$$

., ₽FE(G)

G is called correct iff C(G) is unifiable.  $\hat{\theta}(G)$  denotes the most general unifier of C(G).  $\theta(G) os(G)$  is the clause derived from G. If G is closed, the clause derived from G is the empty clause.

Soundness and completeness of the deduction plan method are shown in the references given above.

4. Unification Graphs With Constraints

Unification by means of unification graphs with constraints is closely related to the unification method of Cox. (Cox 1981). It simplifies this method but is still sound and complete. Cf. for this section (Dilger and Janson 1983) and (Dilger and Janson 1984).

The unification process starts with a constraint set C. By two stops, the transformation stop and the sorting stop, it yields a unification graph with constraints, UWC for short, for C. A UWC consists of

- the node set V(UwC) = SEXPR(C)

- the label set  $I(UwC) = 2^{C}$

- the edge set  $E(UwC) = EU(UwC) \cup ED(UwC)$ where  $EU(UwC) \subseteq V(UwC) \times (2^{C}-\{\emptyset\}) \times V(UwC)$ and  $ED(UwC) \subseteq V(UwC) \times \{\emptyset\} \longrightarrow V(UwC)$

EU(UwC) is a set of undirected edges,

$ED\left(UwC\right)$  a set of directed edges. Construction of UwC starts with the initial graph  $UwC_{\tau}$  which consists only of the nodes.

EU(UwC) is determined in the transformation step, ED(UwC) in the sorting step.

### Definition

A path in UwC which contains only edges from EU(UwC) is called a connection. A connection  $v = p_1, e_1, \dots, e_n, p_{n+1}$  is called simple iff  $p_j \neq p_j$  for all i,  $j (1 \le i \le j \le n+1)$ . A closed path in UwC which contains at least one edge from ED(UwC) is called a loop. A loop is called simple iff  $p_j \neq p_j$ for all i, j such that  $1 \le i \le j \le n+1$ . If e =(p, a, q) is an edge in E(UwC), then a is called the value of e, denoted val(e) = a. Let  $w = p_1, e_1, \dots, e_n, p_{n+1}$  be a path in UwC. Then the value of w is

$$val(w) \in \bigcup_{i=1}^{n} val(e_{j})$$

The transformation step

The algorithm of the transformation step can be found in (Dilger and Janson 1984). It draws undirected edges between the nodes in the following way: If  $e_i = \{p,q\}$  is a constraint, the nodes p and q are connected by the edge  $e_i = (p, \{e_i\}, q)$ . This results in a (possibly empty) set of new constraints, which are treated later on in the same way.

#### Example

Let  $C = \{c_1, c_2\}$  be a constraint set with

- $c_1 = \{G(s,z), G(u,P(y,y))\}$

- $c_{ij} = \{u, F(y,G(s,z))\}$

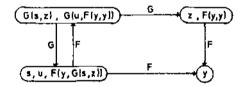

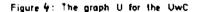

The initial UwC consists only of the nodes SEXPR(C) and is shown in figure 2. The first constraint  $c_1$  is removed, an appropriate undirected edge is added to the UwC and the new constraints  $\{s,u\}$  and  $\{z,F(y,y)\}$  are added to the constraint set.

Now the second constraint is removed from the constraint set. Because u is a variable, there cannot be formed any new constraints, only an edge is added to the DwC. The remaining two constraints are treated as the second one. Because they had their origin in the first constraint,

Figure 2: The initial UwC for the constraint set C

the edges in the UwC arc labelled by {c }. At the end of the transformation step the UwC has the form represented in figure J.

## The sorting step

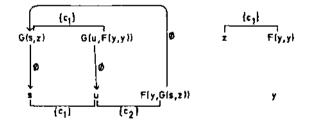

The transformation step classifies the nodes of UwC in such a way that two nodes be 1 ong to the same c 1 as siff the re is a connection between them. In the example above we have four classes. In the sorting step, firstagraph U is constructed which consists of these classes as nodes and which has a directed edge labelled by f from class X to class Y iff there is a term f(p, ..., p) in X and an expression P, (i f {1,...,n}) in Y.

$$\begin{array}{c} \{c_1\} \\ \hline \\ G(s,z) \\ G(u,F(y,y)) \\ z \\ F(y,y) \end{array}$$

Figure 3: The UwC at the end of the transformation step

Figure5: The complete UwC at the end of the sorting step

This graph is shown for the example in figure 4. Now the edges of U which belong to a cycle are added to the UwC as edges between the appropriate nodes and labelled by 0. So we get the complete UwC of figure 5.

Soundness and completeness of the unification algorithm are proved in (Dilger and J a n s o n 1984). The main theorem is: A constraint set C is unifiable iff all terms in UwC which are connected by a simple connection begin with the same function symbol and UwC contain s n o s i ra p1e 10 o p s.

Thus, e.g., our example constraint set is not unifiable because the UwC of figure ') contains a simple loop.

## S. Intelligent Backtracking

If during the unification process a unification conflict has been detected, i.e. a clash (unification of terms with different function symbols) or a cycle, the actual deduction plan is not correct. One or several steps in the construction have to be reset in order to get a correct plan. By means of the information kept by the UwC these steps can be determined immediately. The numbers of the deduction steps are contained in the labels of the undirected edges of UwC. Therefore, we have to examine the values of certain paths through UwC. First, the relevant values are gathered in the sets ATTACH and LOOP.

```

LOOP := \{a \subseteq C \mid a \text{ is the value of } a \\ \text{simple loop in UwC}\}

```

We define:

$B_{ATTACH} := D \Sigma c$  $a \in ATTACH c \in a$

$\begin{array}{ccc} \mathbf{B} & & \mathbf{E} & \mathbf{I} & & \boldsymbol{\Sigma} & \mathbf{c} \\ \mathbf{LOOP} & & \mathbf{a} \in \mathbf{LOOP} & \mathbf{c} \in \mathbf{a} \end{array}$

BUNIF := BATTACH A BLOOP

The minimal disjunctive normal form of  $B_{\rm UNIF}$  has the form

$B_{UNIF}^{\dagger} = B_1 \vee \ldots \vee B_k$

for some k-1, where each  $B_1$  is a conjunctive term. From  $B'_{UNIF}$  the minimal conflict sets are determined by

For details of. (Dilger and Janson 1984).

## Example

Consider the deduction plan of section 3, represented in figure 1. Following the edges according to their numbers we get the constraints

The UWC for these constraints is shown in figure 0. It has no directed edges, because the graph U, constructed in the sorting step, contains no cycles.

There is a clash in the UwC, namely a simple connection between a and b. Therefore, ATTACH = {{5,6}}, Clearly, LOOP =  $\emptyset$ . Thus, B<sub>ATTACH</sub> = 5, V 6, B<sub>LOOP</sub> = 1, B<sub>UNIF</sub> = 5, V 6 = B<sub>INIF</sub> and most = {5}, mcst = {6}.

Figure 6: A complete UwC

Figure 7: A closed correct deduction plan

Backtracking is performed as follows. Take for the backtracking step mes =  $\{S\}$ Edge number fj and node -S(a) are removed from the plan. Thereby, the literal S(x.) be comes an open subprobleni. But there is another clause in the input clause set which fits so close the literal, namely  $\{-S(b)\}$ . This yields the closed correct deduction plan of figure 7. Thn reader is invited to check that backtracking with .ncs<sub>2</sub>-  $\{6\}$  does not result in a closed plan.

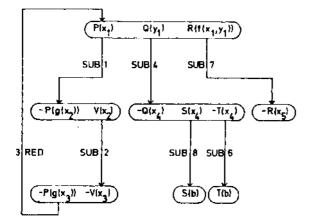

# 6. The structure Of ASSIP-T.

In che deduction plan method, deduction and unification are separated from each other. For deduction, the data struc ture "doduction plan" is used, for unific dtion the data structure "utiification

Figure 8 : The structure of ASSIP-T

gr, iph wiih constrain Ls". In ASS1P-T, both are kept in appropriate pArts of the assodative meinory. Thus, the associative memory is divided in two main parts, AMI for the deduction plan and AM2 for the UwC, of. figure 0. The control unit of the processor consists of fo 11 r components: - the he ad contro 1 HC

- twosubcont.rolsSC1andSC2

- a c o n v e n ti o rial mem o ry CM

The subcontrols operate on the UwC. They tan work independently froin each other, but under control of HC, so they can work in parallel and this is useful during the initial construction of the UwC and during its reconstruction after a back tracking step. Thus, we have not only parallel access to the data in the assocative memories, rather there are two further steps to parallel processing: one by the parallel treatment of deduetion plan and UWC, the other by the use of SC1 and SC2 in parallel. For details of. (Dilger and Schneider 1985). For an introduction to and a survey on the field of associative processors of. (Fu and Ichikawa 1982), (Kohonen 1984), (Parhami 1973) and (You and Fung 1975).

Associative Memory Oriented Data Structures

Several data structures are used for an associative memory oriented representation of deduction plans and UwCs, i.e. representations that can easily be mapped on associative memories. The design principles for the data structures are:

- Deduction plan and UWC both being graphs - are taken as sets of nodes together with their edges.

- 2. A clause together with all its variants in represented as only one data object and therein their constant part is represented only once. The same holds for the terms of the UWC.

Due to lack of space we omit the data structures, which can be found in (Dilger and Schneider 1985), and only give some idea of them.

For each literal, we keep in its variants-part the edges to other literals, represented by the target literals and the edge labels, because in fact they are drawn between variants of clauses. This way of storing edges can be thought to be similar to the way they are drawn e.g. in figure 1.

The nodes of the UWC are variants of expressions. Therefore, we store all expressions which are variants of one another in the same part of AM2 (cf. section 8) together with the edges incident of them.

Because we build variants by just indexing the variables (cf. figure 1), we are able to represent the information "edge e is incident to node t" by simply storing the index of t's variables at e, too. Storing directed edges is done in a most efficient way, which just needs one bit for each argument of the respective term.

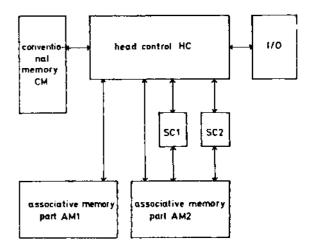

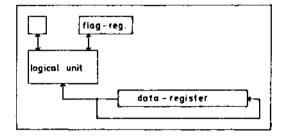

Representation And Handling Of The Data Structures In The ASSIP-T Memory

We will sketch here the representation of the UwC in the memory part AM2. It is similar for the deduction plan. AM2 is divided into several parts, one for each object of type EXPRESSION (that is, an expression, its variants and the edges incident to them). Every AM2-part consists of a linear array of cells and is provided with a special control, called the "EXP-control". The entries in an object of type EXPRESSION can all be represented by the data types INTEGER and BOOLEAN. Therefore all cells of the AM<sup>'</sup>parts have the same form. They consist of

- a logical unit - a control bit

- a 4 bit flag register

- a 32 bit data register

of, figure 9. The purpose of the flag register is to characterize the type of information which actually is stored in the data register, e.g. index and class of variants, information about edges etc. Thus, each cell can store an arbitrary part of an EXPRESSION.

Figure 9: A subprocessor cell of ASSIP-T

The EXP-control has to perform entry, change and query instructions on the components of an object of type EXPRESSION. The head control on the other hand just has to broadcast information to the AM.<sup>1</sup>parts and to gather it from them by means of instructions like

"FOR ALL Sexpression? WITH condition?

DG - instruction."

or - "FOR ONE Sexpression? WITH condition?"

DO Sinstruction>"

Thus, the two-level organisation of the ASSIP-T memory corresponds to a two-level evaluation of the instructions.

9. Conclusion

As far as we know there is no other approach similar to ours. The architecture of the fifth generation inference machine is data flow oriented and does not take into consideration associative access to data cf. (Moto-oka and Fuchi 1983). The main problem with our approach is the storage of the unification graph because its number of edges has an upper bound that is exponential with respect to the number of deduction steps. One may assume that this upper bound will never be reached in practice, but we have to work out another representation of the edges. By means of several head control-subcontrolgroups, we should be able to perform ORparallel as well as AND-parallel processing due to the separation of deduction and unification.

# REFERENCES

- Cox, P.T. On determining the causes of nonunifiability. Auckland Computer Science Report No 23, University of Auckland, 1901.

- Cox, P.T. and Pietrzykowski, T. Deduction plans: A basis for intelligent backtracking. University of Waterloo Res. Rep. CS-79-41, 1979.

- Cox, P.T. and Pietrzykowski, T. Deduction plans: A basis for intelligent backtracking. <u>IEEE Trans. Pattern Ana-</u> lysis and Machine Intelligence, vol. PAMI-3, (1) 1981, 52-65.

- Dilger, W. and Janson, A. Unifikationsgraphen als Grundlage fur intelligerites Backtracking. <u>Proc. of the</u> <u>German Workshop on Artificial In-</u> <u>telligence</u>,Informatik-Fachberichte 76, Springer-VerJag, 1983, 189-196.

- Dilger, W. and Janson, A. A unification graph with constraints for intelligent backtracking in deduction systems. Interner Bericht 100/84, Fachbereich Informatik, Universitat Kaiserslautern, 1984.

- Dilger, W. and Schneider, II.-A. A theorem proving associative processor, In preparations .

- Fu, K.S. and Ichikawa, T. (eds) <u>Special</u> <u>computer architectures for pattern</u> <u>process</u>ing. CRC Press, Boca Raton, Florida," 1982.

- Kohonen, T. Se<u>lf"-organizations and asso-</u>cia<u>tive memory</u>. Springer, Berlin, 1984.

- Moto-oka, T. and Fuchi, K. The architectures in the fifth generation computers. <u>Proc. of the</u> IFIP 83, 1983, 589-602.

- Parhami, B. Associative memories and processors: An overview and selected bibliography. Proc. of the IEEE 61, 1973, 722-730.

- You, S.S. and Fung, H.S. Associative processor architecture - a survey. <u>Proc. of the Sagamore Computer</u> <u>Conference 1975</u>.