Preprint

Article

An Optimal Switching Sequence Model Predictive Control Scheme for the 3L-NPC with Output LC Filter

Altmetrics

Downloads

118

Views

54

Comments

0

A peer-reviewed article of this preprint also exists.

This version is not peer-reviewed

Submitted:

11 December 2023

Posted:

14 December 2023

You are already at the latest version

Alerts

Abstract

In some applications of microgrid and distributed generation, it is required to feed islanded or stand-alone loads with high-quality voltage to provide low total harmonic distortion (THD). To fulfil these demands, an LC filter is connected to the output terminals of power electronics converters. A cascaded voltage and current control loop with pulse-width modulation schemes are used to regulate the voltage and current in these systems. However, these strategies have some drawbacks, particularly when multiple-input multiple-output plants (MIMO) are controlled using single-input single-output (SISO) design methods. This methodology usually produces a sluggish transient response and cross-coupling between different control loops. In this paper, a model predictive control (MPC) strategy based on the concept of optimal switching sequences (OSS) is designed to control voltage and current in an LC filter connected to a three-level neutral-point clamped converter. The strategy solves two well-formulated optimisation problems to achieve control of the LC filter variables and the voltages of the DC-link capacitors. Hardware-in-the-Loop (HIL) results are obtained to validate the feasibility of the proposed strategy, using a PLECS-RT HIL platform and a DSP Microlab Box controller. In addition to the good dynamic performance of the proposed OSS-MPC, it is demonstrated by the HIL results that the control algorithm is capable of obtaining low total harmonic distortion (THD) in the output voltage for different conditions.

Keywords:

Subject: Engineering - Electrical and Electronic Engineering

1. Introduction

When power converters are utilised to supply electrical energy to islanded loads, in microgrids or distributed generation applications, typically an filter is connected at the converter outputs [1,2,3]. For instance, converters augmented by filters are used in applications such as uninterruptible power supplies (UPS) [4], energy storage systems [5], motor drives [6], microgrids [7], etc.

When SISO control tools are utilised, to design the control systems of power converters equipped with filters, typically two cascaded PI or PR control loops are required: an outer voltage control loop, and an inner current control loop [3,8]. The voltage loop computes the reference for the inner current loop, and the current loop computes the desired converter voltage to be synthesized by a pulse-width modulation (PWM) scheme. However, as discussed in [7], the cascaded interconnection of the voltage and current control loops has some drawbacks. First, because SISO design tools are used, the inner and outer loops are separately designed with different bandwidths to avoid cross-couplings between the dynamics of the voltage and current control loops (usually, the outer loop is one order of magnitude slower than the inner loop). This produces a relatively slower transient response. Second, the controllers must be carefully tuned because their parameters affect the system’s stability. To overcome the drawbacks of cascaded linear controllers, model predictive control schemes, which are MIMO systems have been recently proposed.

Model Predictive Control (MPC) has been garnering growing interest in the realm of power electronics converter applications. Most common applications include grid-connected converters, inverters with RL load, inverters with output LC filter, and high-performance drives [9]. MPC has several advantages such as simplicity for the inclusion of nonlinearities, simple treatment of constraints, the multivariable case can be easily considered, dead times can be compensated, etc [10]. On the other hand, the disadvantage of MPC is its relatively high computational load, particularly in power converter topologies where a large number of vectors are available. However, the exponential development in the processing power of microprocessors (such as digital signal processors and field-programmable gate arrays) has allowed the implementation of MPC algorithms in real-time platforms [11].

A wide variety of MPC algorithms for power electronics converters exist. An MPC algorithm can be considered, in general terms, as any algorithm that uses a model of the system to predict its future behaviour and select the most appropriate control action based on the solution to an optimal criterion [12]. The optimal criterion is evaluated in a cost function and can be, for example, tracking of the system state variables, minimising common-mode voltage, or reducing the converter switching frequency [12,13]. After the optimal criterion has been reached, and consequently the best possible solution to the optimisation problem has been obtained, the algorithm sends it to the converter to be synthesised.

MPC algorithms are classified according to the nature of the optimisation variable in the control problem. In broad terms, these algorithms for power electronics are classified as Direct MPC or Indirect MPC methods [13]. In direct MPC methods, the optimisation variable is an integer-valued vector representing the state of the converter switching devices. Conversely, in indirect MPC the optimisation variable is a real-valued vector representing the fundamental component of the converter output voltage or duty cycles.

Direct MPC methods are subdivided into three categories: optimal switching vector MPC (OSV-MPC), MPC with hysteresis bounds, and MPC with an implicit modulator. OSV-MPC, commonly named as Finite Control Set MPC (FCS-MPC) in the literature, was firstly proposed to control the output current of a two-level inverter connected to an RL load [14]. Since then, it has been applied to many converter topologies [9]. In this strategy, the converter switches are directly computed and sent to the converter. Thus, allowing direct manipulation of the controlled variables. The advantages of OSV-MPC are an intuitive design procedure, straightforward implementation and fast transient response [13]. However, they come at the cost of high computational complexity, particularly for multilevel power converters, and variable switching frequency due to the absence of a modulator [15].

Direct MPC methods with implicit modulator have been proposed to overcome the issue of variable switching frequency introduced by OSV-MPC while maintaining its advantages [16,17]. These strategies attempt to emulate the behaviour of pulse-width modulation techniques. In particular, Optimal Switching Sequence MPC (OSS-MPC) and Modulated MPC (M2PC) introduce the concept of variable switching time instants [13]. According to the concept of variable switching time instants, the position of the converter switches can change at any moment during a sampling interval. Then, the strategies compute a sequence of switch positions and their corresponding duty cycles to be applied during the next sampling interval. Thus, a fixed switching frequency is achieved resulting in a reduction of harmonic distortion [13]. However, M2PC is prone to suboptimality because the optimisation problem is solved in two stages: the first stage is to find the optimal switch positions and the second stage is to compute the duty cycles [18].

OSS-MPC avoid suboptimal solutions by computing the optimal sequence of switch positions and their corresponding duty cycles in one stage. The strategy was first introduced for power control of a grid-connected two-level inverter [17]. Then, the strategy was modified to be used in other converter topologies such as a three-level neutral-point-clamped (3L-NPC) inverter and vienna rectifier [19,20,21,22]. In [23], OSS-MPC was used for voltage control of an LC-filtered two-level inverter achieving low output voltage ripple and reduced harmonic content compared against other MPC methods (such as OSV-MPC). In this paper, the OSS-MPC presented in [22] is extended to three-level neutral-point-clamped (3L-NPC) inverters with output LC filter in standalone operation (such as UPS). The strategy uses a prediction model based on the improved Euler method to compute the future value of the load output voltage and inductor filter current. The predicted values are compared against the desired reference values in the cost function of an optimisation problem. The cost function penalizes the deviation between the measured values and the reference values, and also the control effort of the converter. The optimisation problem is solved offline to compute an optimal switching sequence to be applied by the converter. The optimal switching sequence is then transformed into a three-phase reference signal which is used in an optimisation problem to compute an optimal common-mode voltage to balance the DC-link capacitors of the converter. The common-mode voltage is then added to the three-phase reference signal and the resulting optimal three-phase reference is sent to an In-Phase Disposition PWM scheme to generate the pulses of the switching devices.

2. The 3L-NPC Inverter

The 3L-NPC was the first multilevel converter topology, proposed by the group of Akagi in [24]. It was introduced around 1980 to reduce the pulsating torque and harmonic losses on AC drives; thus, improving the efficiency and reducing the cost of the system. Nowadays, this converter topology is the standard for medium and high-voltage applications [25,26]. In the mining industry, for example, 3L-NPC converters are used in variable frequency drives (VFD) for long belt-conveyor systems carrying ore [27].

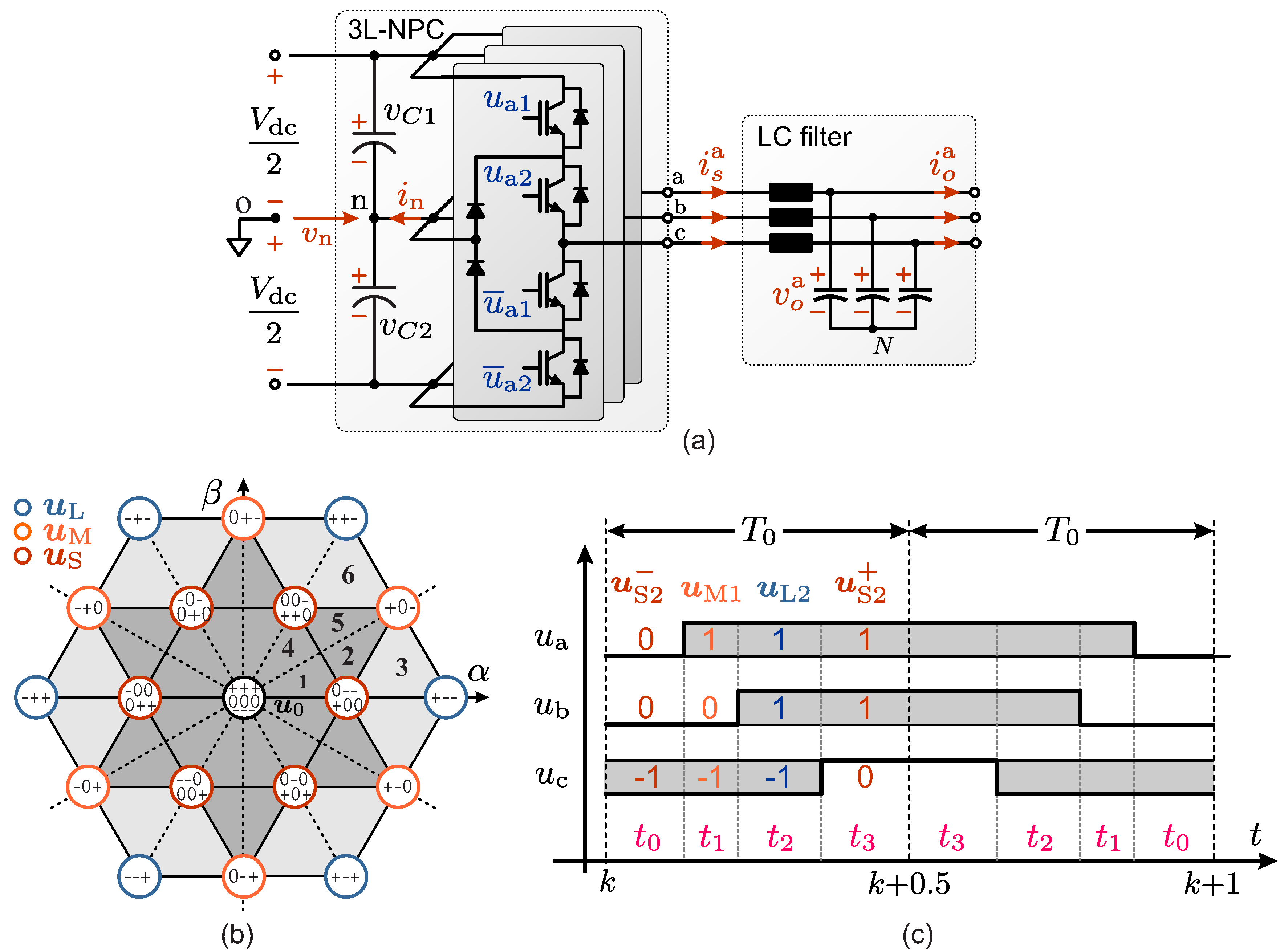

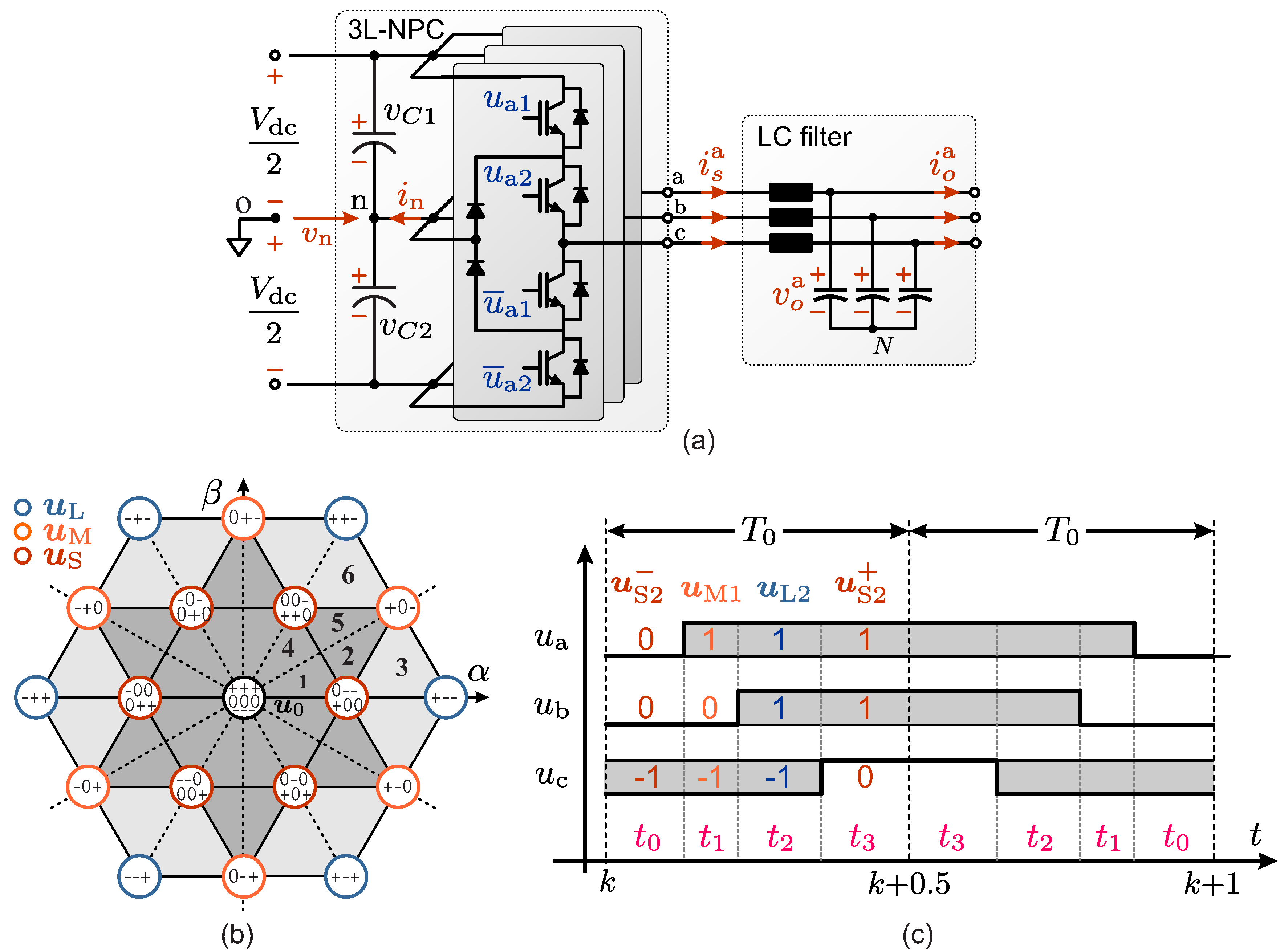

As shown in the circuit diagram in Figure 1(a), the 3L-NPC converter is composed of four switches and two clamped diodes per leg, producing a total of 27 three-phase switching states for the whole converter, where . As depicted in Figure 1(b), these switching states produce 19 non-redundant and 8 redundant switching vectors (SVs) in the frame, where , and is the amplitude invariant -to- transformation [28].

According to the circuit diagram depicted in Figure 1(a), the inverter voltages are given by

where , and is the NP-voltage. Using the transformation , the inverter voltages (1) in the stationary frame can be expressed as:

On the other hand, for a three-phase load with a floating neutral, the NP-voltage evolves as a function of the NP-current according to:

Therefore, for a given output current , as shown in (3), only small- and medium-size SVs, and in fig:NPC1](b) respectively, can affect the NP-voltage [29]. However, to balance the NP voltage, small SVs play a significant role because the redundancy of each SV drives an NP-current of the same amplitude but in the opposite direction. This tendency impacts but not when the capacitors are balanced with a negligible voltage ripple, i.e., .

To synthesize a desired inverter output voltage, the three nearest SVs are typically employed in carrier-based and space vector PWM techniques [29,30]. Due to the presence of redundancies, several switching sequences (or switching patterns) can synthesize the desired output voltage. Therefore, the generation of switching sequences can be used for several purposes, such as to reduce the switching frequency and to minimize the NP-voltage ripple [29].

Figure 1.

3L-NPC converter: (a) topology; (b) space of switching vectors; (c) 7S-SS for the region .

Figure 1.

3L-NPC converter: (a) topology; (b) space of switching vectors; (c) 7S-SS for the region .

Based on the above analysis, the seven-segment switching sequence (7S-SS) [29] will be adopted in this work to implement the OSS-MPC strategy for voltage and current control. This switching pattern consists of four SVs, which are arranged in such a way that the transition between two adjacent switching states demands only one switching action. Additionally, each switching period is split into two sub-cycles of duration , in which the disposition of the second sub-cycle is a reversal of the arrangement of the first [29], as shown in the example in fig:NPC1](c). Furthermore, the first sub-cycle starts with an N-type small-size SV () and ends with the P-type redundancy (). Therefore, each 7S-SS candidate can be defined accordingly as:

where is the time in which the ith switching vector is synthesized by the converter, as depicted in Figure 1(c).

Since the twelve internal regions [highlighted in grey in fig:NPC1](b)] have two N-type small-size SVs, each of them is further partitioned in two subregions to reduce the NP-voltage ripple [29]. Thus, to determine which dominant N-type small-size SV should be utilised to assemble the desired switching sequence, the space of SVs is divided in 36 regions as shown in fig:NPC1](b). Then, according to the OSS-MPC principles, a 7S-SS candidate is denoted as , where .

3. Cascaded OSS-MPC Strategy for Voltage and Current Control

In this work, a cascaded OSS-MPC scheme will be employed to simultaneously control the voltage and current at an LC filter, while maintaining balanced voltages at the capacitors of the DC-link in a 3L-NPC converter. The overall controller is a predictive control scheme based on the solution to two cascaded optimisation problems.

The proposed control scheme is shown in Figure 2. The first optimisation problem —hereinafter called the outer optimisation loop— computes the optimal switching vectors sequence and duty cycles that minimize a cost function. The cost function is designed to track the desired values of the state vector and minimize the control effort of the converter. The second optimisation problem —hereinafter called the inner optimisation loop— computes an optimal common-mode injection signal (see bottom left-hand side of Figure 2). The common-mode injection signal is designed to balance the neutral-point voltage between the DC-link capacitors.

3.1. Continuous-time model

Let us consider a three-phase 3L-NPC connected to an LC filter, as shown in Figure 1(a). The system of differential equations describing the dynamics of the LC filter can be written as:

Assuming that the DC-link NP-voltage is balanced (i.e., ), the converter output voltage in (2) is equal to . Moreover, by rearranging the equations and define the state, input and disturbance vectors as , , and (The superscripts in the vectors will be avoided to simplify the notation). The state-space model of the AC side dynamics is then:

Matrices , , and contain the parameters of the filter and matrix is the identity matrix.

The resistance, inductance, and capacitance matrices are defined as follows:

The dimensions of the system matrices are , , , , , and .

3.2. Discrete-time model

MPC algorithms use the discrete-time mathematical model of the system, to make predictions of the state vector trajectory, then utilise the predicted values in an optimisation problem and compute the best control action that fulfils the control objectives.

Typically, for the discrete implementation of the continuous-time model, the forward-Euler method is applied. However, as extensively discussed in [31,32], the forward Euler methodology is suitable for implementing nested control loops when two MPC stages are used. For this sort of application an outer MPC algorithm is implemented to regulate the voltages and an inner MPC is utilised to regulate the converter’s output currents [31]. Nevertheless, when nested MPC loops are used, two cost functions are required and a global optimum is not necessarily reached (see [32]).

To reach a global optimum, a single cost function for the load voltage and converter’s output current is required; therefore, with this approach, a single MPC algorithm is required to regulate the voltage and currents in a single optimisation stage (see Figure 2). However, as extensively discussed in [32], when nested voltage-current control loops are implemented in a single stage, the discrete model implemented using the forward Euler method may produce a lack of causality and controllability in the MPC controller; therefore, other continuous to discrete approximations, for instance, the improved Euler method [33] or a two-steps control horizon [32] are recommended. In this work, the discretization of the continuous-time model is performed using the improved Euler method [33]. This is further discussed in this section.

3.2.1. Forward Euler-Based Discrete Time Model

It is assumed in this work that a 7S-SS is applied to the converter during every switching cycle. Considering the forward Euler method, the instantaneous trajectory of the state vector when a switching vector is applied can be computed as:

where is the index for the switching vectors of the sequence. The instantaneous evolution of the state vector prediction at the end of the sub-cycle corresponds to its average trajectory when the seven-segment SS defined by (4) (see [20]) is applied to the system:

To simplify the analysis, every subinterval slope is approximated using the values of the state and disturbance vector at the sampling instant k as . Therefore, the prediction of the average trajectory can be expressed as:

where , , and . Because for any N-type seven-segment SS, , and , the duty cycles and can be combined as which is the duty cycle for the small vectors of the sequence [20]. Then, the following linear representation of the average trajectory can be stated as:

where the dwell-time vector and switching matrix are defined as:

3.2.2. Improved Euler-Based Discrete Time Model

The improved Euler method is a second-order Runge-Kutta method to compute the solution of ordinary differential equations [33]. In this method, the weighted average of the approximations to the derivative at intermediate points on the solution curve is computed. Specifically, the improved Euler method uses the extreme points of the solution interval (i.e., kth and ()th points). Higher-order Runge-Kutta methods use more intermediate points to increase the accuracy of the solution.

Once again, it is assumed that a 7S-SS is applied by the converter during the complete switching cycle. Considering the improved Euler method, the instantaneous evolution of the state vector is given by the following equation:

The average slope is multiplied by because it is the time length between predictions in the interval and predictions in the interval . To simplify (14), some assumptions about the states and inputs used for computational purposes are required. Firstly, the slope of the system at the kth time instant is computed with the values measured at the time instant k (i.e., ). Secondly, the slope at the ()th time is computed with the predicted state vector using the forward Euler approximation defined by (12). The switching sequence applied is the same of time instant k (i.e., ). The disturbance vector is assumed to be constant during the switching cycle, but different between switching cycles (i.e., ). Considering these assumptions, the state vector trajectory is described by:

The slopes and are described by the following equations:

Replacing in (16b), the expression for the slope is obtained as follows:

Then, the average trajectory of the state vector, using the improved Euler method, is computed as:

Replacing (16a) and (17) into (18), and after some algebraic manipulations, the following expression is obtained:

Equation (19) is useful when an observer-predictor computes , and the difference between and is sufficiently large. However, if it is assumed that then the average prediction model is simplified to:

Discrete-time model in (20) can be written as the linear representation (12) with , , and . It is straightforward to show that the discrete-time model obtained in (20) is controllable. Thus, the proposed controller can control the converter currents and the capacitor voltages using a single cost function, avoiding a nested control loop structure.

4. C-OSS-MPC formulation

4.1. Reference vector

The objective of the controllers is to keep the voltage of the LC filter capacitors as sinusoidal waveforms. Thus, the reference voltage vector is

Where is the magnitude of the reference voltage vector, and is the fundamental frequency of the output voltage (). The reference current is obtained as a function of the reference voltage. Replacing the reference voltage vector into the dynamic equation of the output voltages yields:

Solving the equation for we obtain

where the matrix is defined as

It is desirable to constrain the reference current to a maximum value, . When the amplitude of the reference current is less than the specified limit, the reference current vector is described by equation (23). In the other case, the reference current vector is saturated at . Therefore, the constrained reference current is represented by the following piece-wise function:

Thus, the reference state vector is

4.2. Cost function

At the heart of the MPC strategy lies the cost function. In the cost function, the variables related to the control objectives are weighted to choose the best possible action. In FCS-MPC schemes, the cost function is most commonly designed to minimize the tracking error [34]; however, it has been shown that FCS-MPC strategies without penalization of the control effort are equivalent to quantised dead-beat controllers [15]. Deadbeat controller features fast dynamic response [35] but they have poor robustness against model mismatches, parameter uncertainties, and noise on measured variables [36]. To alleviate the unwanted effects of deadbeat controllers, the control effort is usually penalised in the cost function [35]. In the control proposed in this work, the outer MPC loop has two objectives: minimise the tracking error between the state vector and its reference, and penalize the control effort. Therefore, the following cost function is defined:

The positive-definite matrix = diag(,,,) is used to trade-off the control objectives of the state vector tracking. Similarly, the weighting factor is used to penalize the control effort. The optimisation variable of the problem is the average switching vector, . The average switching vector is the product between the switching matrix and duty cycle vector as .

Firstly, the term of the cost function used to penalize the reference tracking error will be reformulated as a function of the average switching vector . Replacing (12) in (27), yields:

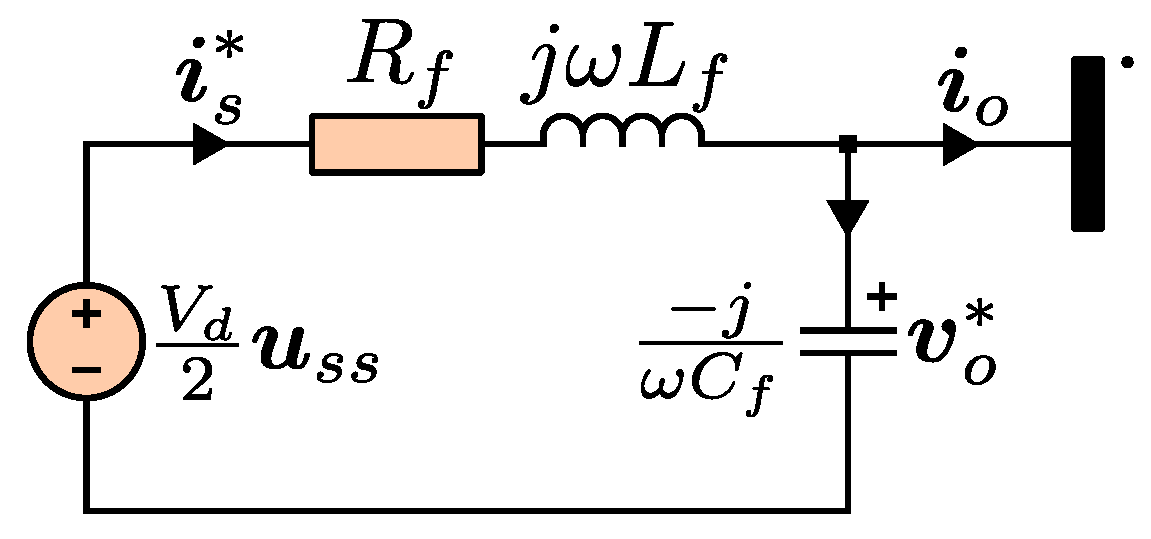

The second term of the cost function in eq. (27) has the vector . Vector is the steady-state control action. The steady-state control action is the input vector needed to drive the system towards the steady-state solution. The expression for this vector is obtained by solving the circuit of Figure 3 for . The steady-state control input is defined as:

Finally, the cost function for the optimisation problem can be written as:

4.3. Optimisation problem

In OSS-MPC, the optimal switching sequence (OSS) is obtained by solving an optimisation problem. The solution must comply with constraints such that the sum of leg duty cycles is equal to one, and each duty cycle must be equal to or greater than zero. Therefore, the optimisation problem to be solved is the following:

The optimisation problem has the same form as the one solved in [22]. Therefore, the same optimiser will be used. Thus, the usual strategy to solve MPC problems with 3L-NPC converters of evaluating each region of the space of vectors is avoided.

5. Solution to the outer optimisation problem

In this section, the relaxed optimisation problem will be solved to obtain the optimal switching vector sequence and its corresponding duty cycles to be applied during the next sampling instant. Two cases of the problem are distinguished; First, the linear modulation stage where the duty cycles are positive. Second, the overmodulation stage where the duty cycle of the small switching vectors becomes negative.

5.1. Non-negative duty cycles: the linear modulation stage

5.1.1. Relaxed optimisation problem

To relax the optimisation problem, the inequality constraints are removed from the problem formulation. The relaxed optimisation problem is then stated as

Expanding the cost function yields:

The following expression is obtained,

where is the modified weight matrix, . The elements of the switching matrix are the vectors of the switching sequence:

5.1.2. Solution of the relaxed optimisation problem

Considering the equality constraint of the relaxed optimisation problem, the duty cycles for the small switching vectors, as a function of the remaining duty cycles, can be written as:

An auxiliar variable, , is defined to eliminate the dependent variable from the optimisation vector :

The relationship between and is the following:

Then, and . The cost function in terms of is

Computing the gradient of J with respect to and making it equal to zero, yields:

Solving the equation for yields:

The unconstrained control action () is defined as:

Now, it is required to map the solution back to its original variables. Replacing (42) in (38), yields:

The optimal duty cycles for the linear modulation stage are computed using the () matrix:

where is the determinant of matrix product :

Where denotes the cross product.

6. Optimal Solution

In the previous section, the relaxed solution to the optimisation problem was calculated. The relaxed duty cycles vector is the local solution for each region of the control hexagon . The relaxed solution computed with (Section 5.1.1) fulfills the equality constraint . Thus, all regions can be mapped onto in the -plane. However, only one region fulfils the non-negativity constraint [20]. The non-negativity constraint can then be considered in the solution with a simple methodology (as reported in [20,22]). The methodology introduced therein also reduces the computational burden avoiding the search over all 24 regions of the control region to only four. The methodology will be explained in this section.

Firstly, considering the -plane shown in Figure 4(a) with the Space of Vectors of the 3L-NPC is divided into 12 regions. The algorithm seeks the region where is located, and then the three sectors in that region are evaluated in the control algorithm. Given that is the desired solution of the optimisation problem, its angle is used to find the optimal region in the plane. The optimal sector is obtained from the following equation:

When the optimal sector is calculated, the duty cycles of the switching sequences contained in it are evaluated. The sector whose duty cycles comply with the non-negativity constraint is the optimal sector, and thus, the optimal switching sequence is found.

Figure 4.

Control region of the 3L-NPC. (a) Hexagon divided into 12 sectors to reduce the computational burden of the OSS-MPC algorithm, and (b) close-up look into sectors -.

Figure 4.

Control region of the 3L-NPC. (a) Hexagon divided into 12 sectors to reduce the computational burden of the OSS-MPC algorithm, and (b) close-up look into sectors -.

The conventional enumeration algorithm can be reduced to only 3 regions after the sector has been identified. Each sector has three candidate switching sequences, but only one of them fulfills the non-negativity constraint. Thus, the optimal pair is found evaluating the non-negativity condition over the duty cycles vector of each candidate region. However, if falls outside the control region (e.g., see in Figure 4(b)) then none of the candidate switching sequences fulfil the non-negativity constraint.

The aforementioned case occurs during a transient operation. The candidate switching sequence is then reduced to one and is built by the medium and large switching vectors belonging to the only outer region that intersects the optimal sector. The case is further analyzed in the next subsection.

6.1. Handling the negative duty cycles: the overmodulation stage

6.1.1. Relaxed optimisation problem

The unconstrained average switching vector goes outside the hexagon, thus the duty cycle for the small switching vector becomes negative. Defining , the optimisation variable becomes

Consider the equality constraint

Notice that one of the two optimisation variables is dependent. Thus, if we set to be dependent of , we can find an auxiliary vector to reduce the equality-constrained optimisation problem into an unconstrained optimisation problem

Then, and . The cost function is

6.1.2. Solution of the relaxed optimisation problem

The unconstrained optimisation problem is solved by setting to zero the derivative of the cost function with respect to the optimisation variable

Solving it for yields:

The matrix corresponds to a scalar multiplied by the identity matrix. Bearing on mind that , the optimal duty cycle is

Notice that the denominator of is the length between a large and medium vector in the hexagon frontier (see Figure 4(b)), thus:

Then, the optimal solution for the overmodulation stage is:

7. Inner optimisation problem

The objective of the inner optimisation loop is to compute an optimal common-mode signal to balance the DC-link capacitors of the 3L-NPC converter. The strategy assumes that a PWM stage is used to synthesize the solution obtained from the outer optimisation loop. To this end, the optimal SS is mapped into a three-phase reference signal obtained as [22]:

in which are the three-phase switching states that produce the optimal SS. The optimal common-mode signal is the solution to the following optimisation problem:

in which is the reference value of the DC-link NP-voltage, is the discrete-time model of the NP voltage and is a time-varying saturation level which represents the voltage available in the DC-link. The solution to the optimisation problem yields the following equation:

where and are determined at each sampling instant according to:

where . The time-varying saturation level is defined as:

Finally, the three-phase reference signals sent to the PWM modulator are:

For a more throughout explanation of the inner optimisation loop, the reader is referred to [22].

8. Hardware-in-the-Loop (HIL) Results

In this section, Hardware-in-the-Loop (HIL) results are shown to validate the proposed controller. The 3L-NPC converter, LC filter and loads are emulated using PLECS-RT box 1 HIL platforms with a time-step of 5 s. The control system is separately implemented using a dSPACE MicroLabBox platform. This dSpace controller is equipped with a Freescale QorIQ P5020 dual-core 2 GHz processor, for number crunching, and a Kintex-7 XC7K325-T FPGA. The FPGA handles the AD conversion, performs an In-Phase Disposition PWM strategy and implements a dead time of 1 s for each switching device; the HIL system is shown in Figure 5(a). The processor computes the Clark transform of the measured three-phase variables, executes the optimisation algorithm, and computes the appropriate three-phase reference signals for the modulator. The loads considered for the study are a three-phase resistive load bank and a nonlinear load implemented using a three-phase diode rectifier with a capacitor and resistor connected in parallel at the DC side, as shown in Figure 5(b). The parameters of the system are shown in Table 1 and are similar to those used in a previous work (see [23]).

The performance of the controllers is evaluated using the following goodness factors: RMS error (RMSE), percentage of voltage error (Ev) and total harmonic distortion (THD). The percentage of error is defined as follows:

where is the set of indices of the measurements vector, and is the total number of elements in the vector. is the period of the fundamental frequency, and is the period of the sampling frequency. Whenever the desired reference amplitude is unknown, the root-mean-square error (RMSE) will be used. The RMS error is defined as follows:

A one-step delay compensation is carried out to compensate for the computational delay introduced by the digital platform. The state vector is computed using (20) with the values measured at the instant, and the switching sequence applied during the previous switching interval. The voltage reference is computed shifting the phase of the reference signal one step ahead. The load output current is estimated using the Lagrange extrapolation technique. The Lagrange extrapolation technique uses the actual and past measurements of the signal to estimate its future value. The load output current is computed as follows [37]:

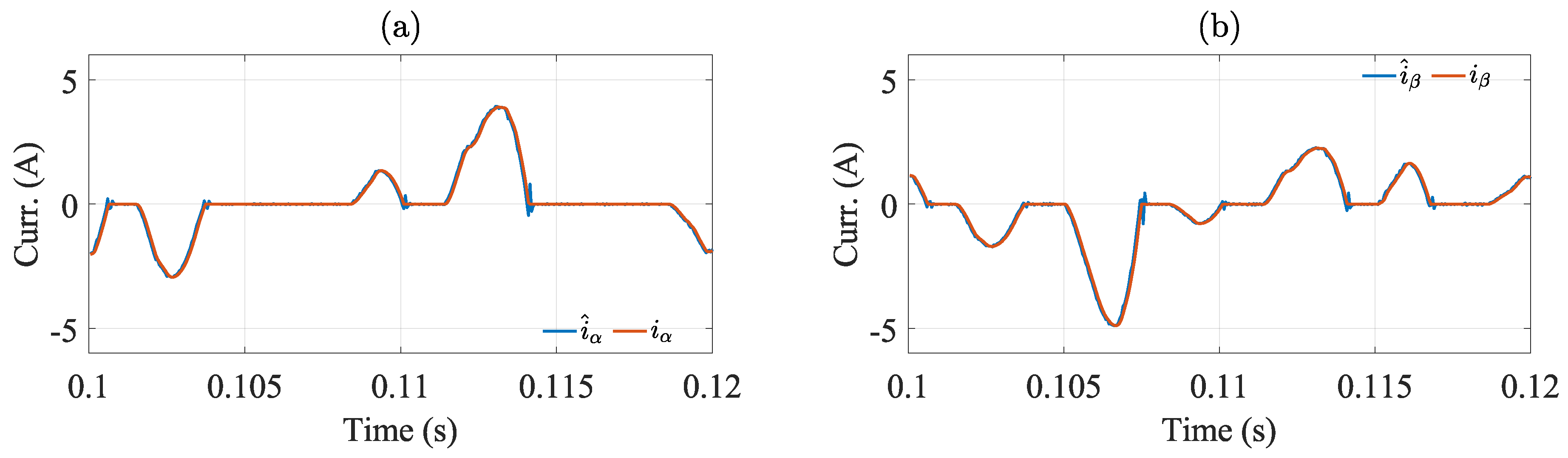

The estimated load output current has an RMS error of 0.0603 [A] in the -component, and 0.0640 [A] in the -component for the worst-case scenario (nonlinear load). The estimated and measured load output current are shown in Figure 6. As shown in this figure, the estimated current tracks relatively well the measured current.

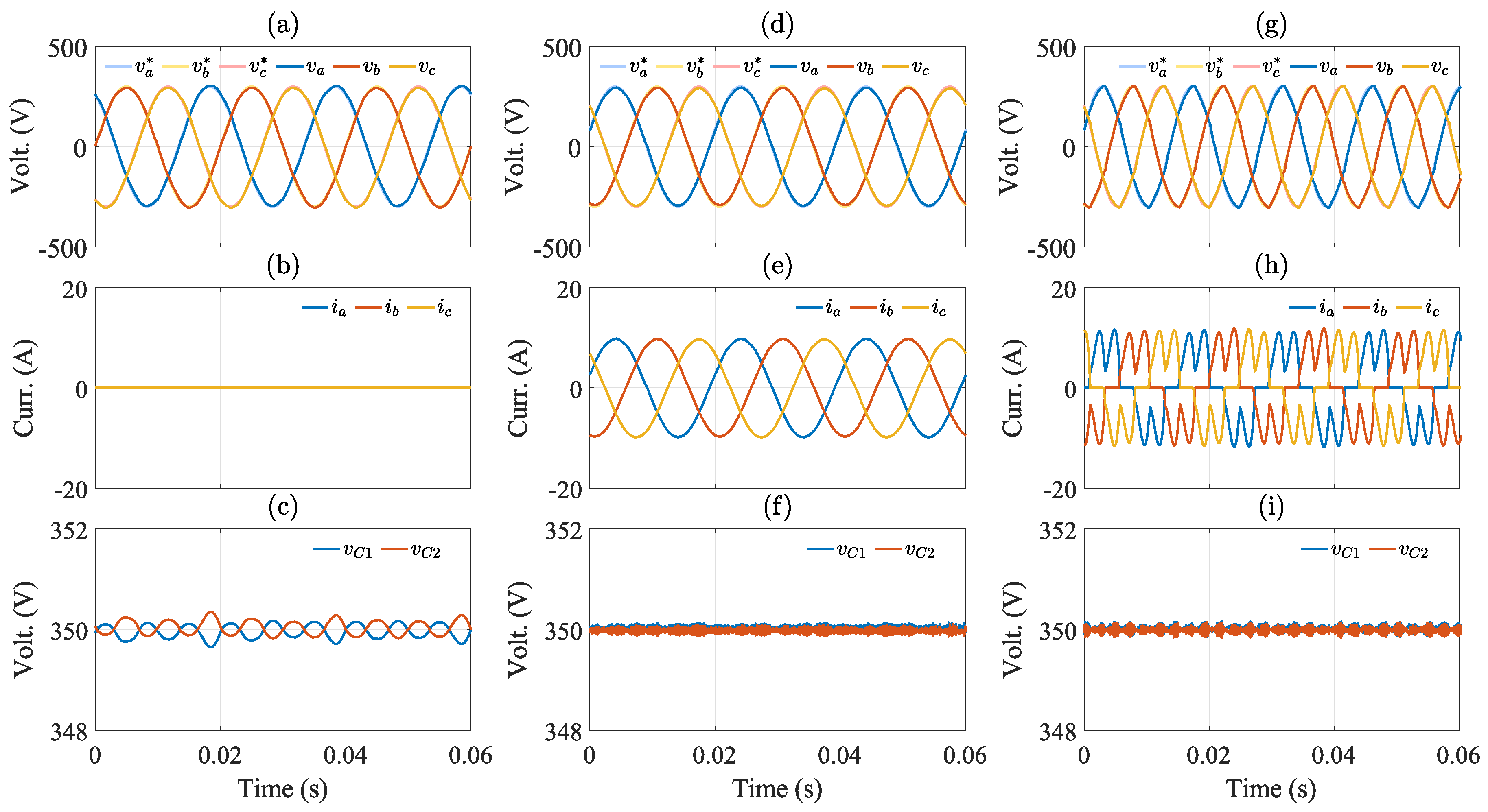

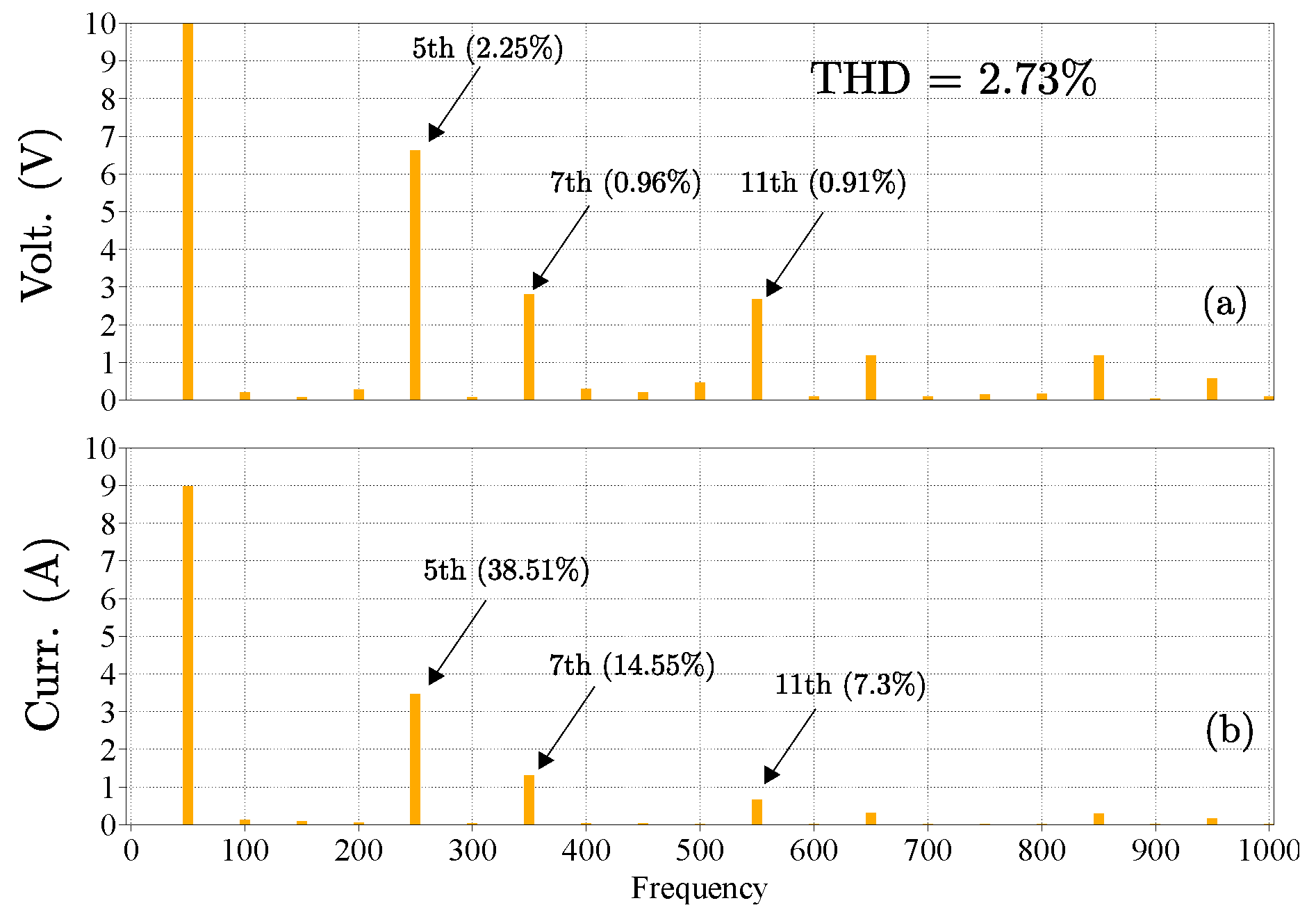

In Figure 7(a), the output voltages when the system operates without load are shown. The reference voltage has an amplitude of 300 [V] with a frequency of 50[Hz]. For this condition, the load output voltages have a voltage error of 2.04% and a THD of 1.74%. Then, a three-phase resistive load is connected as in Figure 7(d). In this condition, the voltage error is 2.05% and the THD is 1.03%. When a nonlinear load is connected, as in Figure 7(g), the voltage error is 2.83%. The harmonic spectrum for the load output voltage and load output current are shown in Figure 8(a)-(b). The voltage THD in this case is 2.73% with the presence of 5th and 7th harmonics, which are produced by the bridge rectifier. In Figure 7(b)-(h) the load output current is shown for the three aforementioned cases. Finally, in Figure 7(c)-(i), the DC-link capacitor voltages are shown. The control strategy is capable of maintaining the DC-link voltages balanced and well regulated, for all operating conditions with very small oscillations.

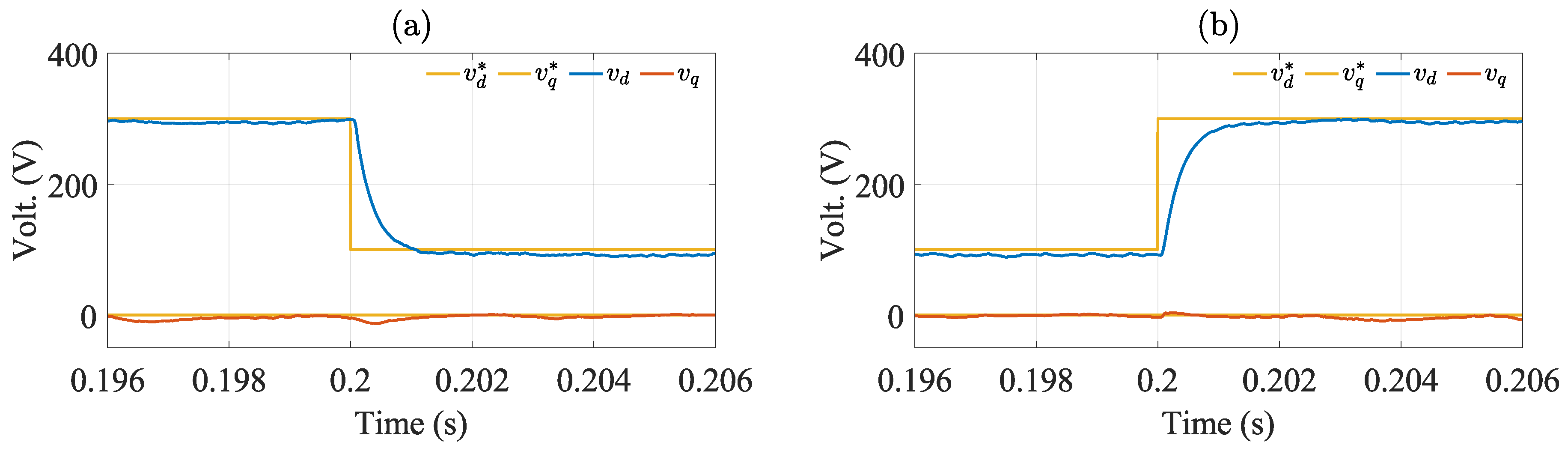

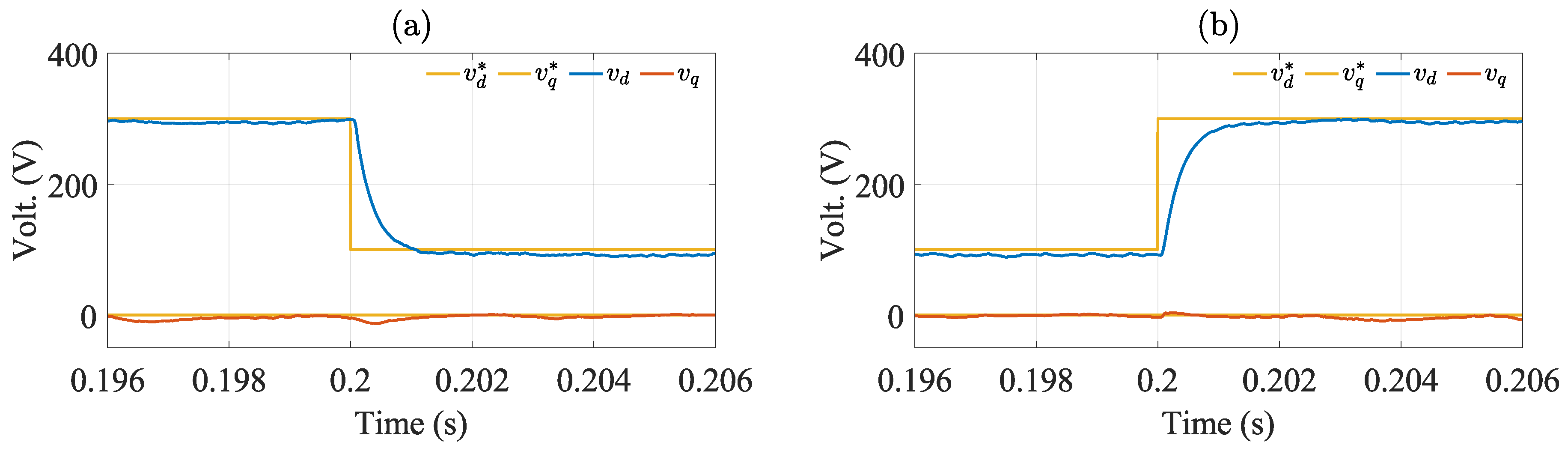

The transient operation of the controlled system is studied in Figure 9 considering changes in the reference voltage amplitude. The variables are presented in the synchronous reference frame to verify the settling time of the load output voltage.

The settling time is computed as the time required by the output voltage to reach and stay within 5% of the desired voltage. In Figure 9(a) the reference voltage receives a step variation from 300 [V] to 100 [V] at t = 0.2 [s]. The voltage error amounts to 5.98% under steady-state conditions. The rise in voltage error results from the reduction in the amplitude of the reference voltage. In Figure 9(b), the reference voltage varies from 100 [V] to 300 [V] at t = 0.2 [s]. In this case, the load output voltage manages to stay within the band of 5% around the desired voltage. Thus, the settling time is 1.03 [ms] approximately.

Notice that a relatively low steady-state error is presented in the HIL results shown in Figure 9 a and b. This small steady-state error is produced because there is not an integrator in the MPC algorithm [38,39]. If steady state error is a must, then the state space matrix [see (7)] must be augmented with additional states to represent the integrator [38]; however, this topic is considered outside the scope of this work.

Figure 9.

Transient operation of the system for reference voltage step. (a) voltage step from 300 [V] to 100 [V], (b) voltage step from 100 [V] to 300 [V].

Figure 9.

Transient operation of the system for reference voltage step. (a) voltage step from 300 [V] to 100 [V], (b) voltage step from 100 [V] to 300 [V].

Figure 10 shows the operation of the system for a load step. A dip occurs in the load output voltage, as shown in Figure 10(a), and takes 1 [ms] approximately to recover. Notice that there is a sudden increase in the inductor reference current to 10 A approximately, and the current features a fast dynamic response to the step change.

The cost function of (30) has two terms: the first term penalizes the deviation of the system states from a reference vector and the second term penalizes the control effort of the converter. The control effort is penalized in the cost function by the deviation between the optimisation variable and the steady-state control action . The weight of this deviation on the optimisation problem is set by the parameter . Increasing will lead the converter’s response to move closer to open-loop operation since depends only on the load reference voltage and load output current. The system’s performance with a logarithmic variation of the parameter is shown in Figure 11. The results are obtained considering a three-phase resistive load at the LC filter terminals. The best trade-off in terms of voltage error between open-loop and closed-loop operation of the converter is achieved when , as shown in Figure 11(a). When is increased, the response of the system tends toward which does not penalize the voltage error. Thus, the voltage error increases.

As shown in Figure 11(b), the voltage THD presents slight variations around 1%, as shown in Figure 11(b). The system’s transient response is also dependent on the value of . A trade-off between settling time and overshoot must be reached, as shown in Figure 12. Increasing up to 100 will reduce the settling time of the system but increase the voltage overshoot. However, for , the system response will present a damped sinusoidal oscillation which increases the settling time.

Figure 11.

System performance over variation of .

Figure 12.

Transient operation of the system for different values of .

9. Conclusions

In this paper, an Optimal Switching Sequence MPC algorithm was proposed for the three-level neutral-point-clamped inverter with an output LC filter. The strategy is an extension of the Cascaded Optimal Switching Sequence MPC proposed in the literature for current and direct power control of active front-end 3L-NPC inverters. The control objectives of the algorithm were two: (1) achieve good tracking performance for the LC filter variables, and (2) maintain balanced the neutral-point voltage between the DC-link capacitors of the converter. To achieve the objectives, the strategy solves two cascaded optimisation problems. The first optimisation problem -called the outer optimisation loop- computes the optimal sequence of switching vectors and their corresponding duty cycles to achieve the objectives related to tracking the AC side variables. Then, the optimal solution of the outer optimisation loop is used by an inner optimisation loop to compute an optimal common-mode signal designed to balance the neutral-point voltage between the DC-link capacitors. A discrete-time model based on the improved Euler discretization method was used to predict the future values of the state vector trajectory. Notice that this methodology allows the implementation of a single-stage MPC algorithm to regulate the load voltage and the converter output current.

Experimental results are provided to validate the performance of the proposed strategy using PLEXIM Hardware-in-the-Loop (HIL) platform RT Box 1 to emulate the power electronics stage, and the control algorithm was executed by the dSPACE MicroLabBox control platform. Three cases were considered in steady-state operation: (1) system performance without load, (2) system performance with linear load, and (3) system performance with nonlinear load. In all cases, the MPC algorithm is capable of achieving good tracking of the load voltage reference with a small error and low THD. Also, the strategy is capable of maintaining well-balanced voltages at the DC-link capacitors.

Author Contributions

Conceptualization, Felipe Herrera, Andrés Mora, Roberto Cárdenas and Jose Rodriguez; Formal analysis, Felipe Herrera, Andrés Mora, Roberto Cárdenas, Matías Díaz and Marco Rivera; Funding acquisition, Roberto Cárdenas, Matías Díaz and Jose Rodriguez; Investigation, Felipe Herrera, Jose Rodriguez and Marco Rivera; Methodology, Andrés Mora and Roberto Cárdenas; Project administration, Roberto Cárdenas; Resources, Matías Díaz; Software, Felipe Herrera, Matías Díaz and Marco Rivera; Supervision, Andrés Mora and Roberto Cárdenas; Validation, Felipe Herrera, Andrés Mora and Roberto Cárdenas; Writing – original draft, Felipe Herrera and Andrés Mora; Writing – review & editing, Andrés Mora, Roberto Cárdenas, Matías Díaz, Jose Rodriguez and Marco Rivera. All authors have read and agreed to the published version of the manuscript.

Funding

This research was funded by Fondecyt grants numbers 1221392 and 1231030. The support of Fondequip EQM210117 and Basal grant FB0008 is kindly acknowledged.

Conflicts of Interest

The authors declare no conflict of interest. The funders had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript; or in the decision to publish the results.

Abbreviations

The following abbreviations are used in this manuscript:

| 7S-SS | Seven Segments Switching Sequence |

| DC | Direct Current |

| AC | Alternate Current |

| FPGA | Field Programmable Gate Array |

| FCS-MPC | Finite Control Set Model Predictive Control |

| Modulated Model Predictive Control | |

| HIL | Hardware in the Loop |

| LC-filter | Inductance Capacitor Filter |

| MIMO | Multiple-Input Multiple-Output |

| MPC | Model Predictive Control |

| NPC | Neutral Point Clamped |

| OSS | Optimal Switching Sequence |

| OSV | Optimal Switching Vector |

| PWM | Pulse Width Modulation |

| RT | Real Time |

| SISO | Single-Input Single-Output |

| THD | Total Harmonic Distortion |

| UPS | Uninterruptible Power Supply |

| VFD | Variable Frequency Drives |

References

- Cárdenas, R.; Espina, E.; Clare, J.; Wheeler, P. Self-Tuning Resonant Control of a Seven-Leg Back-to-Back Converter for Interfacing Variable-Speed Generators to Four-Wire Loads. IEEE Transactions on Industrial Electronics 2015, 62, 4618–4629. [Google Scholar] [CrossRef]

- Espina, E.; Llanos, J.; Burgos-Mellado, C.; Cárdenas-Dobson, R.; Martínez-Gómez, M.; Sáez, D. Distributed Control Strategies for Microgrids: An Overview. IEEE Access 2020, 8, 193412–193448. [Google Scholar] [CrossRef]

- Loh, P.C.; Newman, M.; Zmood, D.; Holmes, D. A comparative analysis of multiloop voltage regulation strategies for single and three-phase UPS systems. IEEE Transactions on Power Electronics 2003, 18, 1176–1185. [Google Scholar] [CrossRef]

- Cortes, P.; Ortiz, G.; Yuz, J.I.; Rodriguez, J.; Vazquez, S.; Franquelo, L.G. Model Predictive Control of an Inverter With Output LC Filter for UPS Applications. IEEE Transactions on Industrial Electronics 2009, 56, 1875–1883. [Google Scholar] [CrossRef]

- Alhosaini, W.; Zhao, Y. A Model Predictive Voltage Control using Virtual Space Vectors for Grid-Forming Energy Storage Converters. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC); 2019; pp. 1466–1471. [Google Scholar] [CrossRef]

- Xue, C.; Zhou, D.; Li, Y. Finite-Control-Set Model Predictive Control for Three-Level NPC Inverter-Fed PMSM Drives With LC Filter. IEEE Transactions on Industrial Electronics 2021, 68, 11980–11991. [Google Scholar] [CrossRef]

- Dragičević, T. Model Predictive Control of Power Converters for Robust and Fast Operation of AC Microgrids. IEEE Transactions on Power Electronics 2018, 33, 6304–6317. [Google Scholar] [CrossRef]

- Diaz, M.; Cardenas, R.; Espinoza, M.; Rojas, F.; Mora, A.; Clare, J.C.; Wheeler, P. Control of Wind Energy Conversion Systems Based on the Modular Multilevel Matrix Converter. IEEE Transactions on Industrial Electronics 2017, 64, 8799–8810. [Google Scholar] [CrossRef]

- Vazquez, S.; Leon, J.I.; Franquelo, L.G.; Rodriguez, J.; Young, H.A.; Marquez, A.; Zanchetta, P. Model Predictive Control: A Review of Its Applications in Power Electronics. IEEE Industrial Electronics Magazine 2014, 8, 16–31. [Google Scholar] [CrossRef]

- Rodriguez, J.; Cortes, P. Model Predictive Control. Predictive Control of Power Converters and Electrical Drives, 2012; 31–39. [Google Scholar] [CrossRef]

- Kouro, S.; Perez, M.A.; Rodriguez, J.; Llor, A.M.; Young, H.A. Model Predictive Control: MPC’s Role in the Evolution of Power Electronics. IEEE Industrial Electronics Magazine 2015, 9, 8–21. [Google Scholar] [CrossRef]

- Kouro, S.; Cortes, P.; Vargas, R.; Ammann, U.; Rodriguez, J. Model Predictive Control-A Simple and Powerful Method to Control Power Converters. IEEE Transactions on Industrial Electronics 2009, 56, 1826–1838. [Google Scholar] [CrossRef]

- Karamanakos, P.; Liegmann, E.; Geyer, T.; Kennel, R. Model Predictive Control of Power Electronic Systems: Methods, Results, and Challenges. IEEE Open Journal of Industry Applications 2020, 1, 95–114. [Google Scholar] [CrossRef]

- Rodriguez, J.; Pontt, J.; Silva, C.A.; Correa, P.; Lezana, P.; Cortes, P.; Ammann, U. Predictive Current Control of a Voltage Source Inverter. IEEE Transactions on Industrial Electronics 2007, 54, 495–503. [Google Scholar] [CrossRef]

- Karamanakos, P.; Geyer, T. Guidelines for the Design of Finite Control Set Model Predictive Controllers. IEEE Transactions on Power Electronics 2020, 35, 7434–7450. [Google Scholar] [CrossRef]

- Tarisciotti, L.; Zanchetta, P.; Watson, A.; Clare, J.; Degano, M.; Bifaretti, S. Modulated model predictive control (M2PC) for a 3-phase active front-end. In Proceedings of the 2013 IEEE Energy Conversion Congress and Exposition; 2013; pp. 1062–1069. [Google Scholar] [CrossRef]

- Vazquez, S.; Marquez, A.; Aguilera, R.; Quevedo, D.; Leon, J.I.; Franquelo, L.G. Predictive Optimal Switching Sequence Direct Power Control for Grid-Connected Power Converters. IEEE Transactions on Industrial Electronics 2015, 62, 2010–2020. [Google Scholar] [CrossRef]

- Karamanakos, P.; Nahalparvari, M.; Geyer, T. Fixed Switching Frequency Direct Model Predictive Control With Continuous and Discontinuous Modulation for Grid-Tied Converters With LCL Filters. IEEE Transactions on Control Systems Technology, 2020; 1–16. [Google Scholar]

- Xu, B.; Liu, K.; Ran, X. Computationally Efficient Optimal Switching Sequence Model Predictive Control for Three-Phase Vienna Rectifier Under Balanced and Unbalanced DC Links. IEEE Transactions on Power Electronics 2021, 36, 12268–12280. [Google Scholar] [CrossRef]

- Mora, A.; Cárdenas-Dobson, R.; Aguilera, R.P.; Angulo, A.; Donoso, F.; Rodriguez, J. Computationally Efficient Cascaded Optimal Switching Sequence MPC for Grid-Connected Three-Level NPC Converters. IEEE Transactions on Power Electronics 2019, 34, 12464–12475. [Google Scholar] [CrossRef]

- Vazquez, S.; Acuna, P.; Aguilera, R.P.; Pou, J.; Leon, J.I.; Franquelo, L.G. DC-Link Voltage-Balancing Strategy Based on Optimal Switching Sequence Model Predictive Control for Single-Phase H-NPC Converters. IEEE Transactions on Industrial Electronics 2020, 67, 7410–7420. [Google Scholar] [CrossRef]

- Mora, A.; Cardenas, R.; Aguilera, R.P.; Angulo, A.; Lezana, P.; Lu, D.D.C. Predictive Optimal Switching Sequence Direct Power Control for Grid-Tied 3L-NPC Converters. IEEE Transactions on Industrial Electronics 2021, 68, 8561–8571. [Google Scholar] [CrossRef]

- Zheng, C.; Dragičević, T.; Zhang, Z.; Rodriguez, J.; Blaabjerg, F. Model Predictive Control of LC-Filtered Voltage Source Inverters With Optimal Switching Sequence. IEEE Transactions on Power Electronics 2021, 36, 3422–3436. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. IEEE Transactions on Industry Applications 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Wu, B.; Pontt, J.O.; Kouro, S. Multilevel Voltage-Source-Converter Topologies for Industrial Medium-Voltage Drives. IEEE Transactions on Industrial Electronics 2007, 54, 2930–2945. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A Survey on Neutral-Point-Clamped Inverters. IEEE Transactions on Industrial Electronics 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Rocha, A.V.; de Paula, H.; dos Santos, M.E.; Filho, B.J.C. Increasing long belt-conveyors availability by using fault-resilient medium voltage AC drives: Part II - Reliability and maintenance assessment. In Proceedings of the 2012 IEEE Industry Applications Society Annual Meeting; 2012; pp. 1–8. [Google Scholar]

- Akagi, H.; Watanabe, E.H.; Aredes, M. Instantaneous power theory and applications to power conditioning; Wiley, 2007; p. 379.

- Wu, B. High-Power Converters and AC Drives; Wiley-IEEE Press, 2006.

- Leon, J.I.; Kouro, S.; Franquelo, L.G.; Rodriguez, J.; Wu, B. The Essential Role and the Continuous Evolution of Modulation Techniques for Voltage-Source Inverters in the Past, Present, and Future Power Electronics. IEEE Transactions on Industrial Electronics 2016, 63, 2688–2701. [Google Scholar] [CrossRef]

- Arias-Esquivel, Y.; Cárdenas, R.; Urrutia, M.; Diaz, M.; Tarisciotti, L.; Clare, J.C. Continuous Control Set Model Predictive Control of a Modular Multilevel Converter for Drive Applications. IEEE Transactions on Industrial Electronics 2023, 70, 8723–8733. [Google Scholar] [CrossRef]

- Arias-Esquivel, Y.; Cárdenas, R.; Tarisciotti, L.; Díaz, M.; Mora, A. A Two-Step Continuous-Control-Set MPC for Modular Multilevel Converters Operating With Variable Output Voltage and Frequency. IEEE Transactions on Power Electronics 2023, 38, 12091–12103. [Google Scholar] [CrossRef]

- Süli, E.; Mayers, D. An Introduction to Numerical Analysis;; Cambridge University Press, 2003.

- Vazquez, S.; Rodriguez, J.; Rivera, M.; Franquelo, L.G.; Norambuena, M. Model Predictive Control for Power Converters and Drives: Advances and Trends. IEEE Transactions on Industrial Electronics 2017, 64, 935–947. [Google Scholar] [CrossRef]

- Quevedo, D.E.; Aguilera, R.P.; Geyer, T. Predictive Control in Power Electronics and Drives: Basic Concepts, Theory, and Methods. In Advanced and Intelligent Control in Power Electronics and Drives; Orłowska-Kowalska, T., Blaabjerg, F., Rodríguez, J., Eds.; Studies in Computational Intelligence, Springer International Publishing: Cham, 2014; pp. 181–226. [Google Scholar] [CrossRef]

- Mattavelli, P. An improved deadbeat control for UPS using disturbance observers. IEEE Transactions on Industrial Electronics 2005, 52, 206–212. [Google Scholar] [CrossRef]

- Yaramasu, V.; Wu, B. Fundamentals of Model Predictive Control. In Model Predictive Control of Wind Energy Conversion Systems; 2017; pp. 117–148. [Google Scholar] [CrossRef]

- Hackl, C. MPC with analytical solution and integral error feedback for LTI MIMO systems and its application to current control of grid-connected power converters with LCL-filter. In Proceedings of the 2015 IEEE International Symposium on Predictive Control of Electrical Drives and Power Electronics (PRECEDE); 2015; pp. 61–66. [Google Scholar] [CrossRef]

- Norambuena, M.; Lezana, P.; Rodriguez, J. A Method to Eliminate Steady-State Error of Model Predictive Control in Power Electronics. IEEE Journal of Emerging and Selected Topics in Power Electronics 2019, 7, 2525–2530. [Google Scholar] [CrossRef]

Figure 2.

Proposed control system, composed of an MPC where the load- voltage and the converter’s output current are controlled in a single-stage MPC. Notice that the common mode voltage is obtained using a second MPC algorithm.

Figure 2.

Proposed control system, composed of an MPC where the load- voltage and the converter’s output current are controlled in a single-stage MPC. Notice that the common mode voltage is obtained using a second MPC algorithm.

Figure 3.

Circuit diagram to obtain the steady-state control action.

Figure 5.

(a) HIL platform used to perform the experiments, and (b) topology of the nonlinear load.

Figure 6.

Estimated and measured current when a nonlinear load is connected. (a) -component of the load current, and (b) -component of the load current.

Figure 6.

Estimated and measured current when a nonlinear load is connected. (a) -component of the load current, and (b) -component of the load current.

Figure 7.

Steady-state results for different load conditions. (a,d,g) Load output voltage without load, with resistive load and with nonlinear load, (b,e,h) load output current without load, with resistive load and with nonlinear load, and (c,f,i) DC-link capacitor voltages without load, with a resistive linear load and nonlinear load.

Figure 7.

Steady-state results for different load conditions. (a,d,g) Load output voltage without load, with resistive load and with nonlinear load, (b,e,h) load output current without load, with resistive load and with nonlinear load, and (c,f,i) DC-link capacitor voltages without load, with a resistive linear load and nonlinear load.

Figure 8.

Harmonic spectrum of (a) load output voltage, and (b) load output current when a nonlinear load is connected.

Figure 8.

Harmonic spectrum of (a) load output voltage, and (b) load output current when a nonlinear load is connected.

Figure 10.

Transient operation of the system for a load step. (a) Load output voltage, and (b) Filter inductor current.

Figure 10.

Transient operation of the system for a load step. (a) Load output voltage, and (b) Filter inductor current.

Table 1.

System Parameters.

| Parameter | Value |

|---|---|

| Switching and Sampling frequency | = 20 [kHz] |

| DC-link voltage | = 700 V |

| LC Filter | = 1 m = 2.4 mH = 15 F |

| Load resistance | = 30 |

| Non-linear load | = 1.8 mH = 2.2 mF = 60 |

| Filter current weight factor | = 0.25 |

| Load voltage weight factor | |

| Control effort weight factor |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Copyright: This open access article is published under a Creative Commons CC BY 4.0 license, which permit the free download, distribution, and reuse, provided that the author and preprint are cited in any reuse.

An Optimal Switching Sequence Model Predictive Control Scheme for the 3L-NPC with Output LC Filter

Felipe Herrera

et al.

,

2023

Microgrids Power Quality Enhancement Using Model Predictive Control

Félix Garcia-Torres

et al.

,

2021

MDPI Initiatives

Important Links

© 2024 MDPI (Basel, Switzerland) unless otherwise stated